锁存器和寄存器介绍

描述

锁存器和寄存器

寄存器主要由触发器和一些控制门组成,每个触发器能存放一位 二进制码,存放N位数码,就应该有N位触发器。为保持触发器能正常完成寄存器的功能,还必须用适当的门电路组成控制电路。

锁存器是由电平触发器完成的,N个电平触发器的时钟端连在一起,在时钟脉冲作用下能接收N位二进制信息。

从寄存器数据角度看,锁存器和寄存器的功能是一样的,其区别仅在于锁存器是用电平触发的,而寄存器是用边沿触发器触发的,即寄存器的输出端平时不随输入端的变化而变化,只有在时钟有效时,才将输入端的数据送到输出端;而锁存器的输出端平时总随输入端变化而变化。

寄存器是在时钟沿进行数据的锁存,而锁存器是用电平使能来锁存数据。所以寄存器的Q输出端在每个时钟沿都会被更新,而锁存器仅在使能电平有效时才被更新。在FPGA设计中建议如果不是强制需求锁存器,则应该尽量使用寄存器。

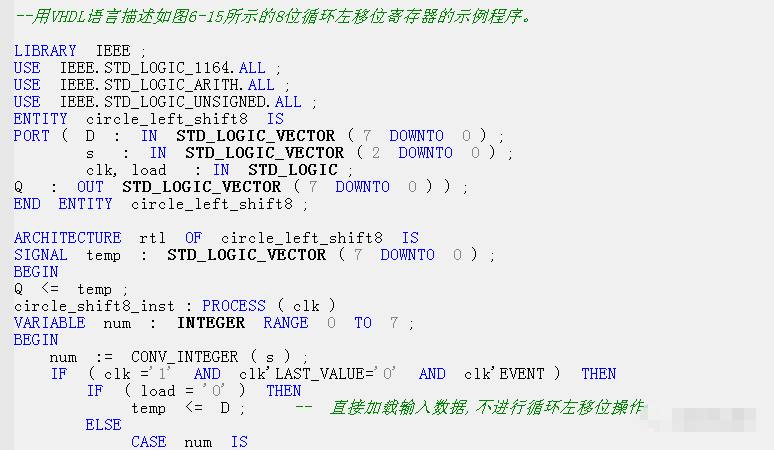

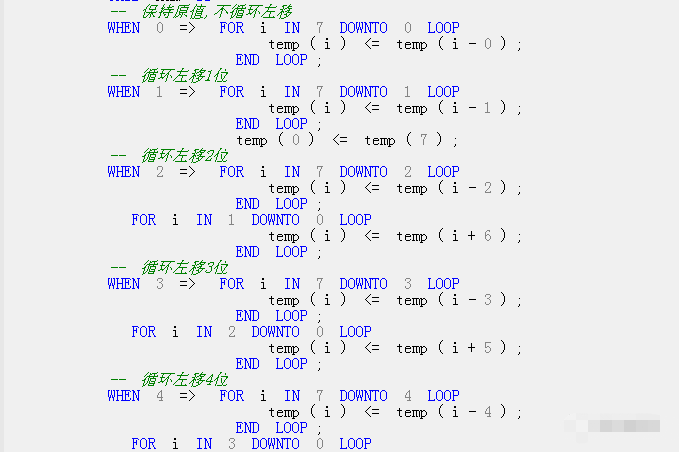

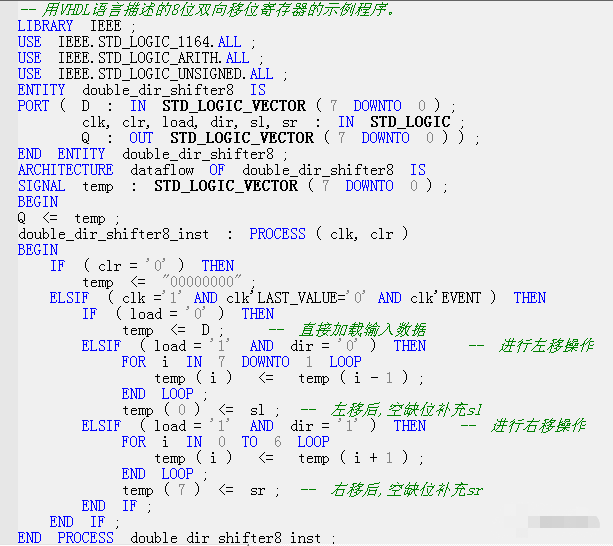

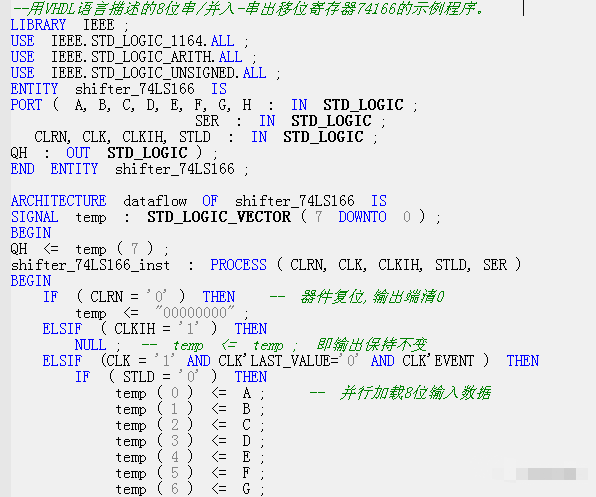

寄存器按功能可以分为两类,即基本寄存器和移位寄存器。基本寄存器的数据只能并行的输入或输出;移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入并行输出,也可以并行输入串行输出、串行输入串行输出、串行输入并行输出,因其数据输入输出方式非常灵活,所以用途非常广泛。

锁存器

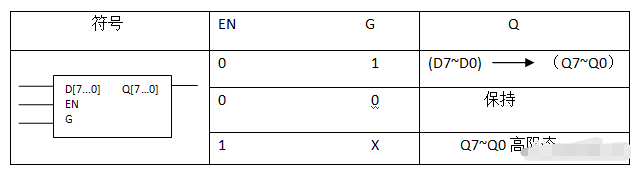

锁存器通常由D触发器构成,在数字电路中,74373是一种常用的8位锁存器,它由使能控制端EN、数据锁存控制端G、数据输入端D7~D0和数据输出端Q7~Q0构成,其逻辑符号与其真值表如下;

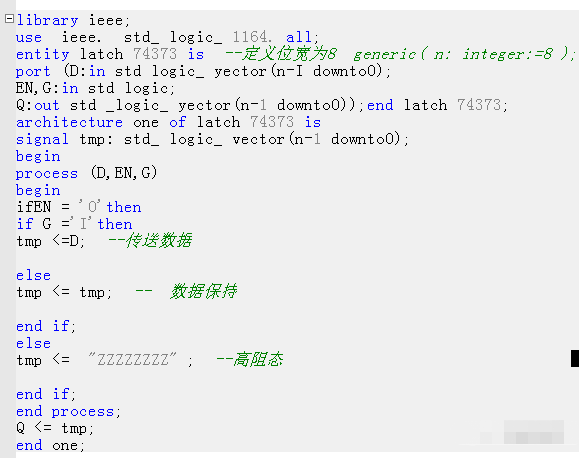

例6-13] 74373锁存器的VHDL描述。

分析:通过74373 锁存器的真值表可以看出,当数据锁存控制端G=1且使能控制端EN=0时,锁存器把输入端口D的数据送到输出端口; 当数据锁存控制端G=0且使能控制端EN =0时,锁存器输出端口将保持前一个状态;当使能控制端EN=1时,不管数据锁存控制端G的状态如何,这时锁存器输出端口将处于高阻态。编写74373锁存器的VHDL程序时,需先使用IF语句判断EN是否等于见 若是,再使用IF语句判断G是否等于1,如果G等于1,则将D输入到Q中,否则Q保持前一状态;当EN=0时,则Q输出为高阻态。74373 锁存器的VHDL程序编写如下:

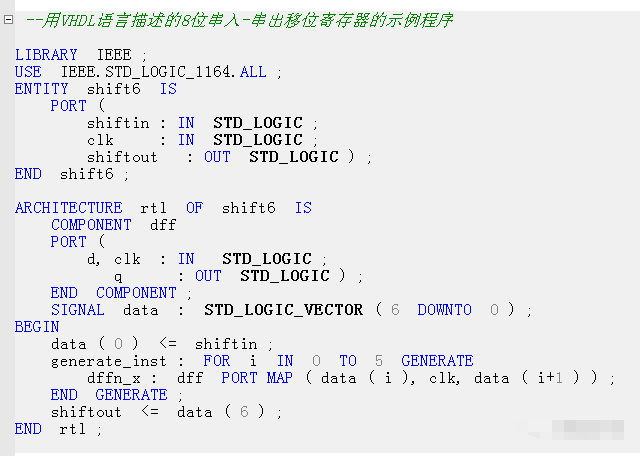

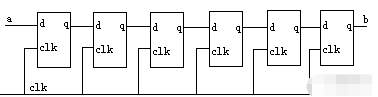

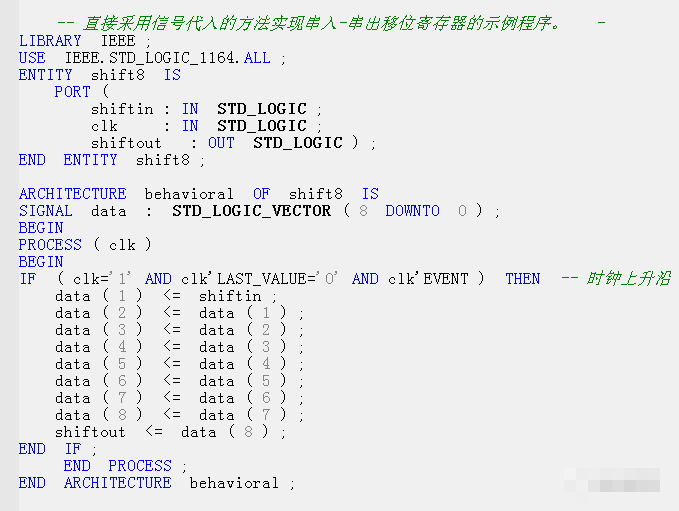

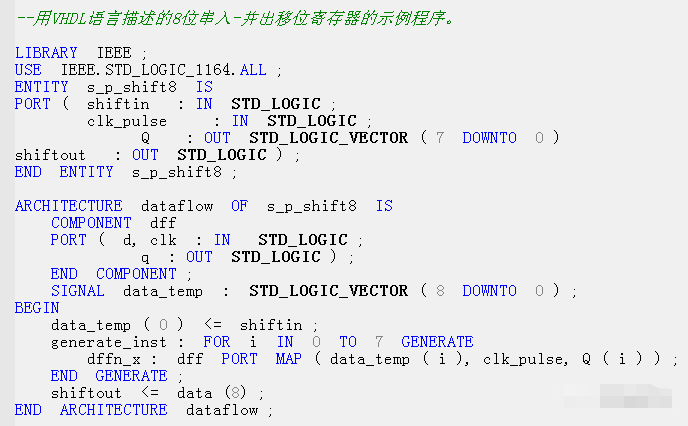

6位串入串出移位寄存器的结构化描述

-

锁存器、触发器和寄存器的区别2024-05-23 4251

-

具有3态输出的8位锁存寄存器收发数据表2024-05-13 347

-

什么是锁存器 与寄存器有何区别2023-04-09 11457

-

寄存器的工作原理2023-02-20 9933

-

一文详细区分寄存器、锁存器和触发器2023-01-30 3751

-

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述2022-12-19 14611

-

如何使用锁存器的Time Borrowing技术来替代关键路径中的寄存器2022-06-14 2610

-

如何在项目中使用移位寄存器2019-07-15 2010

-

【转】数字电路三剑客:锁存器、触发器和寄存器2018-10-27 2742

-

触发器、锁存器、寄存器三者的区别2018-09-11 6199

-

寄存器、锁存器和触发器的区别2018-07-03 4020

-

74LS595-8位输出锁存移位寄存器2016-01-12 1279

-

锁存器、触发器、寄存器和缓冲器的区别2011-10-09 9361

全部0条评论

快来发表一下你的评论吧 !