BUCK开关振铃的原因与优化方法

描述

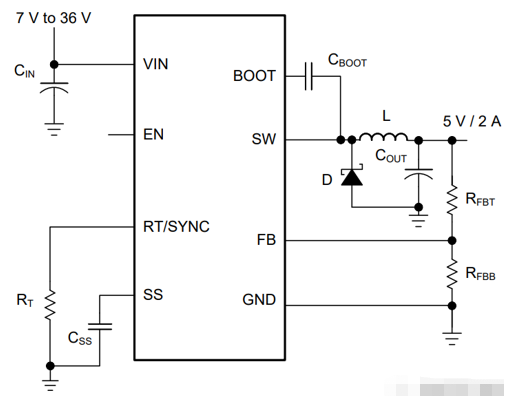

LMR14020是一款40V/2A在工业领域非常popular的buck芯片,下面是他的推荐电路。

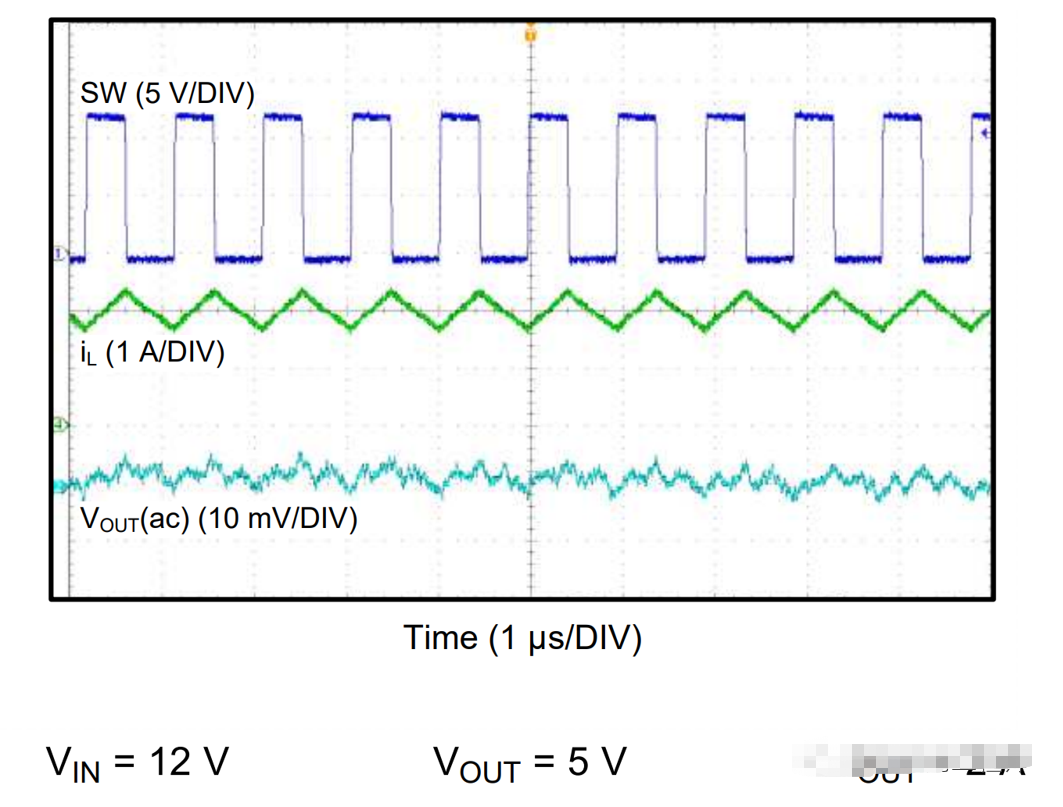

你有看过BUCK关键引脚的波形么? CCM下正常的SW波形如下图方波。

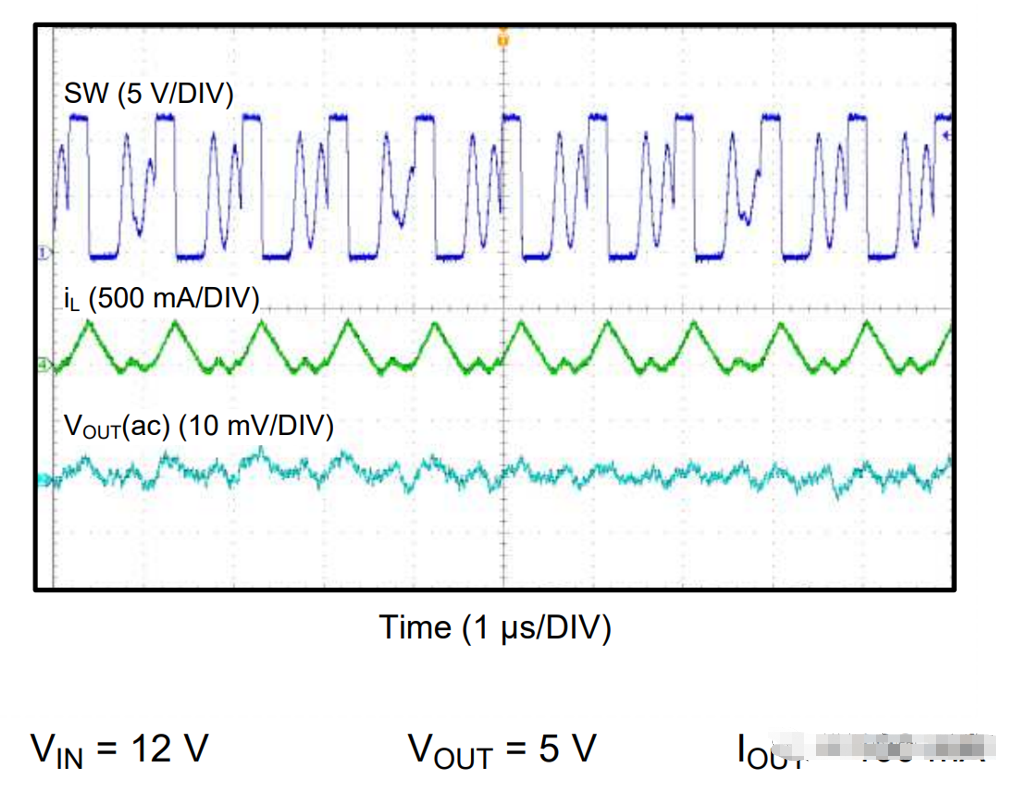

而DCM模式下的SW波形在断续模式下,上管下管都不导通,输出LC能量谐振,这个时候的震荡是正常的。

一、什么是开关振铃?

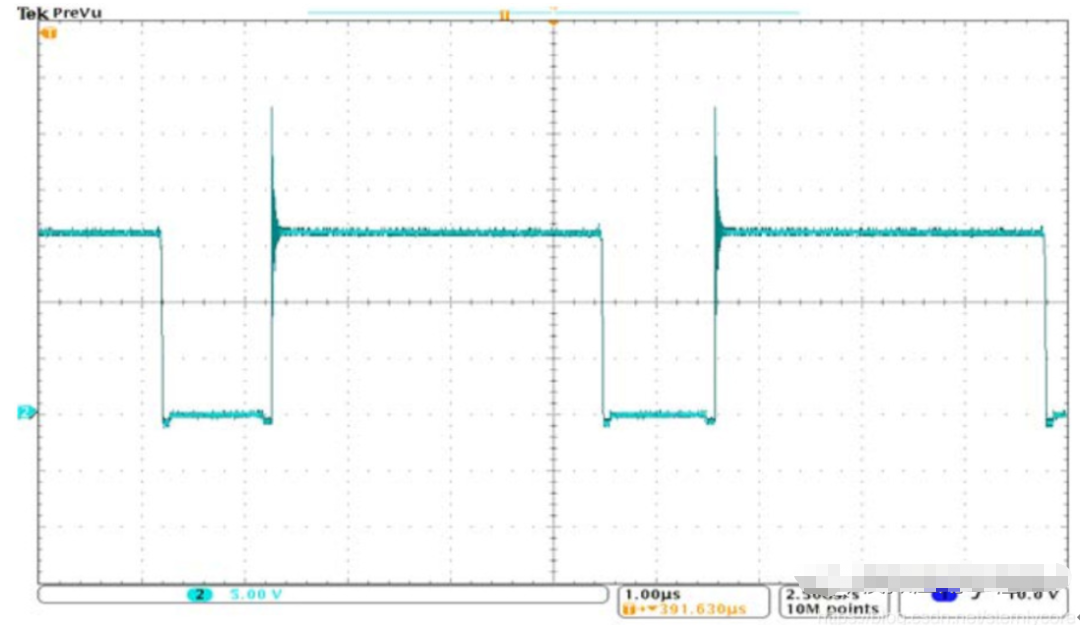

由于寄生参数的存在,开关电源电路在开关动作瞬间会产生开关振铃。SW波形在上管导通瞬间,SW电压过冲超过VIN 10V。

振铃的存在,可 能使得开关管承受的电压超过其耐压值而发生击穿;另一方面,开关振铃为远超开关频率的高频振铃, 并伴随很高的 dV/dt,会带来传导和辐射的 EMI 问题,可能会使得终端产品不能通过 EMI 标准测试, 更严重时甚至会干扰开关电源自身的信号电路或临近的其他功能电路的正常工作。所以尽可能地抑制 开关振铃是开关电源设计中一个很重要的环节。

二、振铃的原因?

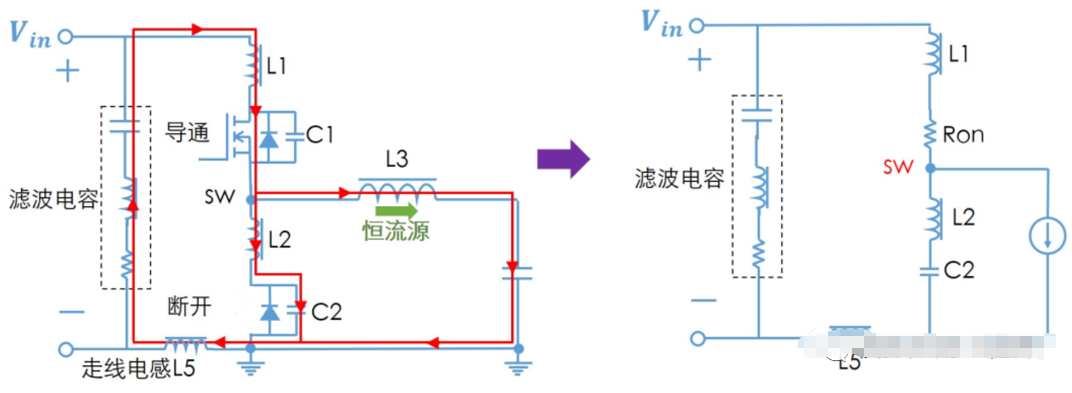

虽然MOS管模型通常都有Lg,Ld,Ls,即管子三个引脚的寄生电感,但通常MOS集成在芯片内部,因此振铃的主要原因都来自layout走线过长导致的寄生电感与下管结电容谐振导致SW点电压的震荡。

看上图,其中,L1、L2为走线与MOS管寄生电感之和。在上管导通瞬间,正在导通的下管突然被加上反向电压,在瞬间会产生非常大的反向恢复电流,即从SW到GND会产生很大的di/dt,通过寄生电感L2在SW节点会产生很高的电压幅值。之后L1、L2与下管结电容C产生谐振,进而引发振铃现象,其本质是LCR阻尼振荡。

从以上分析可推断出,寄生电感L1比较大,那么产生的尖峰电压肯定是越大的;负载电流越大,那么意味着功率电感电流越大,在SW从0上升到Vin电压时,寄生电感L1得到的电流也越大,L1获得的用于振荡的能量也是越大的,振荡尖峰越高;开关速度越快,寄生电感电流上升的速度也越快,在SW从0上升到Vin电压时,寄生电感L1得到的电流也越大,参与振荡的能量也越多,所以尖峰也越高。

三、 如何优化振铃现象

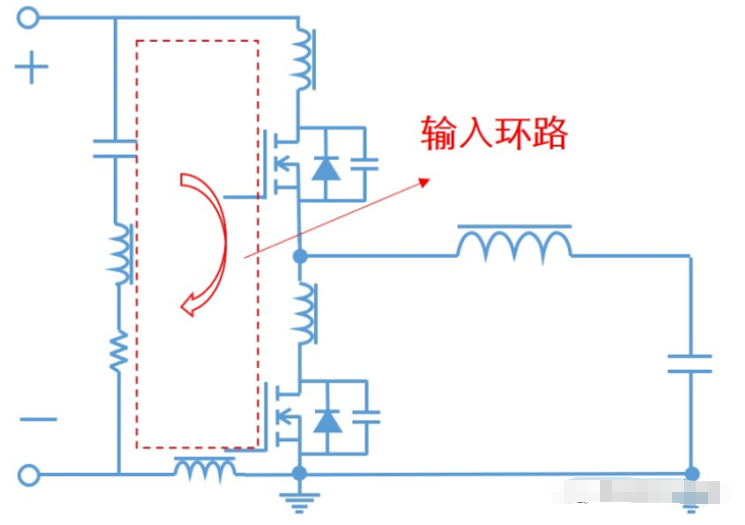

1. 输入滤波电容的位置尽可能的靠近芯片供电引脚,以减小输入回路面积。

2. 优化PCB Layout降低走线电感量。

1盎司铜厚,线宽50mil,走线长度10mm的电感量是6.52nH,而通过仿真测试看到,在VIN=12V,VOUT=3.3V,IOUT=6.6A 时,设置上管走线电感0.5nH,可引起SW 超过VIN 4V 的电压尖峰!基本优秀的Layout 会极大减小SW的过冲电压。

3. 可以通过从SW连接到BOOT引脚的外置RC控制开关速度,减小di/dt从而减小谐振峰值电压

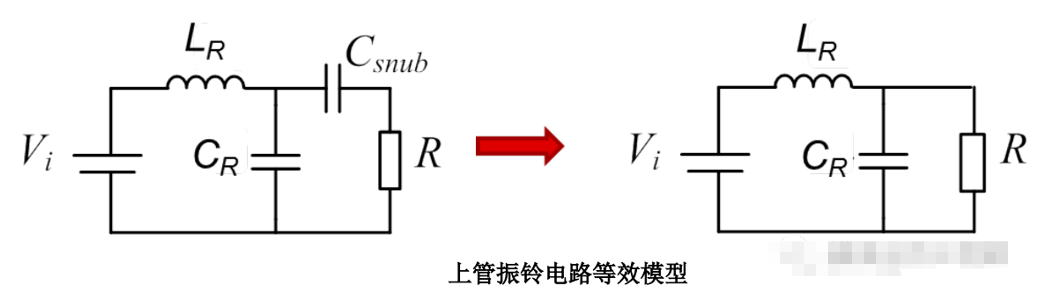

4. SW对地添加snubber电路吸收:R Csnub放置在SW节点与GND之间。

电容越大,抑制振铃振幅效果越好。而且当电容达到一定程度大小以后,电容的增加给振铃抑制的效果并不显著,并且Csnub越大也会带来损耗的问题,效率会变差。一般工程经验取值范围:(R:5~10ohm,C:1nF~10nF) 。

四、Snubber快捷设计方法分享

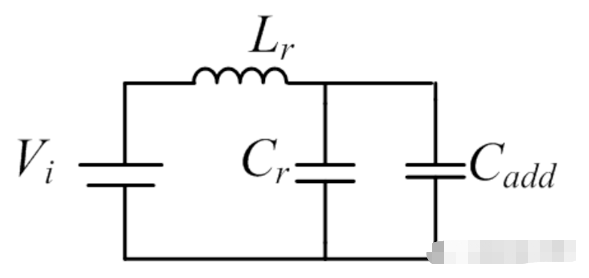

(上图Csnub阻抗小,被进一步简化)

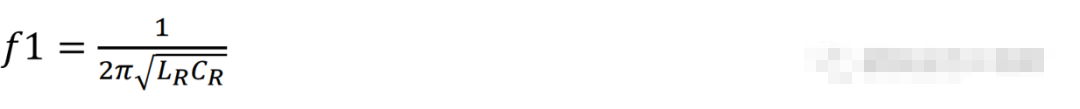

第一步,需要确定图上图中的 LR和 CR。首先测量初始振铃频率。

然后在 snubber 将要放置的位置上,放置一个 Cadd,因此新的可测得的振铃频率表达式 为

以上两式中,仅 LR和 CR为未知量,故可通过两式联立,解得 LR和 CR.

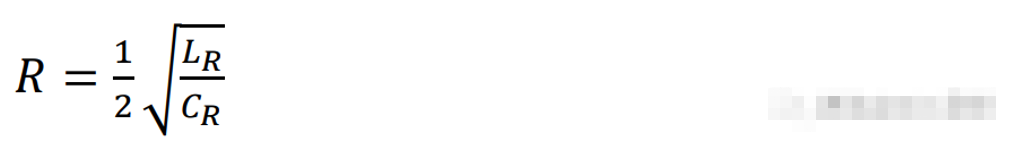

第二步,选取合适的 R 值,使得 R 值近似于

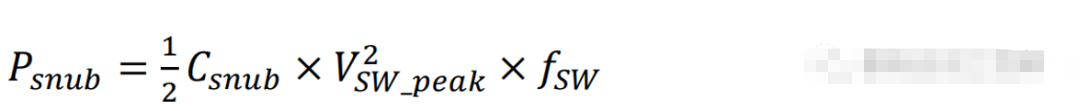

注意,电阻的封装应考虑散热。使得电阻功率等级大于电阻上损耗。电阻损耗表达式为

第三步,选择合适的电容值 Csnub。如前文所说,电容值的选择是振幅抑制和控制损耗的折中。可选择以下式作为起点,根据损耗情况和振幅抑制效果,进行进一步的调整:增大电容抑制振幅,减小电容提高效率。

-

如何调整BUCK电路的占空比 BUCK电路占空比优化技巧2024-12-12 3333

-

buck电路效率优化方法2024-11-04 7348

-

什么是开关振铃?振铃的原因?如何优化振铃现象?2024-02-17 22071

-

Buck电源的SW振铃产生原因是什么?如何抑制呢?2023-12-28 15980

-

四开关BUCK-BOOST的无缝切换控制方法2023-03-20 14242

-

BUCK型DC-DC芯片的抗振铃电路2022-05-09 1254

-

优化开关频率振点的方式2021-11-17 991

-

降低开关电路振铃现象的缓冲器设计方法2021-10-22 627

-

一种新颖的BUCK型DC—DC芯片的抗振铃电路2021-09-18 1014

-

如何实现Buck电路的软开关详细方法说明2019-07-11 9020

-

开关节点的振铃2018-12-03 3403

-

振铃产生的原因介绍2018-08-17 10443

-

图像处理振铃效应原理_图像处理中振铃现象2018-05-14 21285

-

开关电源的振铃与抑制2017-09-15 1665

全部0条评论

快来发表一下你的评论吧 !