Zynq及Vitis HLS助力面向声音合成和声学控制的低时延技术

描述

从音频输入到输出,现有的实时数字音频系统很难实现低于 1ms 的时延。实际上,200µs 是到目前为止可实现的最佳时延。INSA(法国)的 Emeraude 研究团队正在开发 Syfala 编译器,该编译器结合了 Faust (一种用于实时音频 DSP 的领域特定语言)和 AMD Vitis HLS,使其为音频 DSP 用户提供非常高级的音频合成工具。

Emeraude 采用基于 AMD Zynq 的FPGA 板卡、低时延音频编解码器和 Syfala 编译器,在众多简单的 DSP 程序上实现了 11µs 的低时延。这项新技术适用于声音合成和主动声学控制。

01

项目挑战

实时音频数字信号处理( DSP )已经在广泛的计算机架构上实现:采用冯・诺依曼架构的 CPU、多核 CPU、GPU、专用电路、FPGA 等。然而,实现超低时延(即小于 1ms)的唯一方法是使用专用电路,如 ASIC 或 FPGA。

尽管如此,对于 DSP 程序员而言,使用 FPGA 几乎是不可能的事情,因为他们没有掌握硬件设计技能。

因此,该项目的主要挑战在于设计出一款工具,允许音频 DSP 程序员以极低时延(即小于 100µs)在 FPGA 上实现任意音频 DSP 算法。

02

解决方案

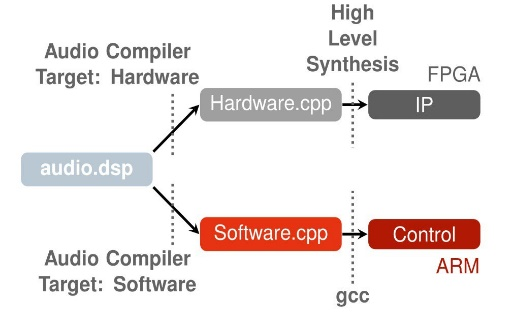

采用的解决方案是将音频 DSP 语言编译器(即 Faust)的输出与 HLS 工具 Vitis HLS连接起来。Faust 编译器不仅可处理软硬件分区,而且还可隔离将在 FPGA 上实施的内核 DSP 算法,如图 1 所示。

图 1:从 Faust 程序到 FPGA 的 Syfala 编译流程

Vitis HLS 用于实现该内核 DSP 的硬件,允许访问外部 DDR 内存以及使用 ARM Zynq 处理系统驱动程序的硬件控制器。

INSA-LYON 的研究团队主管 Tanguy Risset 表示:“Vitis HLS 允许我们直接重复使用 Faust 编译器生成的 C++ 代码,因此从 Faust 高级规范直至 FPGA 比特流都无需经历手动设计流程。此外,Vitis HLS 与 AMD 的设计流程能够很好地集成在一起,方便我们进行硬件/软件的协同设计。”

03

设计成效

最终成效就是获得一个新的编译流程,可将任意音频 DSP 程序自动编译到基于 AMD Zynq 7000 的 FPGA 板卡(如 Digilent Zybo 或 Genesys)上。这样一来,从模拟输入到模拟输出,所实现的程序的时延可低至 11µs。如此短的时延是前所未有的。该编译器是开源的,目前用于实现主动声学控制算法和 3D 音频编解码流程。

Risset 补充道:“Vitis HLS 使我们能够精确控制 IP 的时延。特别是 Vitis HLS 能够生成一个有一个样本延迟时延的 IP。这对于实现我们在模拟与模拟之间实现的时延极为重要。”

Risset 表示,Vitis HLS IP 的调度视图有助于我们了解 Vitis HLS 是如何引导并行化,以及内存访问是如何对 IP 时延产生影响的。他补充道:“这促使我们在 Faust 生成的 C++ 代码中对内存访问进行优化,这是实现低时延的必要步骤。”

审核编辑:刘清

-

使用AMD Vitis Unified IDE创建HLS组件2025-06-20 2057

-

如何使用AMD Vitis HLS创建HLS IP2025-06-13 1422

-

Vitis HLS移植指南2023-09-13 500

-

如何在Vitis HLS GUI中使用库函数?2023-08-16 2114

-

AMD全新Vitis HLS资源现已推出2023-04-23 1725

-

理解Vitis HLS默认行为2022-11-24 2398

-

使用Vitis HLS创建属于自己的IP相关资料分享2022-09-09 5456

-

FPGA高层次综合HLS之Vitis HLS知识库简析2022-09-07 3706

-

Vitis HLS知识库总结2022-09-02 4604

-

Vitis HLS前端现已全面开源2022-08-03 1600

-

Vitis HLS工具简介及设计流程2022-05-25 3445

-

基于Vitis HLS的加速图像处理2022-02-16 3234

-

Vivado HLS和Vitis HLS 两者之间有什么区别2020-11-05 40959

-

音箱,音响技术和声学原理是什么?2010-04-03 4252

全部0条评论

快来发表一下你的评论吧 !