RA2快速设计指南 [11] 外部总线、SDADC24和OPAMP

描述

13. 外部总线

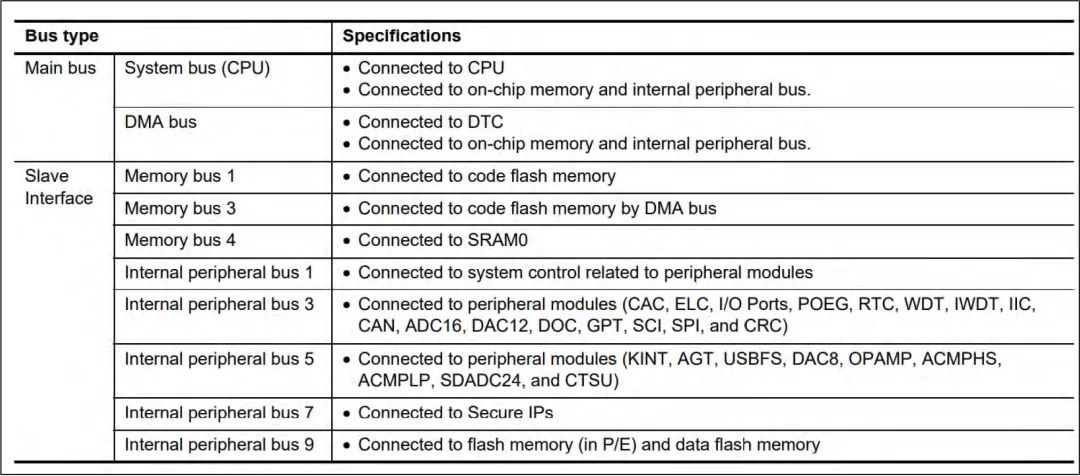

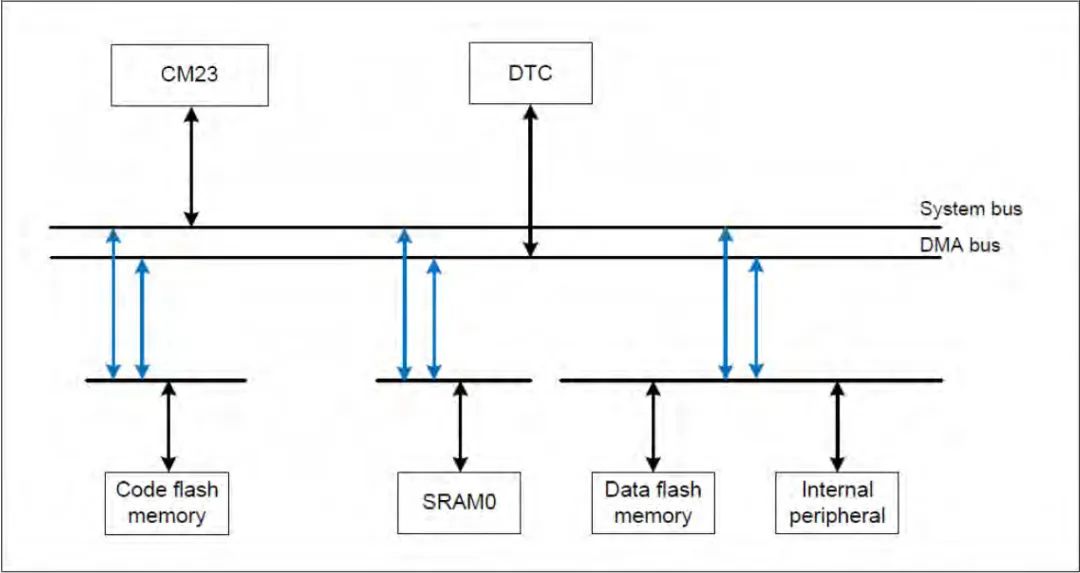

RA2产品有总线主控和总线受控接口。图27列出了总线主控和总线受控接口,图28给出了总线配置。

注:存储器空间必须采用小端法才能在Arm Cortex-M内核上执行代码。

图27. RA2A1总线规格

图28. RA2总线配置

13.1 总线错误的监视

总线错误监视系统监视每个单独的区域,当检测到错误发生时,会通过AHB-Lite错误响应协议将错误返回给发请求的主IP。

13.1.1 总线错误类型

每条总线上都可能发生以下类型的错误

• 非法地址访问

• 总线主MPU错误

• 总线从MPU错误

• 超时

13.1.2 发生总线错误时的处理

发生总线错误时,无法保证正常运行,并且会将错误返回到发出请求的主IP。每个主器件发生的总线错误均存储在BUSnERRADD和BUSnERRSTAT寄存器中。只能通过复位来清空这些寄存器。有关更多信息,请参见《硬件手册》的“总线错误地址寄存器(BUSnERRADD)”和“总线错误状态寄存器 (BUSnERRSTAT)”部分。

注:DTC不会收到总线错误,因此它们的运行不受总线错误的影响。

14. 24位Sigma-Delta A/D转换器

(SDADC24)

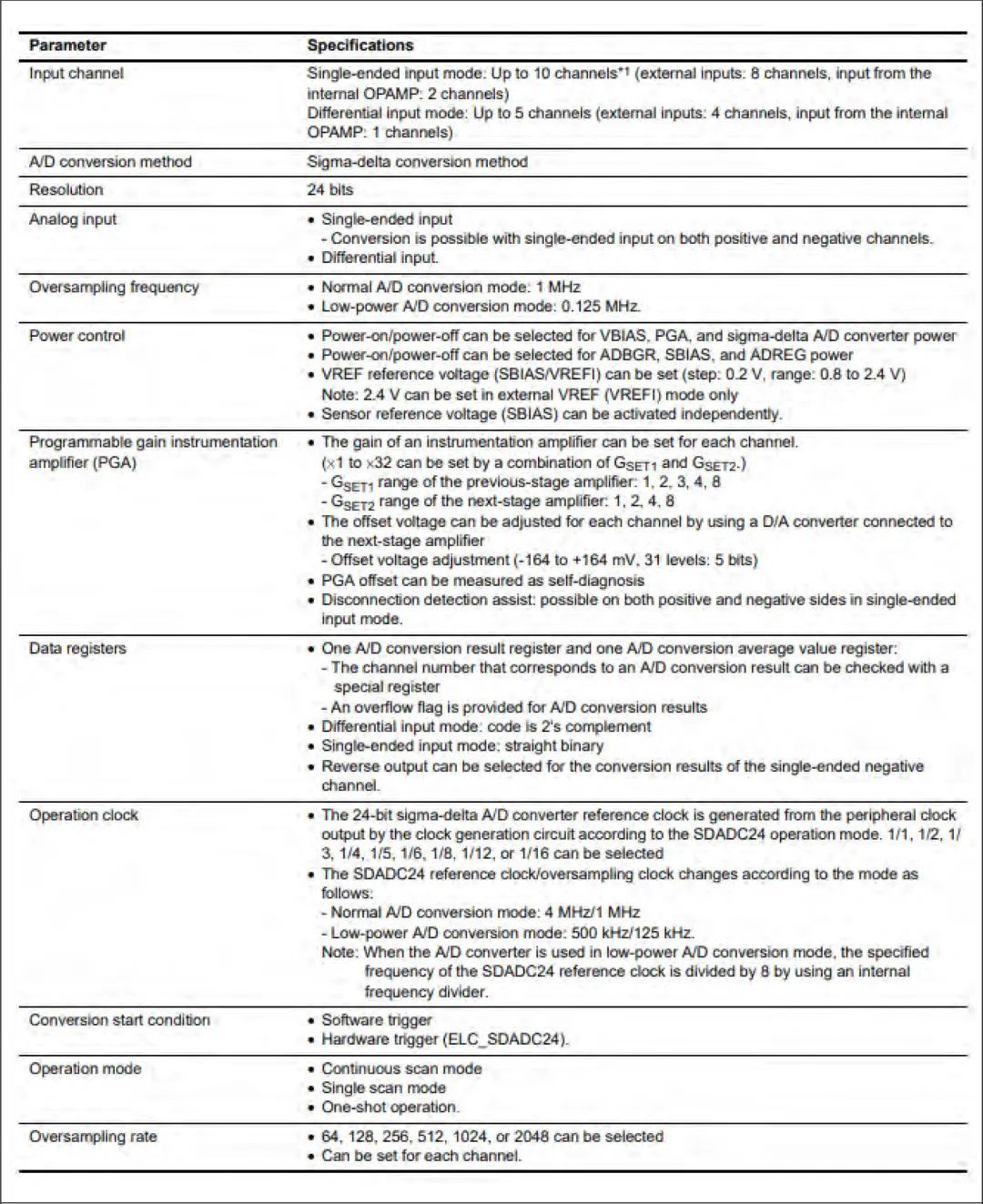

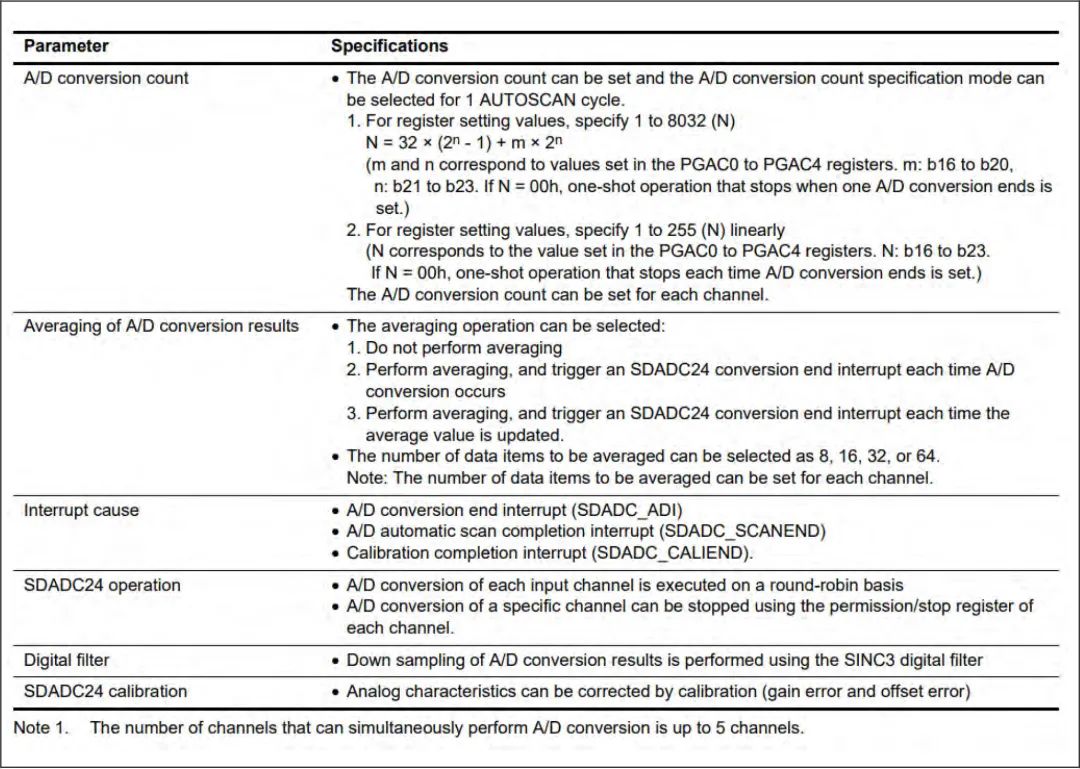

RA2A1 MCU具有一个24位Sigma-Delta ADC。RA2A1为RA2产品中唯一一种包含SDADC的产品。图29与图30显示了SDADC24转换器的规格。具体请参照《RA2A1 MCU硬件手册》中“24位Sigma-Delta转换器(SDADC24)”章节的内容。

图29. SDADC24的规格(1/2)

图30. SDADC24的规格(2/2)

15. 可配置开关的运算放大器

(OPAMP)

RA2A1产品具有运算放大器(OPAMP),可用于将较小的模拟输入电压放大并输出放大后的电压。它共有三个差分运算放大器单元,每个单元都有两个输入引脚和一个输出引脚。

运算放大器具有以下功能:

• OPAMP0和OPAMP1可用来将信号输入到低功耗模拟比较器(ACMPLP)和24位Sigma-Delta A/D转换器(SDADC24)中。

• 支持高速模式(大电流消耗)、中速模式(中电流消耗)、低功耗模式(慢速响应)。选择模式时需要权衡响应速度与电流消耗之间的关系。

• 可通过异步通用定时器(AGT)的触发器启动运行。

• 可通过16位A/D转换结束触发器来停止运行。

• 每个单元都有用来选择输入信号的开关。此外,OPAMP0还有一个可以选择输出引脚的开关。

• OPAMP的输出可以不通过开关而直接从AMP0O输出到AMP2O引脚。

• 所有OPAMP单元的I/O信号都可用于ADC16的输入信号。

• DAC8和DAC12的输出信号可作为每个OPAMP的正输入信号。

• 电压跟随电路可以通过连接一个OPAMP的输出信号到该OPAMP的负输入信号进行配置。

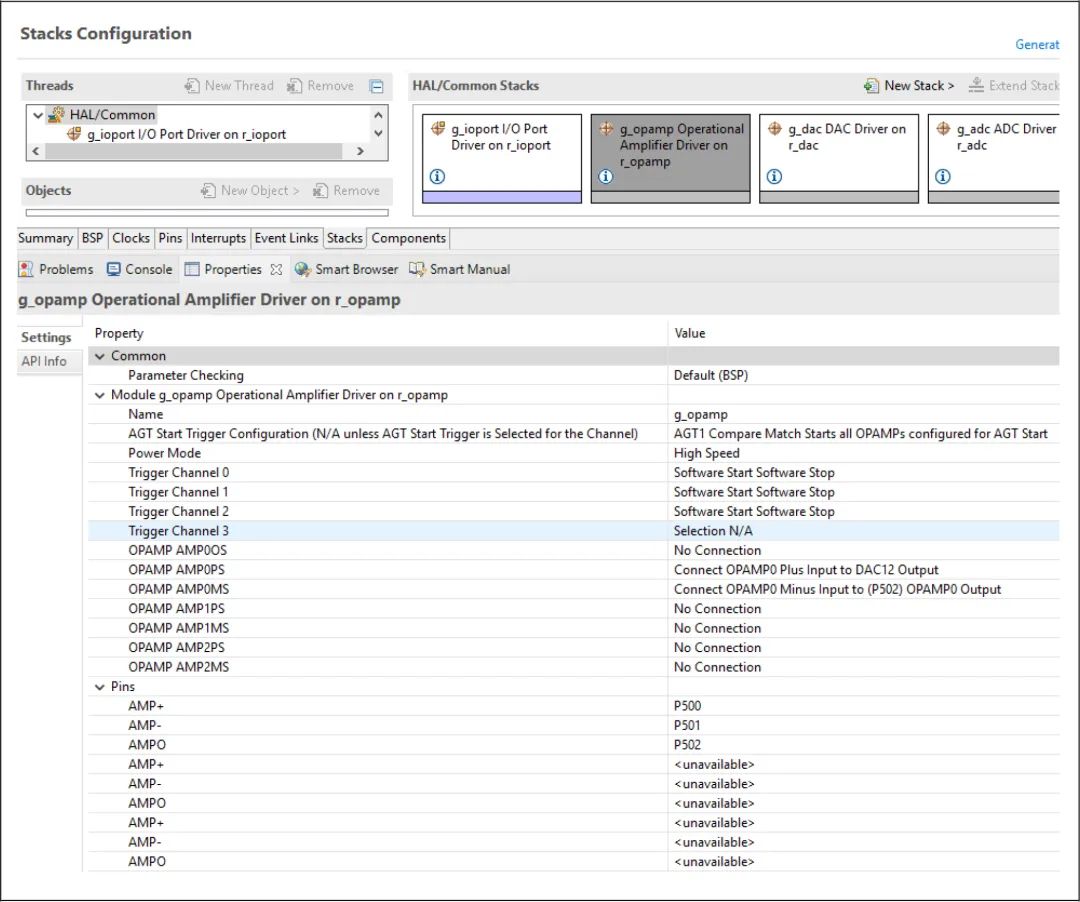

Renesas FSP具有用来设置OPAMP以及引脚连接等的运算放大器驱动器和驱动器配置器。在图31的示例中,通过设置OPAMP0实现了一个分别由P500、P501、P502作为正输入引脚、负输入引脚、输出引脚的电压跟随器。该示例还设置了正输入,在内部实现了DAC12的输出。

图31. 使用Renesas FSP配置器设置RA2A1 OPAMP的示例

在Renesas FSP配置器中设置完OPAMP后,您可以使用OPAMP驱动程序的API(如R_OPAMP_Open、R_OPAMP_Start)来初始化并启动OPAMP的运行。请参考《RA2A1 MCU硬件手册》和《FSP用户手册》中的“运放(OPAMP)”章节了解更多内容。

-

RA2快速设计指南 [3] 时钟电路2023-10-24 1505

-

RA2快速设计指南 [6] 存储器2023-04-06 2113

-

RA2快速设计指南 [4] 时钟电路(下)2023-03-29 1650

-

RA2快速设计指南 [3] 时钟电路(上)2023-03-26 1801

-

RA2 MCU ADC转换时间测试方法2023-02-08 2563

-

EK-RA2E2-快速入门指南2023-01-30 533

-

FPB-RA2E2-快速入门指南2023-01-11 494

全部0条评论

快来发表一下你的评论吧 !