FPGA原型验证系统的时钟门控

电子说

描述

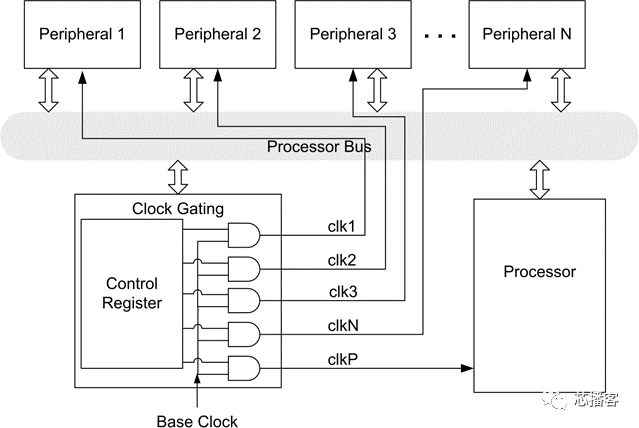

门控时钟是一种在系统不需要动作时,关闭特定块的时钟的方法,目前很多低功耗SoC设计都将其用作节省动态功率的有效技术。在SoC设计中,时钟门控可以在两个级别完成:

1. 门控时钟被设计到SoC架构中,并被编码为RTL功能的一部分。当这些相关的模块处于非激活状态时,它会停止各个模块的时钟,从而有效地禁用这些块的所有功能。由于大的逻辑块在这些非激活的时钟周期内都不进行切换和运算操作,因此节省了大量的动态功率。时钟门控的最简单和最常见的形式是使用逻辑“与”功能通过控制信号enable选择性地禁用各个块的时钟。

2. 在综合期间,相关工具自动识别共享公共使能控制信号的触发器组,并使用它们选择性地关闭这些触发器组的时钟。

这两种时钟门控方法最终都将在控制其下游时钟的时钟路径中引入具体物理逻辑门。即使映射到SoC中,这些逻辑门也可能会引入额外的时钟偏差,并导致设置和保持时间冲突,然而,这可以通过SoC后端STA流程或者其他手段的时钟树综合和布局工具来补偿。SoC设计的时钟树综合平衡了源和目的地之间的时钟缓冲、分段和布线,以确保定时关闭,使这些路径包括时钟门控。这在FPGA技术中是不可能的,因此如果SoC设计包含大量门控时钟或复杂的时钟网络,则需要其他一些方法来映射SoC设计。

所有FPGA设备都有专用的低偏斜时钟树网络,称为全局时钟。它们的数量有限,但它们可以计时FPGA中的顺序资源,频率为数百兆赫。由于FPGA供应商的精湛设计技术,时钟网络在FPGA中的任意两个目的地之间也只有几十皮秒的偏差。因此,当我们将设计目标定为FPGA时,始终建议使用这些全局时钟。然而,FPGA时钟资源不适合创建大量相对较小的时钟域,如我们通常在SoC中发现的那样。相反,FPGA更适合于实现少量的大型同步时钟网络,这些网络可以被认为是整个设备的全局网络。

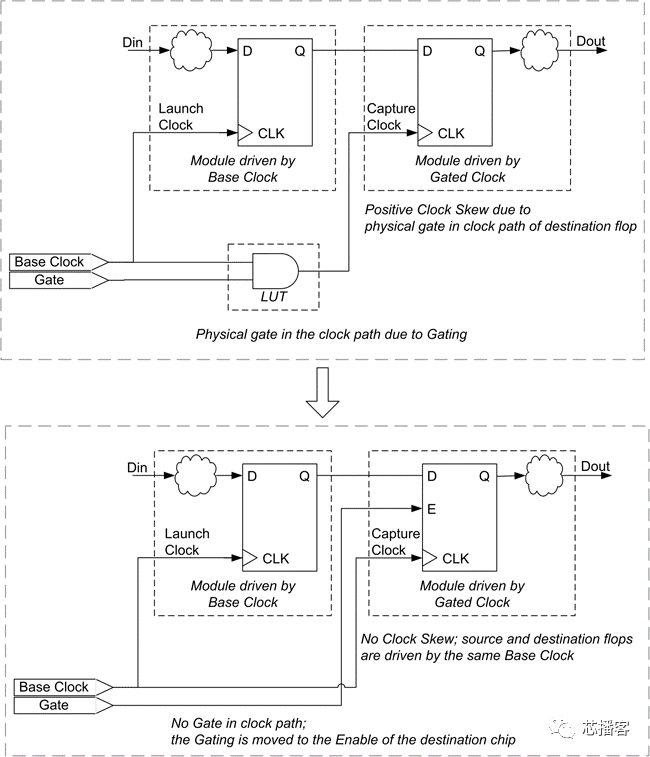

全局时钟网络非常有用,但可能不够灵活,无法满足复杂SoC设计的时钟需求,尤其是在RTL中执行时钟门控时。这是因为物理门被时钟门控过程引入时钟路径,并且全局时钟线不能自然地容纳这些物理门。因此,布局布线工具将被迫为具有插入门的时钟网络使用其他片上路由资源,通常导致到目标寄存器的不同路径之间的大的时钟偏移。

当在SoC中采用架构级时钟门控时,例如当为时钟使用粗粒度开关控制以减少动态功耗时,可能会出现这种情况。在这些情况下,可以将门控时钟的所有负载划分到同一FPGA中,并从同一时钟驱动器块驱动它们。在一些SoC设计中,设计中也可能存在跨时钟域的设计,即源和目标触发器由不同相关时钟驱动的路径,例如,时钟和由时钟路径中的物理门创建的导出门控时钟,如图所示。来自源触发器的数据很可能比门控时钟更快/更晚到达目的地触发器,并且这种竞争条件可能导致定时冲突。

上述竞争条件的解决方案是将基准时钟和选通与选通时钟分开。然后将分离的基本时钟路由到时钟,并选通到时钟使能所有顺序元件。当时钟“打开”时,顺序元件将被启用,当时钟“关闭”时,序列元件将被禁用。通常,许多门控时钟来自同一基准时钟,因此将门控与时钟分离允许单个全局时钟线用于许多门控时钟。这样,功能时钟路径中存在的逻辑门被移动到数据路径中,这消除了时钟偏移。

这个过程称为门控时钟转换。FPGA中的所有顺序元件都有专用的时钟使能输入,因此在大多数情况下,门控时钟转换可以使用这一点,而不需要任何额外的FPGA资源。然而,手动将门控时钟转换为等效启用是一个困难且容易出错的过程,尽管如果SoC设计中的时钟门控都在设计层次结构中的同一位置执行,而不是分散在各个子功能中,则可能会稍微容易一些。

顶层的芯片支持块可以包括驱动整个SoC所需的所有时钟生成和时钟门控。然后,在原型设计期间,可以用其FPGA等效逻辑替换该Chip Support模块。同时,我们可以手动将时钟门替换为启用信号,该启用信号可以在整个设备中路由。

然后,这将在原始门控时钟每次上升时仅启用全局时钟的单个边缘。在大多数情况下,由于复杂性,手动操作是不可能的,例如,如果时钟在RTL中的许多不同的始终或过程块处被本地门控。在这种情况下,可能是大多数设计流程中的默认情况,可以采用自动门控时钟转换。

审核编辑:刘清

-

什么是FPGA原型验证?FPGA原型设计的好处是什么?2024-01-12 2399

-

浅析FPGA原型验证系统的时钟资源2023-05-23 1549

-

多台FPGA原型验证平台系统如何实现自由互连2023-04-11 1044

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 2862

-

FPGA原型验证系统的时钟资源设计2023-04-07 1918

-

如何建立适合团队的FPGA原型验证系统平台与技术?2023-04-03 2277

-

验证中的FPGA原型验证 FPGA原型设计面临的挑战是什么?2022-07-19 2507

-

门控时钟实现低功耗的原理2022-07-03 3366

-

什么是门控时钟 门控时钟降低功耗的原理2021-09-23 15900

-

ASIC设计-FPGA原型验证2020-03-19 2645

-

高频RFID芯片的FPGA原型验证平台设计及验证2019-05-29 2847

-

FPGA的时钟门控是好还是坏?2019-02-21 5921

-

门控时钟2016-05-10 846

-

基于FPGA原型的GPS基带验证系统设计与实现2010-11-11 574

全部0条评论

快来发表一下你的评论吧 !