跨时钟域电路设计:单周期脉冲信号如何跨时钟域

描述

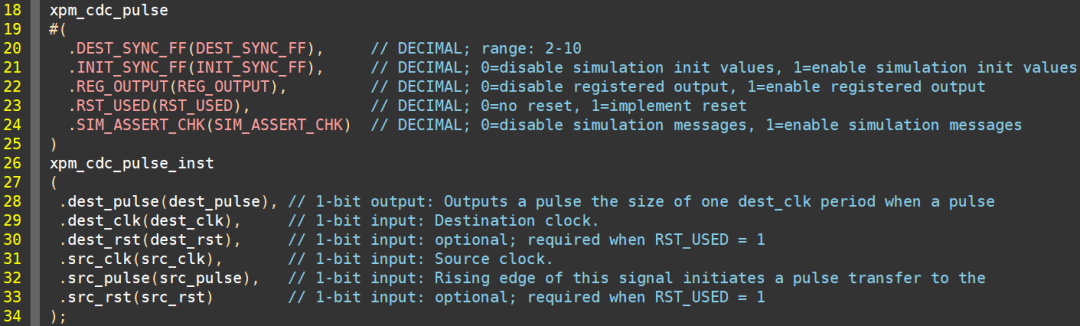

对于脉冲信号跨时钟域,XPM_CDC提供了模块xpm_cdc_pulse,如下图所示。该模块有5个参数,其中参数DEST_SYNC_FF用于确定级联触发器的个数;INIT_SYNC_FF用于确定仿真时是否使用触发器初始值;

参数REG_OUTPUT用于确定是否对最终输出信号寄存;参数RST_USED用于确定是否使用复位信号;参数SIM_ASSERT_CHK则用于确定是否显示仿真信息。从输入/输出端口来看,源端时钟域的输入信号为src_pulse和src_rst;

目的端时钟域的输入信号为dest_rst,输出信号为dest_pulse(src_pulse跨时钟域后的结果)。

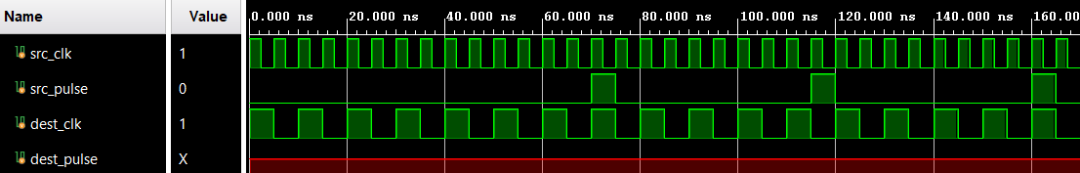

这些参数对仿真以及实际电路都有较大影响。如果参数INIT_SYNC_FF为0,同时RST_USED也为0,这就表明了仿真时不能使用同步寄存器链路的初始值,同时也没有复位信号对其复位,这样仿真时就会出现未知态,如下图所示。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何处理跨时钟域这些基础问题2024-01-08 1326

-

跨时钟域电路设计:单位宽信号如何跨时钟域2023-08-16 2154

-

从处理单bit跨时钟域信号同步问题来入手2023-06-27 2601

-

FPGA跨时钟域处理方法(一)2023-05-25 2887

-

跨时钟域电路设计总结2023-05-18 1301

-

跨时钟域电路设计:多位宽数据通过FIFO跨时钟域2023-05-11 4832

-

关于跨时钟域信号的处理方法2022-10-09 8060

-

看看Stream信号里是如何做跨时钟域握手的2022-07-07 6900

-

关于跨时钟域的详细解答2021-04-27 4931

-

总线半握手跨时钟域处理2021-04-04 3621

-

CDC单bit脉冲跨时钟域的处理介绍2021-03-22 4192

-

跨时钟域控制信号传输设计方案2020-10-16 1440

-

跨时钟域信号的几种同步方法研究2012-05-09 1250

全部0条评论

快来发表一下你的评论吧 !