CML耦合方式介绍

描述

CML(Current Mode Logic)电流模式逻辑电路主要靠电流驱动,它的输入与输出的匹配集成在芯片内部,基本不需要外部端接,从而使单板硬件设计更简单、更简洁。被广泛应用于网络物理层的传输和高速Serdes器件。

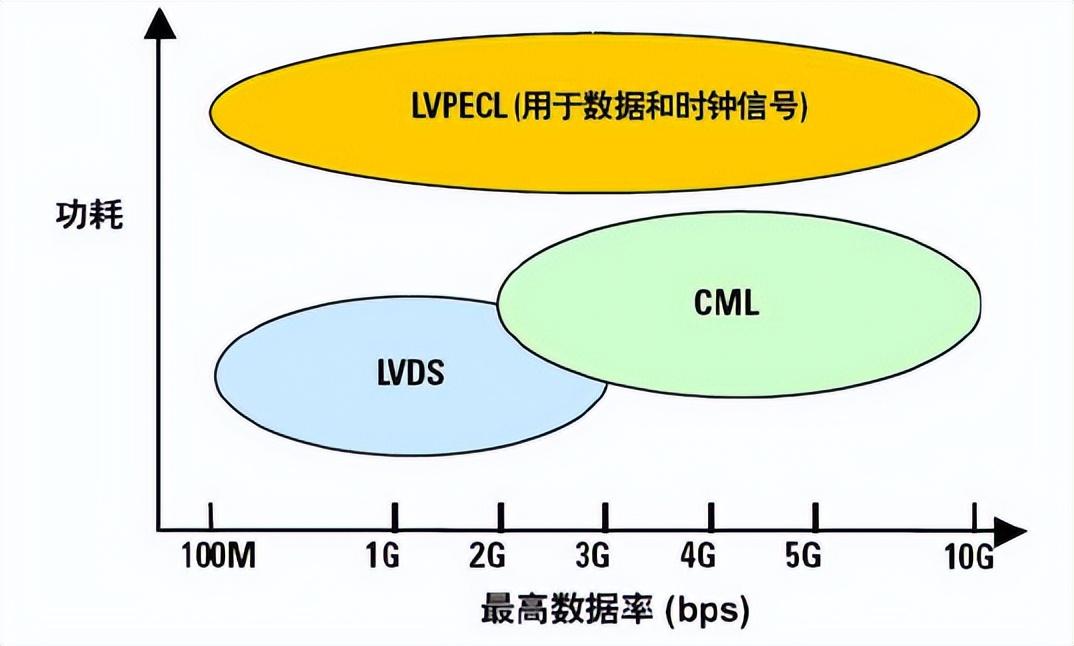

速度更高,CML理论极限速度可达10Gbit/s;

功率更低,

外围更简单,几乎不需要外围器件

1、CML输入输出结构

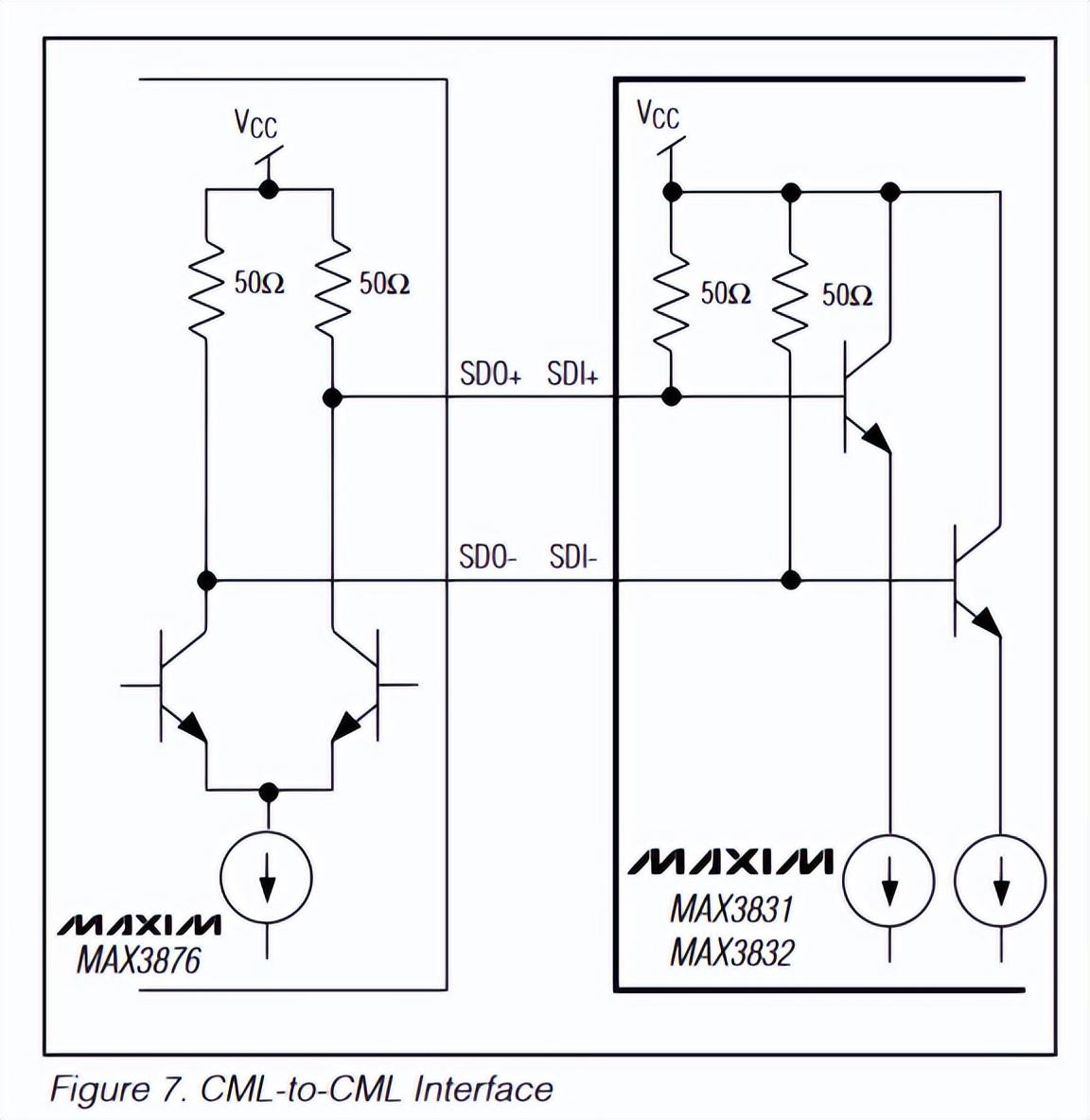

CML 接口的输出电路形式是一个差分对,该差分对的集电极电阻为50Ω,恒流源典型值为16mA。

CML输入与输出接口拓扑

2、CML输出波形

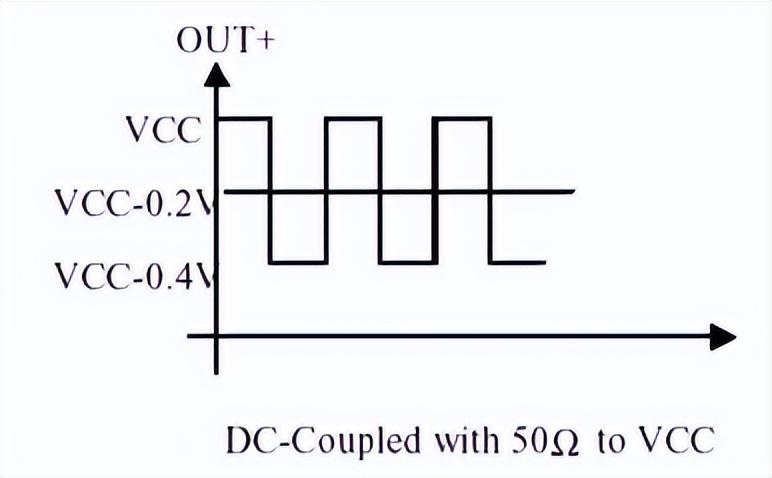

DC耦合时,CML 输出负载为一50Ω上拉电阻,单端CML 输出信号的摆幅为Vcc~Vcc-0.4V。

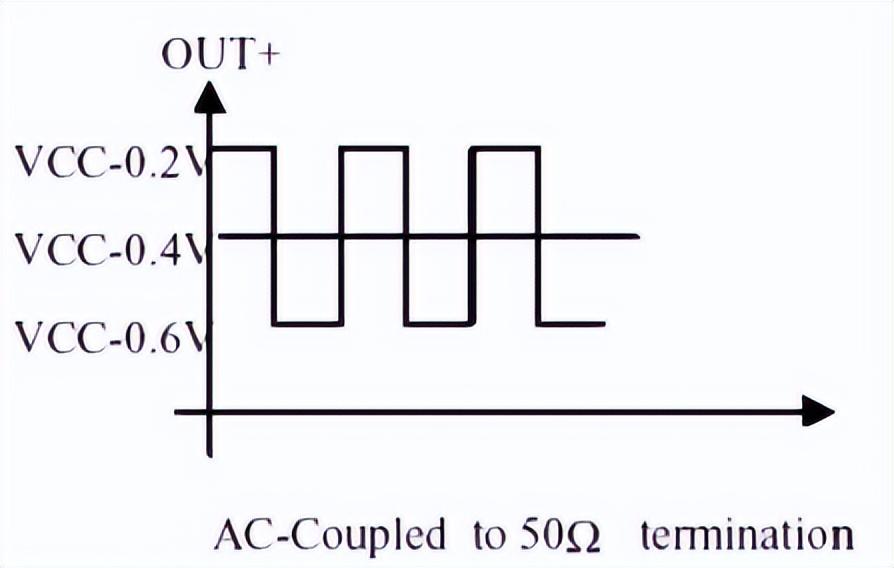

AC耦合时,CML 输出负载经过电容后经过50Ω上拉电阻,单端CML 输出信号的摆幅为Vcc-0.2~Vcc-0.6V。

3、CML耦合方式

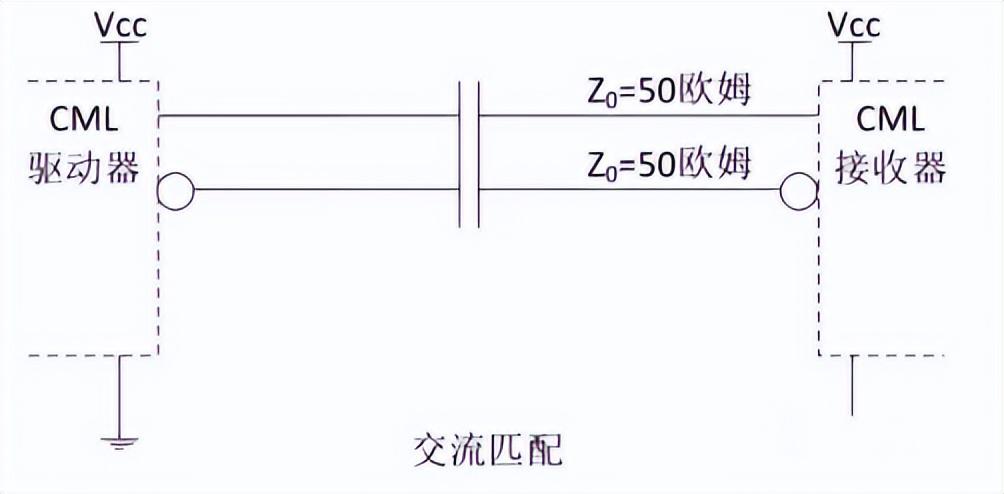

如果接收器有内置匹配(上拉50Ω电阻)与发送器采用不同的电源用交流耦合方式。

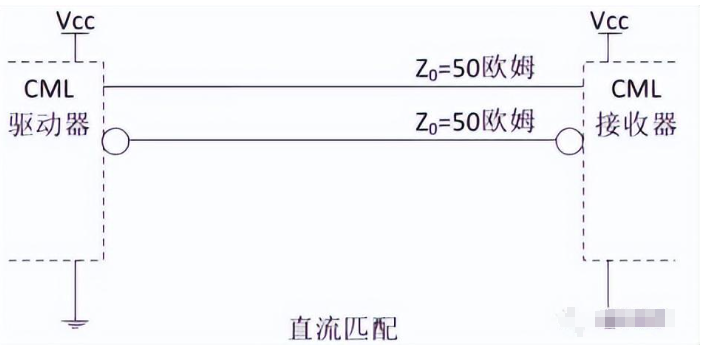

如果接收器有内置匹配(上拉50Ω电阻)与发送器采用相同的电源用直流耦合方式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请问DS90LV001是否可以接受CML的差分信号?2025-01-13 286

-

电路的耦合方式怎么判断正负2024-08-09 2120

-

多级放大电路耦合方式的特点是什么2024-08-07 2077

-

电路的耦合方式怎么判断2024-02-18 4762

-

如果ad9680的clk和sysref信号采用lvpecl格式输入,交流耦合的话前端网络如何设计?2023-12-06 626

-

耦合电容的原理及耦合方式2023-06-09 6020

-

如何在LVPECL、VML、CML、LVDS和子LVDS接口之间转换2022-11-21 1044

-

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连2020-12-20 40981

-

请问如何在Kintex-7 HP输入端终止交流耦合CML信号?2020-07-21 1762

-

定向耦合器的两种耦合方式和如何设计与制作双定向耦合器2020-03-27 3858

-

LVPECL、VML、CML、LVDS 与LVDS之间的接口连接转换2018-09-13 15156

-

示波器触发耦合方式的选择方法介绍2018-02-02 31927

全部0条评论

快来发表一下你的评论吧 !