环路增益及其对模拟控制系统的影响

描述

本文汇集了开环增益、闭环增益、增益和相位裕量、最小增益稳定性的概念,并展示了这些参数在反馈系统中是如何相互关联的。它从理论控制系统以及实际电子电路(包括线性稳压器)的角度检查环路增益。

介绍

Bob Dobkin 的 2014 年新线性稳压器解决老问题一文介绍了突破性的低压差线性稳压器 LT3081 表明,与其他 LDO 解决方案相比,其恒定环路增益改善了瞬态响应和绝对输出电压精度。这一说法虽然令人印象深刻且真实,但对工程师对环路增益的理解以及恒定环路增益与LT3081的优势之间存在明确联系做出了重要假设。遗憾的是,环路增益并不像闭环和开环增益那样被普遍认可。

如果不了解环路增益及其对电子电路的影响,就无法真正理解LT3081的优势。本文面向电源工程师,研究环路增益对增益和相位裕量的影响,并将其与理论控制系统和实际模拟反馈电路相关联。

基础知识

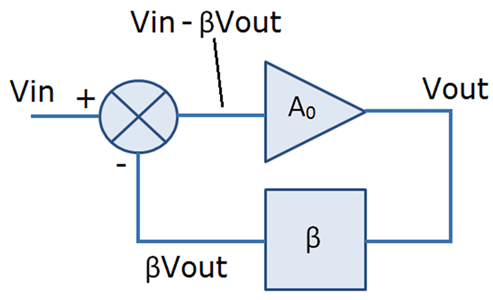

经典的模拟构建模块是运算放大器,其行为可应用于大多数反馈控制系统。事实上,许多器件的性能可以通过将其建模为运算放大器来简化。我们可以将运算放大器理论应用于低压差线性稳压器(LDO)和开关稳压器,以预测器件的稳定性。图1所示为简化的运算放大器电路。

图1.简化运算放大器电路

输入电压施加于误差放大器,误差放大器从V中减去输出电压的一小部分(β)在以产生错误信号。因此错误是

该误差信号受放大器(A0)的开环增益的影响,以产生输出电压:

重新排列以找到放大器的闭环增益:

在大多数运算放大器电路中,放大器的开环增益非常高,即远大于分母中的“1”,从而实现闭环增益近似值:

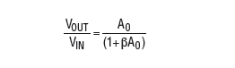

图2所示为传统运算放大器电路,其中可预测的工作取决于该增益近似值。

图2.传统运算放大器电路

对于输出端的任何给定电压,如果开环增益为无穷大,则两个输入引脚之间的电压差(V差异) 为零,运算放大器进行调节以使其两个输入引脚保持在同一电压。此处,输出通过电阻分压器R1-R2反馈到输入端,因此反馈分数(β)为0.1(1k/10k)。根据上式,如果开环增益较高,则电路的闭环增益近似于反馈分数的倒数,因此电路的闭环增益为10。

这种简化的运算放大器理论可用于对各种电路进行建模,适用于低频输入,但这种简单的模型在高频输入下失去有效性。

环路增益和交流运算放大器

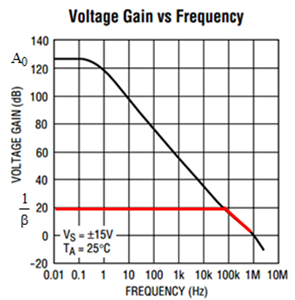

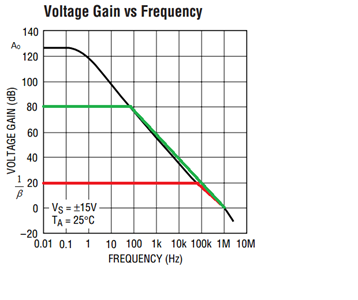

LT®1012 运放具有图 3 所示的经典开环增益与频率响应的关系。

图3.LT1012 运放开环和闭环增益与频率的关系

在图3中,您可以看到开环增益在高达0.3Hz的输入频率下很大,此后以每十倍频程20dB的速率衰减。尽管增益在很宽的输入频率范围内仍然非常高,但有时开环增益不能被认为是相对无限的。也就是说,当开环增益接近闭环增益时,上述理想运算放大器模型以及我们对其性能所做的相应假设开始失去可信度。

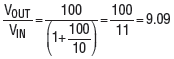

考虑有限开环增益对图2电路闭环增益的影响。反馈分数(β)为1/10,因此在理想的运算放大器模型中,闭环增益是其倒数,即10。如果我们的运算放大器的开环增益为100,则计算出的闭环增益为

计算的闭环增益

增益仍然约为10,但误差为9%。

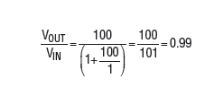

现在考虑使用相同的放大器,但具有单位增益反馈。反馈分数(β)为1,因此理想的运算放大器闭环增益应为该增益的倒数,即1。如果我们的运算放大器的开环增益为100,则闭环增益

虽然这两个电路的开环增益相同,但只需降低闭环增益,增益误差就会降低到1%。

上面的方程表明,误差是βA大小的函数0与分母中的“1”项有关。请注意,开环增益本身并不总是决定误差,但它是开环增益(A0)和重要的反馈分数(β)。适用于大 βA0,“1”项失去意义;对于 βA0接近于统一,“1”变得显着,增加了误差。

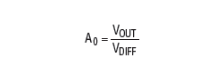

什么是βA0

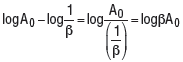

那么什么是βA0?在图3中,闭环曲线(约1/β)和开环曲线(A0),在对数刻度上为

所以开环增益曲线和闭环增益曲线之间的间隙为βA0(直流时约为 105dB)。参考图 1,我们可以看到 A0• β是通过放大器和反馈环路的增益,因此βA0是我们的环路增益,表示系统中可用的超额增益。虽然人们通常认为放大器的开环增益应该很高,以使运算放大器增益准确,但我们可以看到,不一定是开环增益,而是必须很高的环路增益。换句话说,开环增益必须高于闭环增益才能获得精确的电路增益。

那么有限开环增益对运算放大器电路有什么影响呢?基本运算放大器理论指出,两个输入电压调节到相同的电压,这是在非常高的开环增益下的一个合适假设,但是当开环增益随着信号频率的增加而降低时会发生什么?

考虑图2所示电路:随着放大器的开环增益随着输入频率的增加而降低,我们看到两个输入引脚之间的交流电压增加,等于输出电压除以开环增益。这不是输入失调电压,而是小交流电压(V差异),等于输出电压除以放大器的开环增益。如果开环增益为1万,输出端有<>V,则V差异两个输入引脚两端为 1μV。随着输入频率上升,开环增益下降,V差异增加。极端情况下,开环增益衰减到10,我们的V差异变为显著的 100mV。

这就是许多人误解运算放大器在较高交流频率下的工作的地方,其中两个输入引脚不再调节到相同的电压。两个输入引脚之间的电压由直流输入失调电压(为简单起见,我们在这里忽略)和V组成差异.V差异通常可以忽略,但在高频下不能忽略。

我们知道开环增益由下式表示

我们知道β由

其中 V–是反相输入端的电压,因此环路增益由下式给出

环路增益将V–(应等于输入信号)与VDIFF进行比较。

相移的影响

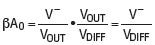

还有一个与VDIFF相关的相移。图3所示的开环增益曲线与低通滤波器的响应相同。有一个0.3Hz的中断频率,之后增益以每十倍频程20dB的速度滚降,另一个在1MHz处滚降,之后增益以每十倍频程40dB的速度滚降。图4所示为具有相同断路频率的低通滤波器。

图4.频率响应与图2中的开环增益曲线相匹配的低通滤波器

单阶低通滤波器(由R1和C1组成)的传递函数由下式给出

根据经验,对于单阶低通滤波器,在十分之一的断断频率下,相移大致为零。在每个分断频率处,相移 –45°(相位滞后),在断断频率的十倍处,相移约为 –90°,超出该值。如果第二个断路频率为1MHz,则在100kHz时,滤波器的总相移约为–90°,在1MHz时,总相移为–135°,在10MHz时,总相移约为–180°。

由于放大器的开环增益行为相同,尽管图2所示的输入和输出电压同相,但VDIFF和VOUT之间存在与放大器开环增益相移相关的相移。同样,由于VDIFF通常很小,我们可以忽略它,但是随着输入频率的增加,VDIFF与输入电压异相的增加可能会导致稳定性问题。图3所示的开环增益曲线没有稳定性问题,但很容易想象,如果第二次分断频率的频率远低于1MHz,我们的电路现在将有一个增加的VDIFF,有可能与输入电压异相180°,这肯定会对稳定性产生影响。

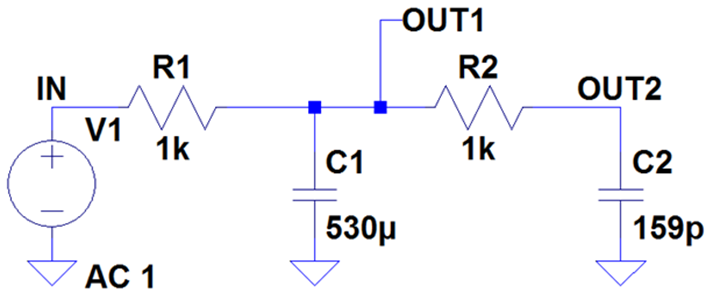

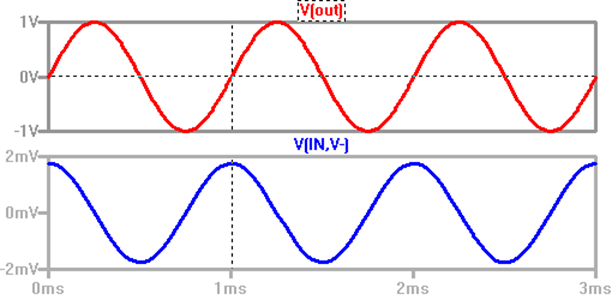

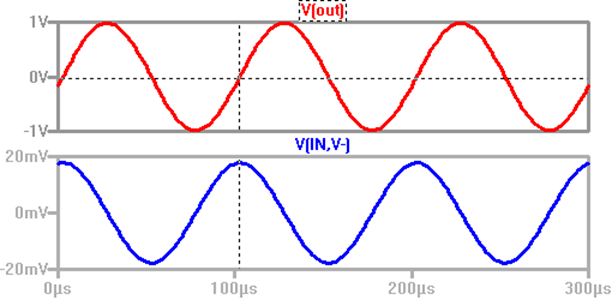

LTspice是分析不同频率下相移效应的有用工具。图5a显示了输出电压在1kHz时将VDIFF滞后90°。

图 5a. VOUT 在 1kHz 时相位上比 VDIFF 滞后 90°

如果输入频率从1kHz增加到10kHz,VDIFF加10倍,但相位滞后保持90°,表明我们远未达到开环增益的第二次断开频率。如图 5b 所示。当输入频率接近1MHz时,相位滞后开始增加到90°和V以上差异相应增加。

图 5b. VOUT 在 10kHz 时相位滞后 VDIFF 90°

所以可以看出,VDIFF可能得出一个与输入电压相当且与输入电压异相180°的值——要使电路振荡,环路周围的增益必须是单位的,环路周围的相移必须为180°。如果 V差异受放大器的开环增益(A0),那么反馈网络的衰减,(β),我们可以看到它是环路增益(βA0)及其决定系统稳定性的相位。

考虑图2中的电路,运算放大器放大其输入之间的电压(VDIFF),并受到βA0增益的影响,从而产生V–电压。如果环路增益为1,则意味着V-处的电压与VDIFF相同,因此VDIFF的幅度在通过环路时没有变化。如果它经历了180°的相移,并且VDIFF的幅度没有变化,则电路将振荡。纯粹主义者可能会争辩说,相移必须是360°,而这个额外的180°由反相输入引脚提供。

附带说明一下,如果图2中的电路具有高增益,则意味着反馈电阻会大幅衰减输出电压。大部分相移发生在放大器中(因为反馈电阻没有电抗元件,因此不存在相移),因此增益越低,反相输入端出现的“相移”输出电压越多,从而增加了不稳定的可能性。这就是为什么一些放大器具有最低增益稳定性的原因。如果将增益降低到某一点以下,反相端会出现更多的相移输出电压,因此电路更容易振荡。

值得考虑图2中电路在各种环路增益和相移下的工作原理。

在低频时,当放大器具有足够的环路增益时,V差异很小,与反相输入端的电压相比,相移为 –90°(V–).在这种情况下,反相输入端的电压沼泽V差异,所以 V差异可以忽略不计。但是,如果相移V。差异相对于 V 为 –180°–,并且环路中有增益,我们可以看到 V 处的任何电压差异在环路周围行进时被放大并反转,然后放大和反转,因此电路振荡。电路只需要具有单位环路增益即可维持振荡。多近 V差异当电路具有单位环路增益时达到–180°,用于衡量电路的相位裕量,并告诉我们电路相位与不稳定点的接近程度。相移为–120°的电路具有60°的相位裕量。

同样,如果 V差异相对于 V 的相移为 –180°–,但在通过环路时会经历衰减,电压回到 V–较小,因此由于缺乏环路增益,任何潜在的振荡都会停止。衰减多少V差异当电路通过环路时(当相移为–180°时)的经验是电路增益裕量的量度,并告诉我们当相移为–180°时电路的环路增益比单位增益低得多。当V时环路衰减为10dB的电路差异是 –180° 的增益裕量为 10dB。

以上所有内容都可以与控制理论和图1中的框图相关。我们知道反馈系统的闭环增益由下式给出

其中 βA0是系统的环路增益。如果βA0具有–180°的相移和单位增益,分母在一个特定频率下变为零,电路在该频率下振荡。如果βA0很大,但没有–180°的相移,分母不为零,电路不振荡 - 我们有足够的相位裕量。同样,如果βA0小于单位,但相移为–180°,电路不振荡 - 我们有足够的增益裕量。

所以现在我们可以看到我们有相关的开环增益、闭环增益、环增益、增益裕量和相位裕量,并在控制理论领域和电路理论领域对此进行了解释。

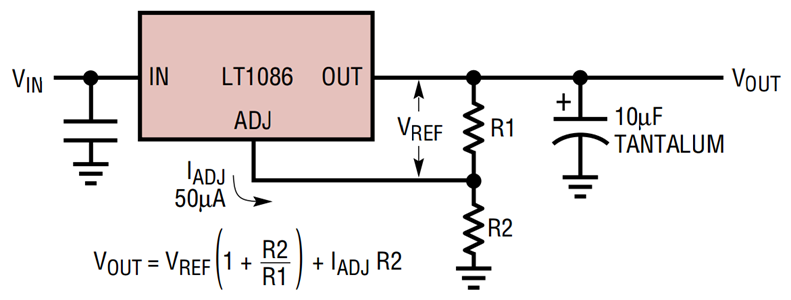

那么这与电源电路有什么关系呢?大多数电源系统都可以建模为运算放大器电路。图 6 示出了 LT1086 线性稳压器。我们可以看到,该电路有两个反馈电阻,它们为ADJ引脚(内部运算放大器的反相输入)提供一小部分输出电压。同相端子连接到内部基准电压。

图6.传统线性稳压器 (LT1086)

如上所述,放大器增益的精度由放大器的环路增益决定:放大器中的环路增益越大,增益精度越高。

增加 LT1086 的输出电压与增加一个运放的闭环增益相同。图7显示了将闭环增益从20dB增加到80dB的效果。如果环路增益由开环增益曲线和闭环增益曲线之差表示,那么增加 LT1086 的输出电压会降低环路增益,从而降低输出电压的绝对准确度。增加输出电压的另一个缺点是降低电路的频率响应(在本例中为100kHz至100Hz),因此负载瞬态响应受到影响。

图7.电压增益与频率的关系

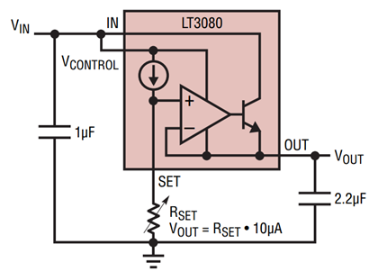

LT308x系列线性稳压器将传统的LDO架构更改为图8所示的架构。

图8.LT3080线性稳压器采用非常规架构来提高准确度和瞬态响应

LT3080 采用一个内部电流源来产生一个外部电阻器 R 两端的电压设置.然后将该电压施加到单位增益缓冲器以产生输出电压。这有许多含义。

内部运算放大器以恒定单位闭环增益工作,输出电压由 R设置运算放大器“输入”端的电阻值。

将图3080所示的LT7与图6所示的传统运放电路进行比较。图 1086 中 LT6 的输出电压通过改变 LT1086 的反馈电阻器 (以及闭环增益) 而改变。与此形成对比的是,LT3080 在恒定闭环增益下工作,其中放大器的“输入”电压由 R 两端的电压设定设置.如果闭环增益保持不变,则环路增益保持不变,因此即使在高输出电压下,该电路也具有良好的绝对精度。顺便说一下,这就是为什么DC/DC转换器中的环路补偿元件始终具有串联电容的原因。误差放大器的输出是电流源,直流时的串联电容是高阻抗的,因此在补偿环路中产生高环路增益。

保持环路增益不变的另一个结果是频率响应保持不变,并且在高输出电压下不会牺牲频率响应,因此该器件能够快速响应负载瞬变。

鉴于电源电压不断降低,LT308x 器件能够产生一个低至 0V 的输出电压,因此另一个特别令人感兴趣的好处是。传统的 LDO 无法将其输出电压设定为低于内部基准电压,而通过在 LT308x 部件上短路 RSET,输出电压可设定为低至 0V。

结论

LT308x 系列 LDO 由于其恒定的高环路增益,与传统 LDO 相比,具有更好的高输出电压准确度和瞬态响应。它们还可以以传统LDO无法使用的方式使用,例如将输出设置为0V,或并联它们以实现更高的电流操作。

审核编辑:郭婷

-

【开关电源控制环路设计:Christophe Basso 的实战秘籍】开环系统阅读 一2025-08-21 2405

-

环路增益和开环增益的区别是什么2024-07-30 5472

-

环路增益是什么?什么样的环路增益特性是理想的呢?2023-10-25 3853

-

控制系统中的开环增益和闭环增益2023-09-04 6714

-

过程控制系统_系统耦合方法和相对增益矩阵1#硬声创作季Hello,World! 2022-10-28

-

如何改善动态环路响应2020-12-01 2836

-

如何使用模拟数字技术改善动态环路响应2020-11-24 829

-

电源环路增益:电源环路增益的基本工作原理概述2019-04-30 7553

-

智能控制系统及其应用2016-04-13 848

-

集散控制系统及其应用实例2010-03-19 1788

-

音频信号自动增益控制系统2009-09-08 2565

-

控制系统的模拟2009-07-25 2931

全部0条评论

快来发表一下你的评论吧 !