优化PCB布局走线的EMC静电整改方案

EMC/EMI设计

描述

电子产品如手机,智能手表,TWS耳机在认证时往往需要做静电测试,测试过程出现不可恢复的故障,或整机复位重启。

问题详细描述

某智能手表在静电测试时,打充电输入端子的接触±4KV出现系统复位,甚至概率性卡死,长时间不能恢复。充电端子在bottom层,板子为四层一阶。

问题具体分析

1、分析如下:

经过对PCB的研究发现,在充电弹片和正极充电路径下方的相邻层信号线过多,没有完整的地来释放静电,并有高速的flash信号经过。当静电打进来时,静电瞬间干扰到信号走线,静电管还来不及释放静电,导致系统异常。

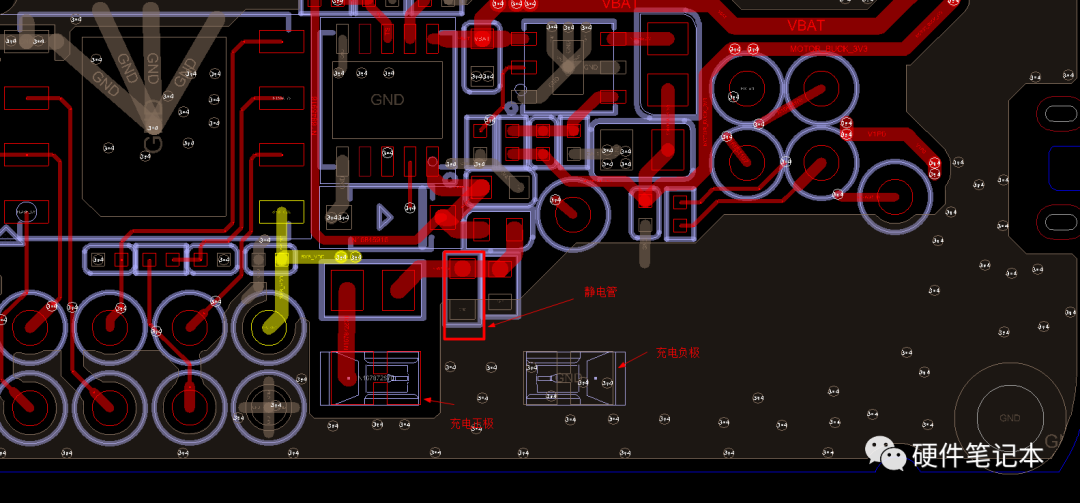

第四层(bottom层)走线如下(充电接触弹片所在层):

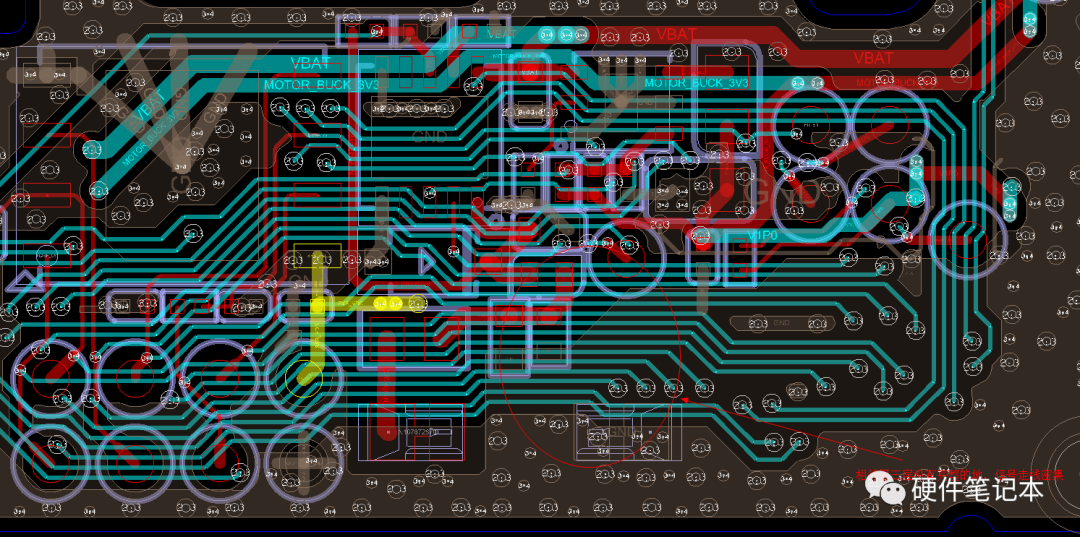

第三层走线如下:

2、根据上面的分析做实验

(1)在充电输入正极弹片就近并联一个静电管,让静电打正极接触弹片±6KV可以第一时间把静电从静电管处释放掉。

(2)正极弹片悬空起来(目的为了验证弹片所在的bottom层是否会影响到弹片下方相邻层的信号线),然后从充电输入正极弹片飞一根线到充电IC输入端电容处,电容之前的路径断开(确保充电通路正常),目的是为了避免原PCB上的充电路径走线有静电流过干扰到相邻的信号走线。经过这样的实验接触的±6KV稳过无异常通过。对比不处理±3KV都不行。

问题解决方案

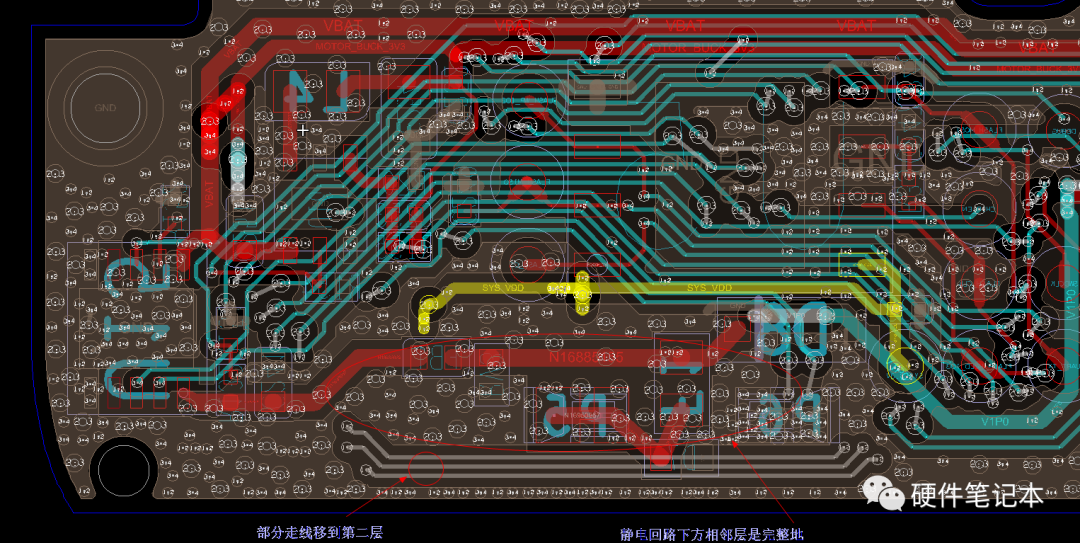

整改思路:优化PCB布局走线(把静电路径下方信号走线移走),缩短充电回路(目的是缩短静电通过的路径),充电回路下面净空不走线,静电通过的路径邻层有完整的地。静电释放的径路是通过第三层的地进入到第二层主地层。

具体优化如下:

总结和建议

静电是具有辐射干扰的,在PCB布局走线时尽可能是把静电管靠近静电进来的位置,同时要就近打孔,让静电快速进入主地层,以免干扰到其他敏感器件或走线。静电通过的路径相邻层尽可能有完整的地,避免有敏感信号经过。

编辑:黄飞

-

PCB布局的关键:开关节点走线尺寸满足电流?(3)2023-08-08 2052

-

EMC测试整改:提升产品合规性和市场竞争力?|深圳比创达电子2024-03-07 12960

-

探秘 EMC 本质:比创达为你解析 EMC 设计整改核心原理与解决方案2025-02-06 1271

-

PCB 布局、走线资料2014-08-02 3192

-

USB接口的EMC整改方案2016-06-13 11386

-

案例分析||医用电钻静电整改2016-07-29 4883

-

pcb布局,走线方面2016-10-15 5815

-

EMC整改的万能方法论(五分钟的时间教会你EMC整改)2017-11-22 9059

-

电磁兼容EMC整改2019-03-13 12728

-

PCB布局和走线的调整2019-10-17 3563

-

如何优化高速无刷电机的EMC?2023-03-13 2138

-

开关电源的PCB设计(布局、排版、走线)规范2016-09-06 1409

-

EMC测试整改:了解EMC测试及解读整改方案2023-12-06 2932

-

线束EMC电磁兼容性测试整改:源头到末端全面优化2025-02-10 1408

-

工业电子EMC整改:问题定位到系统优化的定制方案2025-12-04 703

全部0条评论

快来发表一下你的评论吧 !