看看电源噪声对信号质量的影响

电子说

描述

一、写在文前

目前对于DDR4、DDR5等并行信号,信号速率越来越高,电源性能要求也越来越高,今天我们就来看看电源噪声对信号质量的影响;

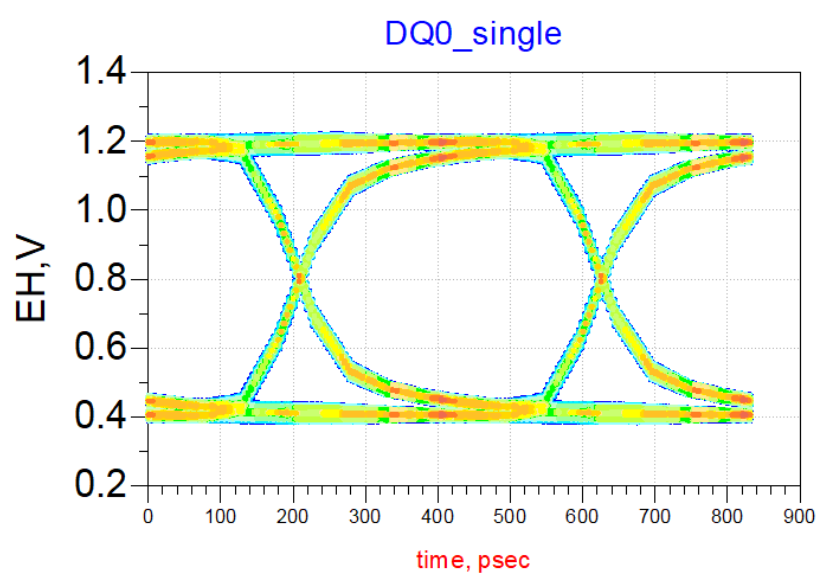

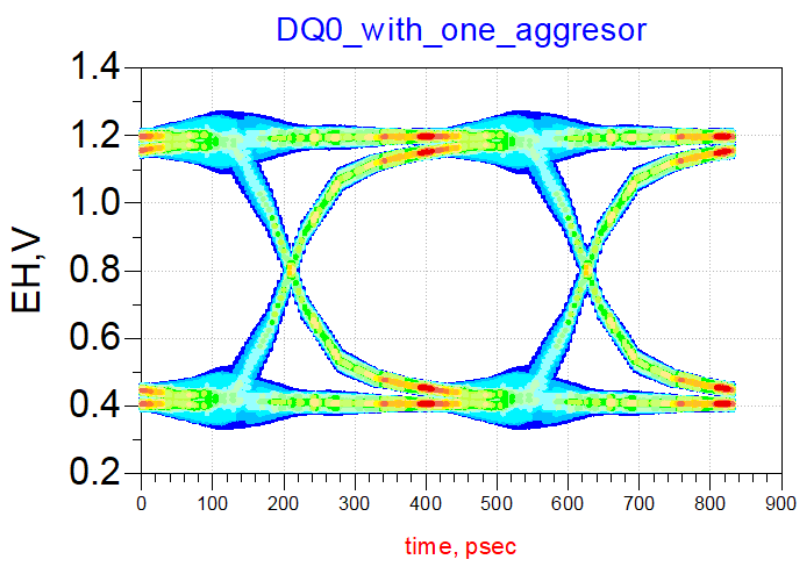

先来看下面的一组DQ 信号,信号速率为2400Mbps,眼图如下:

从眼图来看,还是不错的,但是现在对于DDR信号而言,除了信号单通道的影响外,还有一些其他影响,比如临近线的串扰,在上图信号的基础上,增加了一个临近线的串扰,眼图如下:

可以看到,眼图恶化了不少,上面这只是其中一条表层微带线的影响,平行走线为400mil,线间距为2*w(中心距);

当然这不是本文的重点,本文的重点是讨论一下电源对信号的影响;

二、DDR4-2400信号电源联合仿真

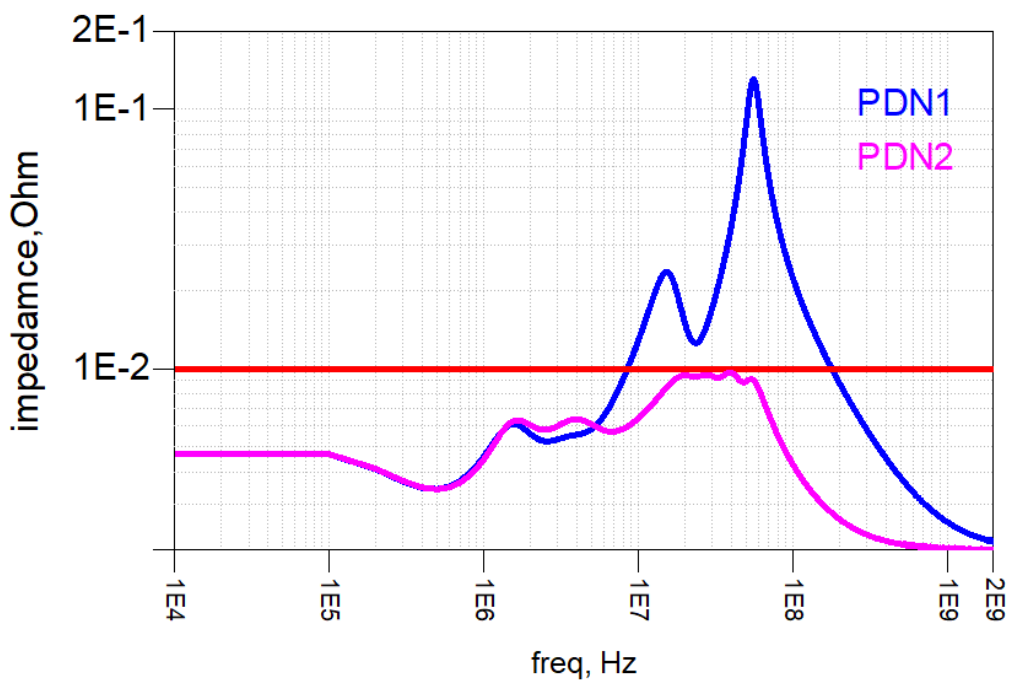

为了对比,我们设计了两组电源系统(以下用PDN1、PDN2代替),包含了DIE_model、PKG、PCB以及VRM的RL等效模型;其各自的PDN阻抗曲线对比如下:

可以很明显看出,PDN1的阻抗曲线在15MHz和50MHz处有较大谐振,阻抗值已经达到了0.1Ohm,而PDN2的阻抗则比较平坦,且都保持在0.01Ohm以下;

对于PDN1的电源系统,很容易产生比较大的噪声,而DDR4这种多端口并行链路很容易产生同步跳变电流,从而作用在PDN1这样的系统中,进而产生电源噪声,影响芯片电路和信号;

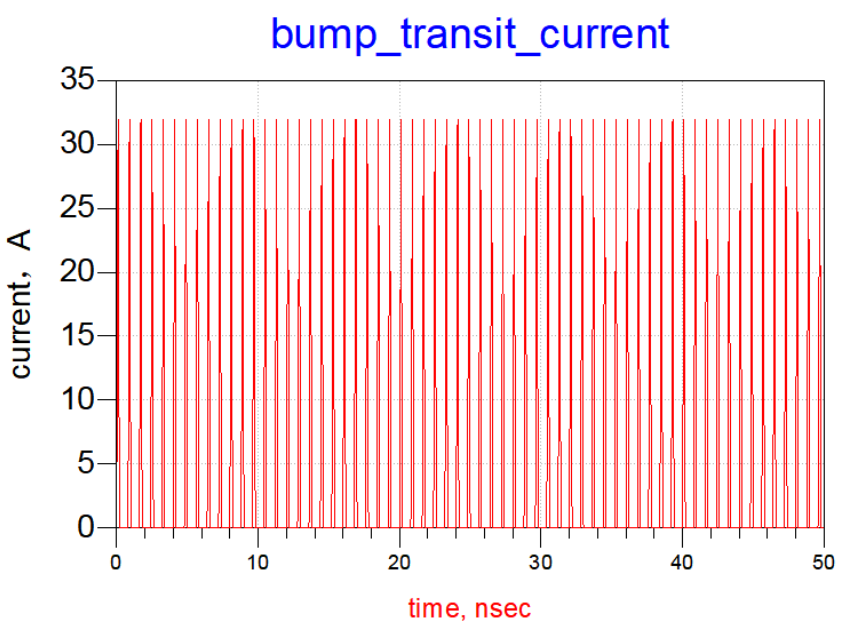

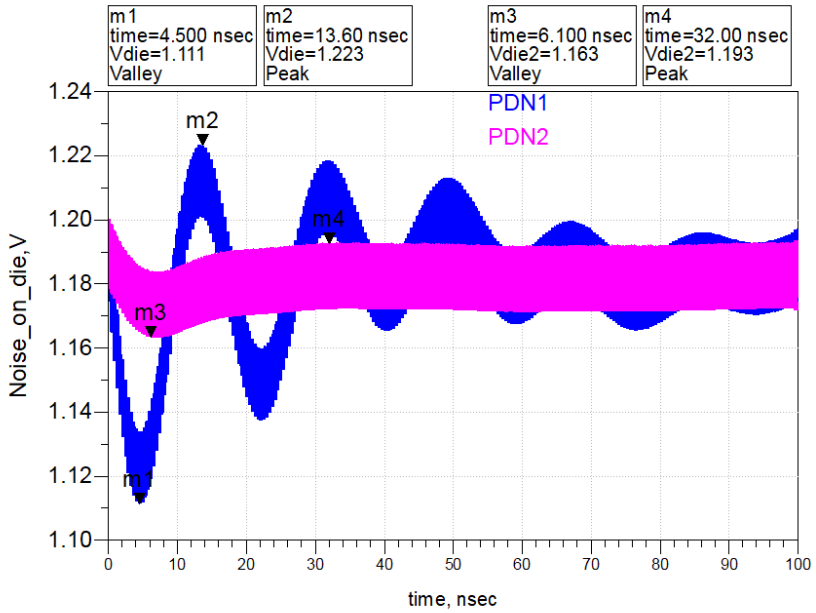

我们用下图的脉冲电流加载PDN1和PDN2的die端,观察噪声情况:

可以看到两个电源系统产生的噪声差异非常大,PDN1的噪声更大;

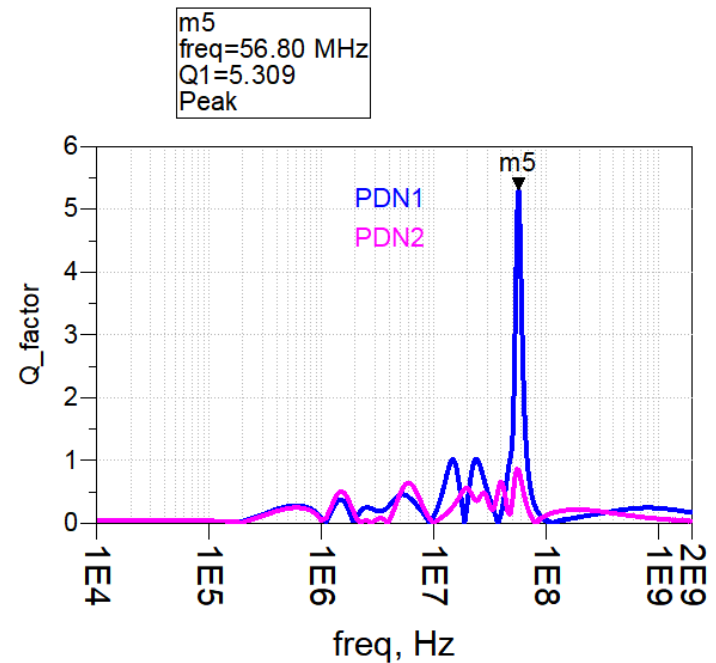

两个系统的Q值比较如下:

可以看到 ,PDN1系统的阻抗值不仅大,而且Q值非常高;

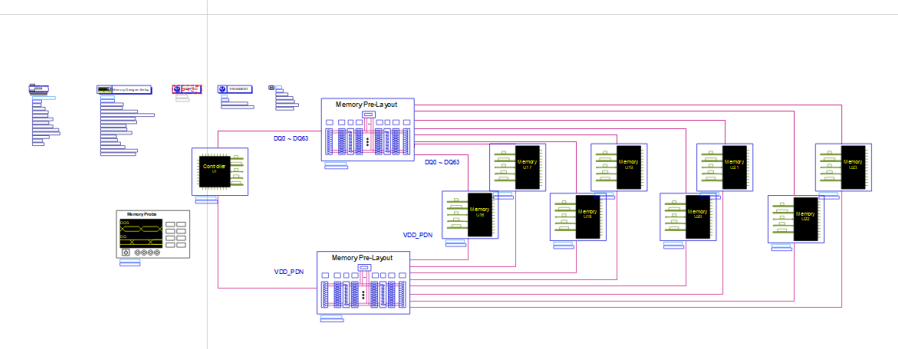

下面我们在power-aware当中实际跑一下信号、电源的联合仿真,来看一下电源对信号的影响,我们运行的DDR4为2400Mbps、64bit、8颗mem芯片;

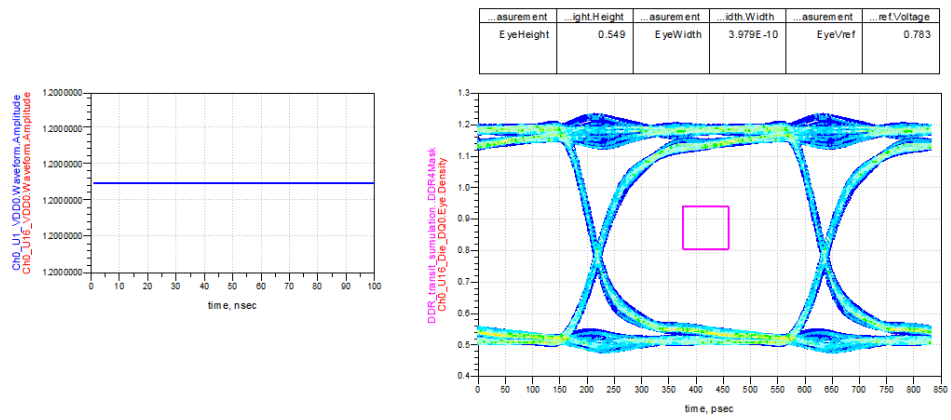

在没有考虑电源的影响时,眼图如下:

可以看到,控制器和DDR芯片的电源是恒定的1.2V,此时眼图还算比较干净,和之前我们仿真的有一个临近线串扰的眼图基本一致;

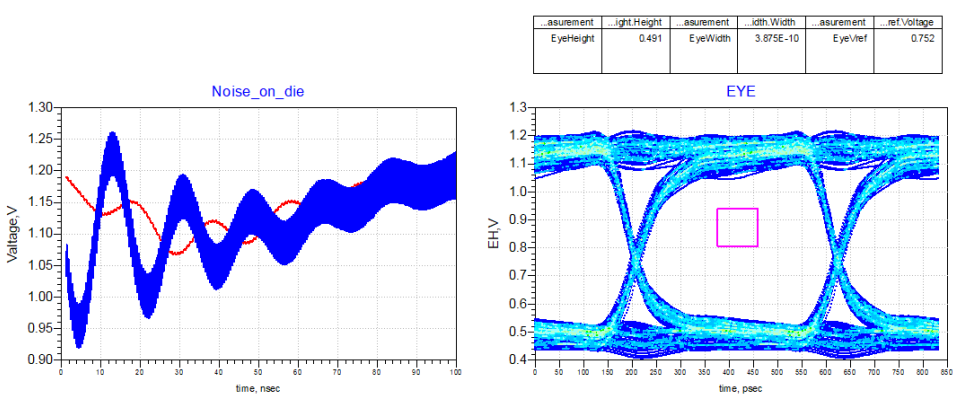

接下来看一下在PDN1系统下的信号质量:

可以看到,此时,电源已不再是恒定的1.2V,而是有了噪声,而此时的DQ眼图也变差很多;

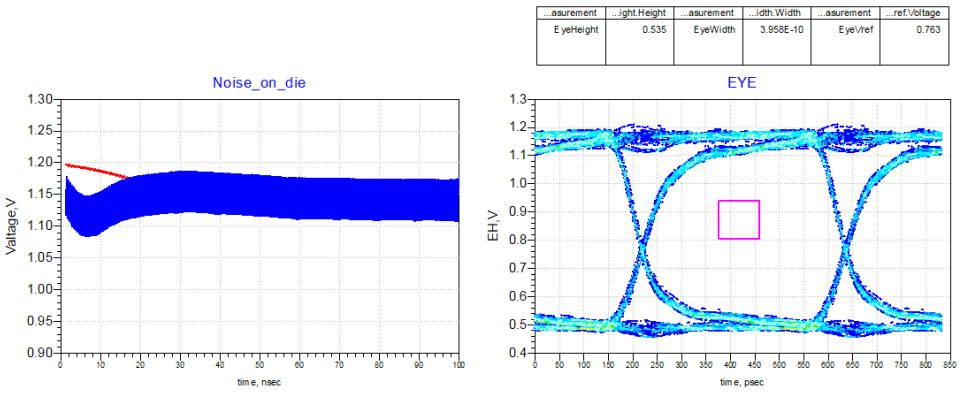

我们为了对比,再在PDN2上面运行,结果如下:

无论是电源噪声,还是眼图质量都是比PDN1要好的,可见电源对于信号的影响是非常大的,尤其对于DDR这么多的并行端口同时反转时导致的SSO,而且DDR信号本身的敏感度也在提升,所以单纯的考虑信号本身的影响已经不够谨慎。

审核编辑:刘清

-

低噪声开关电源的用途有哪些?2025-12-01 1671

-

如何评估CAN总线信号质量2025-06-07 783

-

信号发生器在相位噪声测量中的应用2025-03-13 997

-

多级运放级联如何安排运放放大倍数才能让信号质量最优噪声小?2024-08-27 923

-

电源滤波器是怎么降低电源噪声的?2023-12-15 1809

-

开关电源纹波噪声测试方法是什么?纹波噪声的测试标准是什么?2023-11-09 5319

-

信号链的电源管理如何选?2023-08-08 1760

-

电源噪声对模拟信号处理器件的影响2023-01-30 2526

-

电源噪声的主要来源2021-10-29 1375

-

优化信号链的电源系统 — 多少电源噪声可以接受?2021-06-16 3079

-

PSRR和其它电源噪声对手机音频质量有什么影响?2021-06-02 1692

-

对电源噪声的分析与产生的原因2018-06-29 16264

-

改善RF信号质量的电源线噪声对策2015-10-25 2052

-

为什么FPGA产生高频信号影响电源质量2015-06-06 4092

全部0条评论

快来发表一下你的评论吧 !