什么是ECO?ECO的应用场景和实现流程

描述

什么是 ECO?

ECO 指的是Engineering Change Order,即工程变更指令。目的是为 了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证 的功能和时序。ECO 的叫法算是从 IC 设计领域继承而来,其应用在 FPGA 设计上尚属首次,但这种做法其实在以往的 FPGA 设计上已被广泛采用。简单来说,ECO 便相当于 ISE 上的 FPGA Editor。

但与 FPGA Editor 不同,Vivado 中的 ECO 并不是一个独立的界面或是一些特定的命令,要实现不同的 ECO 功能需要使用不同的方式。

ECO 的应用场景和实现流程

ECO 的应用场景主要包含:修改cell 属性、增减或移动 cell、手动局部布线。还有一些需要多种操作配合的复杂场景,例如把 RAM(或 DSP)的输出寄存器放入/拉出 RAMB(或 DSP48)内部,或是把设计内部信号接到 I/O 上作调试 probe 用等等。

针对不同的应用场景,Vivado 中支持的 ECO 实现方式也略有区别。 有些可以用图形界面实现,有些则只能使用 Tcl 命令。但通常可以在图形化界面上实现的操作,都可以改用一条或数条 Tcl 命令来实现。

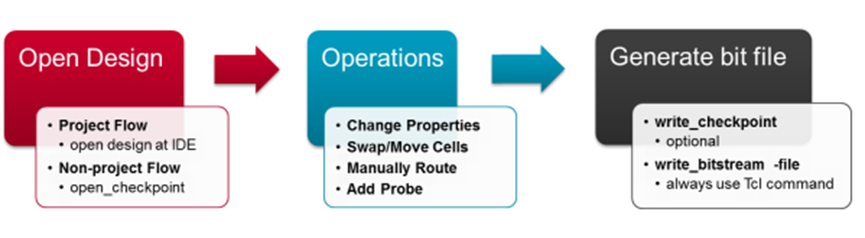

ECO 的实现流程如下图所示:

第一步所指的 Design 通常是完全布局布线后的设计,如果是在工程模式下,可以直接在 IDE 中打开实现 后的设计,若是仅有 DCP 文件,不论是工程模式或是非工程模式产生的 DCP,都可以用 open_checkpoint 命 令打开。

第二步就是 ECO 的意义所在,我们在布局布线后的设计上进行各种操作,然后仅对改动的部分进行局部布局/布线而无需整体重跑设计,节约大量时间的同时也不会破坏已经收敛的时序。

第三步就是产生可供下载的 bit 文件了,此时必须在 Tcl Console 中或是 Tcl 模式下直接输入命令产生 bit 文件,而不能使用 IDE 上的“Generate Bitstream”按钮。原因是后者读到的还是 ECO 前已经完成布局布线的原 始设计,生成的 bit 文件自然也无法使用。

修改属性

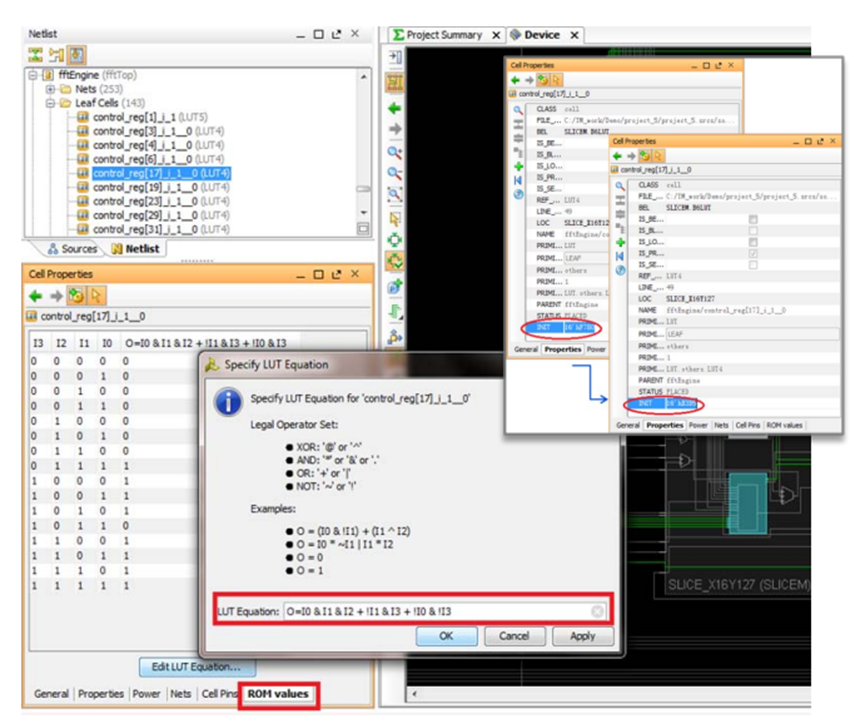

绝大部分的属性修改都能通过 IDE 界面完成,如下图所示。

比如要修改寄存器的初值 INIT 或是 LUT 的真值表,用户只需在 Vivado IDE 中打开布局布线后的设计 (Implemented Design),在 Device View 中找到并选中这个 FF/LUT,接着在其左侧的 Cell Properties 视图中 选择需要修改的属性,直接修改即可。

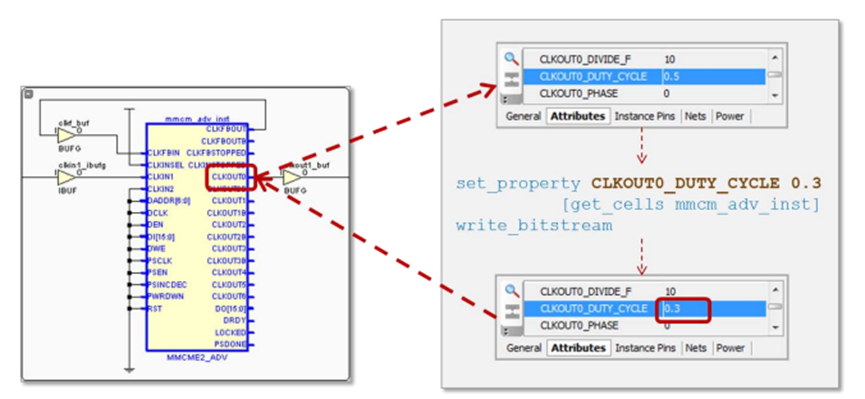

除了对 FF/LUT 的操作外,很多时候我们需要对 MMCM/PLL 输出时钟的相移进行修改。对于这种应用,用户也无需重新产生 MMCM/PLL,与上述方法类似,可以在布局布线后的 Device View 上直接修改。

移动/交换 cells

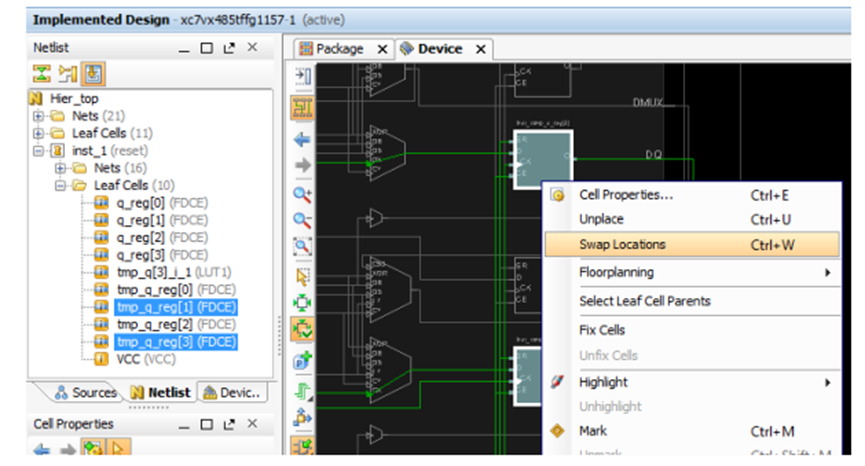

移动/交换 cells 是对 FF/LUT 进行的 ECO 操作中最基本的一个场景,目前也只有这种情况可以通过图形化实现。如要删减 cells 等则只能通过 Tcl 命令来进行。

具体操作方法也相当简便,要互换 cells 位置的情况下,只要在 Device View 上选中需要的那两个 cells,如上图所示的两个 FFs,然后右键调出菜单,选择 Swap Locations 即可。若要移动 cells 则更简单,直接在图 中选中 FF 拖移到新的位置即可。

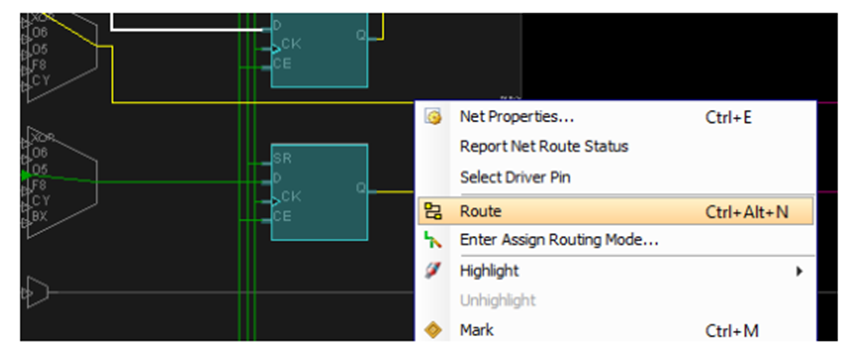

当用户移动或改变了 cells 的位置后会发现与其连接的 nets 变成了黄色高亮显示,表示这些 nets 需要重新布线。这时候需要做的就是在图中选中这些 nets 然后右键调出菜单,选择 Route 进行局部布线。

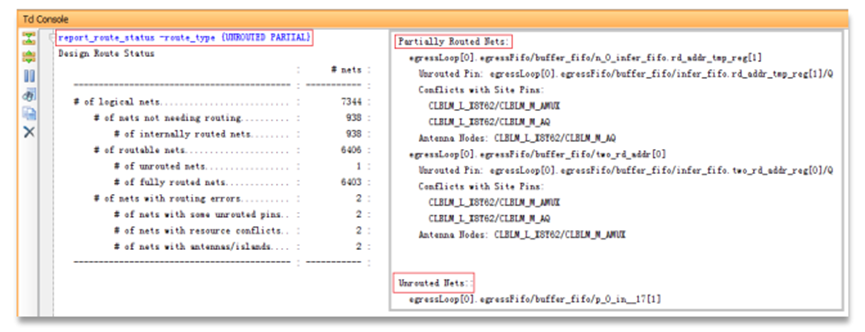

局部布线后一定要记得在 Tcl Console 中使用 report_route_status 命令检查布线情况,确保没有未完成布线(unrouted)或是部分未完成布线(partial routed)的 nets 存在。给这个命令加上选项则可以报告出更细致的结果,如下图所示。

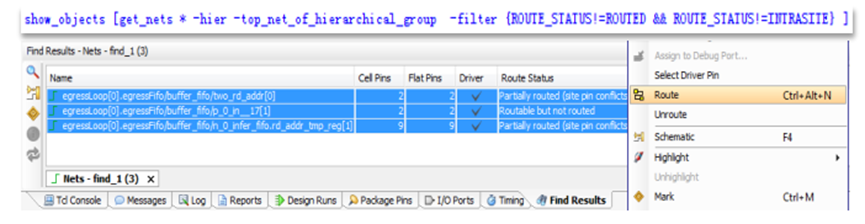

如果换个稍复杂些的 Tcl 命令配合图形化显示,更加直观的同时,也可以方便右键调出命令进行针对性的局部布线。

手动布线

手动布线是一种非常规的布线方式,一次只能针对一根 net 在图形化界面下进行。所谓手动布线,除了完全手动一个节点一个节点的选择外,也支持工具自动选择资源来布线。通常我们并不建议全手动的方式, Vivado 是时序驱动的工具,所以其自动选择的布线结果已经是遵循了时序约束下的最佳选择。

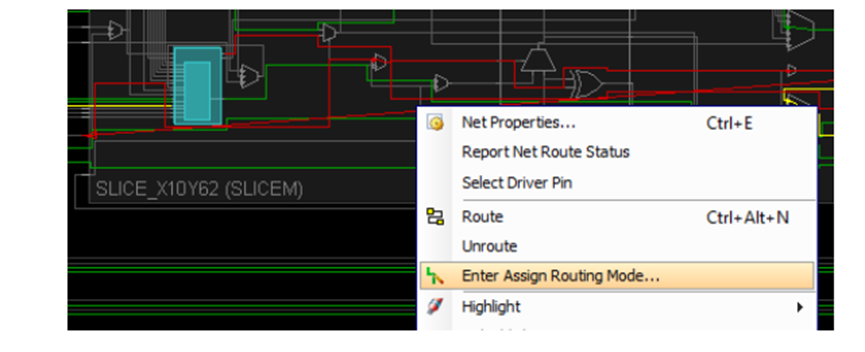

在 Device View 中选择一根没有布线或是预先 Unroute 过的 net(显示为红色高亮),右键调出菜单并选择 Enter Assign Routing Mode… 便可进入手动布线模式。

复杂的 ECO场景

篇幅过半,一直在铺垫,其实最有实践意义的 ECO 还没提到。相信大部分用户最怀念 FPGA Editor 中的 一个功能就是 probe 了,如何快速地把一根内部信号连接到 FPGA 管脚上,无需重新布局布线,直接更新 bit 文件后下载调试。曾经数次被客户问及,很多人还为 Vivado 中不支持这样的做法而深表遗憾。

其实这样类似的功能在 Vivado 中一直支持,唯一的问题是暂时还没有图形化界面可以一键操作(相关开 发工作已经在进行中)。但受益于 Tcl 的灵活多变,我们可以更有针对性地实现 probe 功能,效率也更高。

Tcl 操作命令

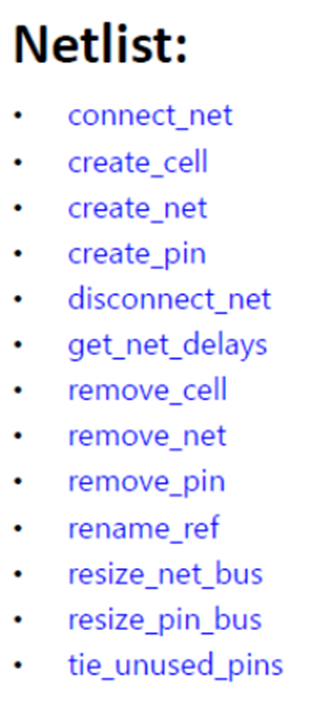

在 UG835 中把 Vivado 支持的 Tcl 命令按照 Category 分类,这些列于 Netlist 目录下的命令就是实现 ECO 需要用到的那些。

通常涉及到增减 cells 的 ECO 基本分为三步实现:首先用create_cell / create_net 等创建相关 cell 和/或 net,然后用 disconnect_net / connect_net 等命令修正因为 cell 和 net 的改动而影响到的连接关系,最后用 route_design 加选项完成局部布线。

不同的 Vivado 版本对此类 ECO 修改有稍许不同的限制,例如在 2014.1 之后的版本上,需要在改变 cell 的连接关系前先用 unplace_cell 将 cell 从当前的布局位置上释放,在完成新的连接关系后,再用 place_cell 放到新的布局位 置上。

具体操作上可以根据 Vivado 的提示或报错信息来改动具体的 Tcl 命令,但 操作思路和可用的命令相差无几。

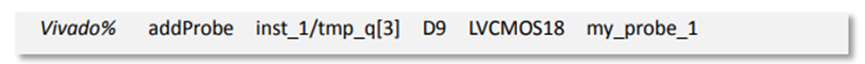

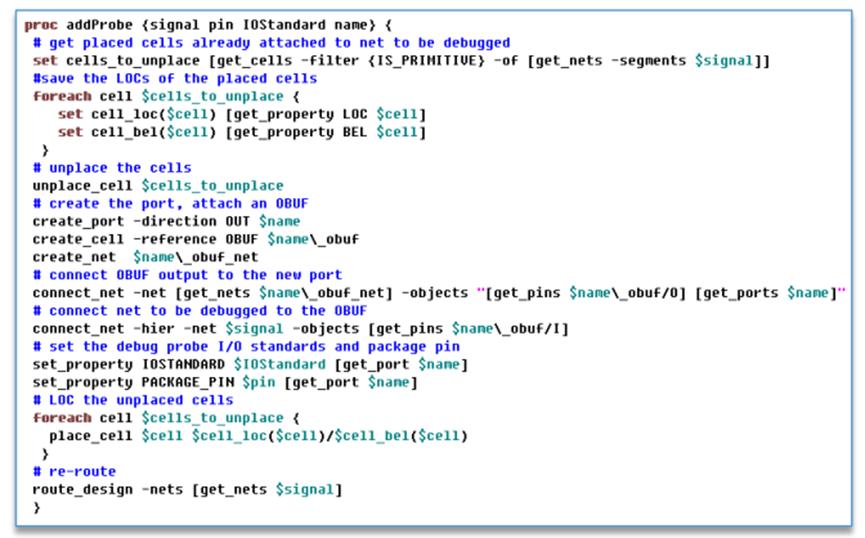

Add Probe

这是一个在 Vivaod 上实现 probe 功能的 Tcl 脚本,已经写成了 proc 子程序,简单易懂。可以直接调用,也可以做成 Vivado 的嵌入式扩展命令。调用其生成 probe 只需先 source 这个脚本,然后按照如下所示在 Tcl Console 中输入命令即可。

该脚本已经在 Vivado2014.3 和 2014.4 上测试过,一次只能完成一个 probe 的添加,而且必须按照上述顺 序输入信号名,管脚位置,电平标准和 probe 名。因为不具备预检功能,可能会碰到一些报错信息而导致无法继续。例如选择的信号是只存在于 SLICE 内部的 INTRASITE 时,则无法拉出到管脚。再比如输入命令时拼错了电平标准等,也会造成 Tcl 已经部分修改 Vivado 数据库而无法继续的问题。此时只能关闭已经打开的 DCP 并选择不保存而重新来过。

ECO 在 Vivado 上的发展

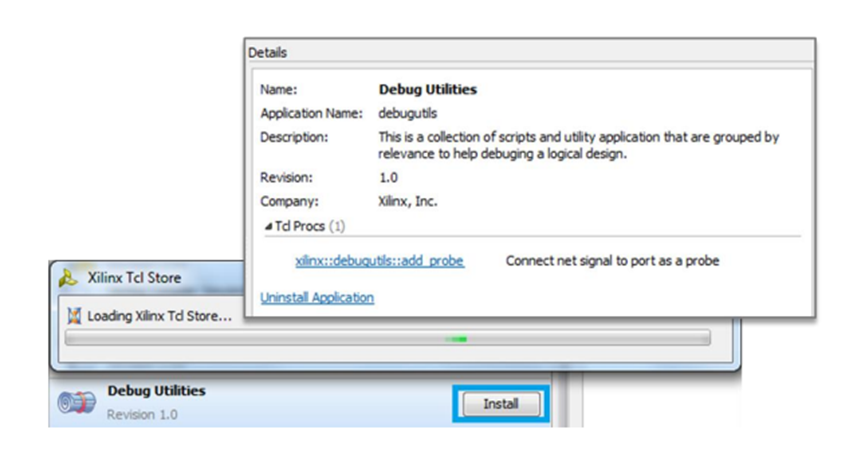

经过了两年多的发展,在 Vivado 上实现 ECO 已经有了多种方式,除了前面提到的图形化上那些可用的技巧,还有用户自定义的 Tcl 命令和脚本等。随着 Xilinx Tcl Store 的推出,用户可以像在 App Store 中下载使用 app 一样下载使用 Tcl 脚本,简化了 Tcl 在 Vivado 上应用的同时,进一步扩展了 Tcl 的深入、精细化使用,其 中就包括 Tcl 在 ECO 上的应用。

目前 Vivado 2014.4 版本上新增了很多有用的脚本。安装好 Vivado 后,只需打开 Tcl Store,找到 Debug Utilities,点击 Install 稍等片刻,即可看到一个 add_probe 的 Tcl proc 被安装到了你的 Vivado 中。

这个 add_probe 是在上述 addProbe 例子的基础上扩展而来,不仅可以新增 probe,而且可以改变现有 probe 连接的信号。此外,这个脚本采用了 argument 写法,点击程序可以看 help,所以不一定要按照顺序输入信号、电平标准等选项,输错也没有问题。另外增加了预检和纠错功能,碰到问题会报错退出而不会改变 Vivado 数据库,效率更高。

此外,Tcl Store 上还有很多其它好用的脚本,欢迎大家试用并反馈给我们宝贵意见。虽然里面关于ECO 的脚本还很少,但我们一直在补充。此外 Tcl Store 是一个基于 GitHub 的完全开源的环境,当然也欢迎大家上传自己手中有用的 Tcl 脚本,对其进行补充。

总体来说,ECO 是一个比较大的命题,因为牵扯到的改动需求太多,其实也很难限制在一个 GUI 界面中实现。这篇文章的目的就是为了让大家对在 FPGA 上实现 ECO 有个基本的认识,梳理看似复杂无序的流程,所谓观一叶而知秋,窥一斑而见全豹,希望能带给更多用户信心,用好 Vivado 其实一点都不难。

审核编辑:刘清

-

奇捷科技EasyAI ECO Suite即将发布2026-01-15 972

-

解析什么是DFT友好的功能ECO?2023-05-05 3191

-

什么是DFT友好的功能ECO呢?2023-03-06 3798

-

详细描述和解释GOF ECO每一个步骤的实现方法和注意事项2022-11-07 3326

-

详解Xilinx FPGA的ECO功能2022-08-02 5402

-

空调遥控器上的eco是什么意思2022-04-18 11358

-

自动ECO参考网表来自动修改实现网表2021-09-08 4513

-

ECO技术在SoC芯片设计中的应用2021-04-07 1981

-

使用ECO进行调试有哪些好处2018-11-29 4518

-

如何在Vivado中执行工程变更命令 (ECO)2018-11-21 5913

-

Uber联合创始人发行加密货币Eco 希望Eco能够复苏虚拟货币2018-03-03 2959

-

PADS使用ECO对比步骤2018-01-16 2299

-

汽车eco模式使用技巧_eco模式真能省油吗2017-12-14 30264

-

Vivado使用误区与进阶——在Vivado中实现ECO功能2017-11-18 5939

全部0条评论

快来发表一下你的评论吧 !