AMD全新Vitis HLS资源现已推出

描述

您是否担心 RTL 设计中的延迟?

您的设计是否有效并经过优化?

AMD Vitis HLS 可帮助您解决这些问题。

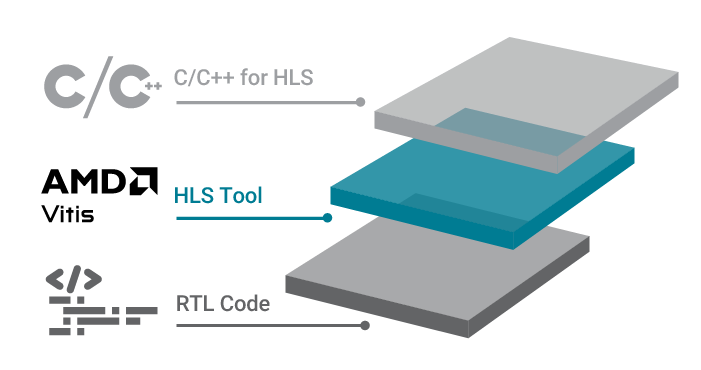

通过 Vitis HLS,您可将 C/C++ 函数综合到 RTL 中,从而轻松创建复杂设计算法。

AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

使用 Vitis HLS 流程,用户可针对 C 代码应用指令,创建专门用于所需实现方案的 RTL。

不仅可从 C 语言源代码创建多个设计架构,而且还可启用用于高质量 Correct-by-Construction RTL 的路径。

C 语言仿真可用于验证设计,支持比基于 RTL 的传统仿真更快的迭代。

Vitis HLS 工具具有一系列丰富的分析及调试工具,其可促进设计优化。

全新推出的Vitis HLS资源,具有以下特点:

较之传统的 RTL,Vitis HLS 可实现更快的设计验证和更高效的迭代

通过 Vitis HLS,开发者可使用 C/C++ 代码中的自动 pragma 推理、流水线循环和函数等高级功能来满足系统性能要求

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AMD Vitis AI 5.1测试版现已开放下载2025-11-08 1450

-

如何在Unified IDE中创建视觉库HLS组件2025-07-02 1683

-

使用AMD Vitis Unified IDE创建HLS组件2025-06-20 2554

-

如何使用AMD Vitis HLS创建HLS IP2025-06-13 2252

-

AMD Vitis Unified Software Platform 2024.2发布2024-11-27 1437

-

在Windows 10上创建并运行AMD Vitis™视觉库示例2024-05-08 2068

-

AMD-Xilinx的Vitis-HLS编译指示小结2023-12-31 2085

-

Vitis HLS移植指南2023-09-13 595

-

使用Vitis HLS创建属于自己的IP相关资料分享2022-09-09 5561

-

FPGA高层次综合HLS之Vitis HLS知识库简析2022-09-07 3857

-

Vitis HLS知识库总结2022-09-02 4962

-

Vitis HLS前端现已全面开源2022-08-03 1817

-

开启无限可能的世界:Vitis HLS 前端现已全面开源2022-08-02 1720

-

Vitis HLS工具简介及设计流程2022-05-25 3748

全部0条评论

快来发表一下你的评论吧 !