基于FPGA的数字电位器设计

描述

一、数字电位器简介

数字电位器是一种可由数字信号控制的电位器,当前使用范围十分广泛,区别于滑动、机械调节的电位器,而是属于集成电路,优点主要有:可以进行细调,调节精度高,无机械磨损,寿命高; 缺点:不能对阻值连续调整,只能按芯片位数的最小间隔调整。

数字电位器最终控制的是阻值的变化,依据此性能可以在不同的原理下,实现分压、电流控制、增益控制、信号控制、偏移调整等应用。

二、FPGA硬件设计

2.1 以AD5174BRMZ-10为例

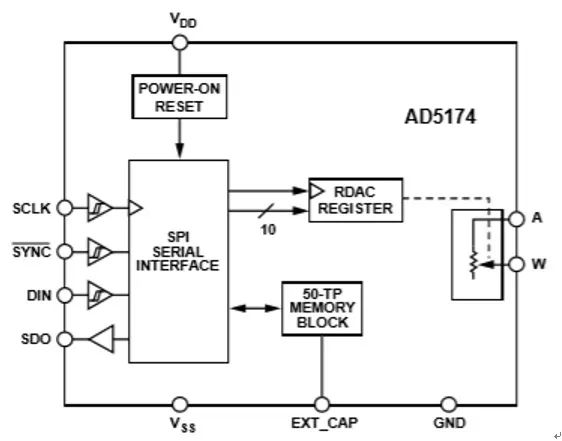

AD5174BRMZ-10是一款1024位的,10K数字电位器,SPI接口。 功能框图如下:

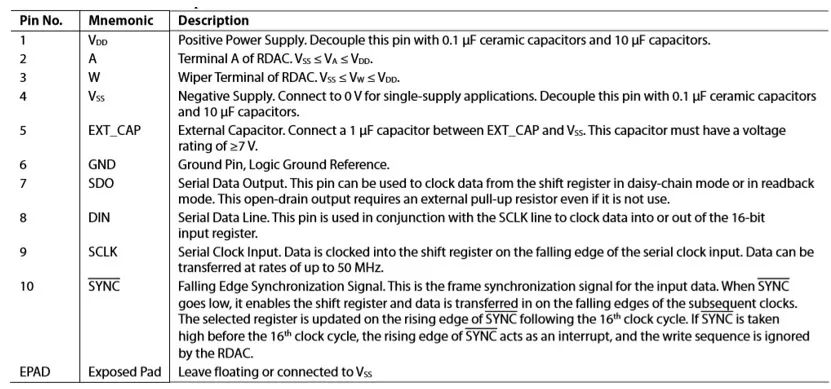

芯片各引脚功能介绍如下:

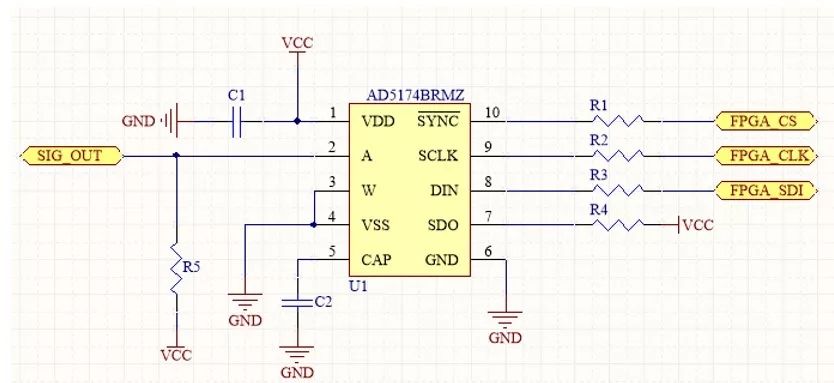

2.2 原理连接

右端3个信号连入到FPGA引脚,左端SIG_OUT是数字电位器电阻输出端。

三、FPGA代码设计

3.1 芯片手册代码使用信息汇总

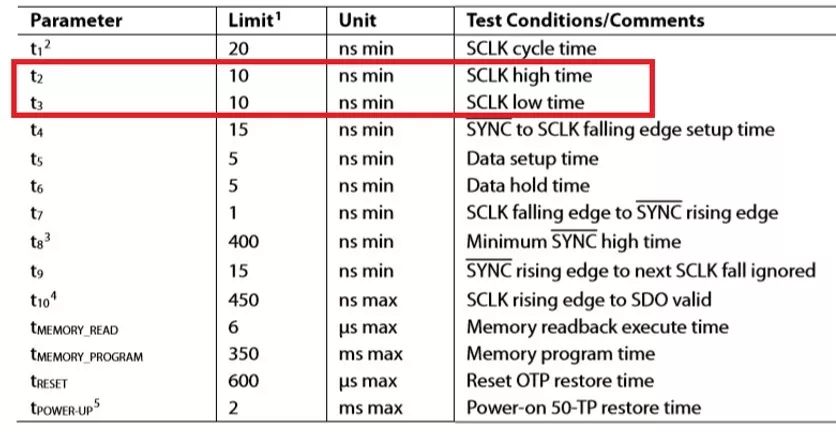

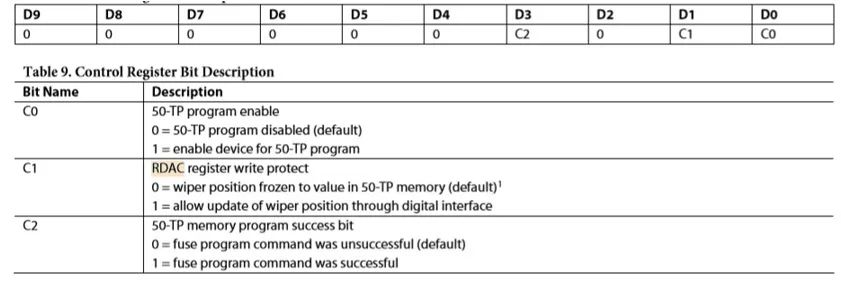

由数字电位器芯片时序要求中下图红框内需求,可得FPGA的PLL最小时钟需要在100MHz。

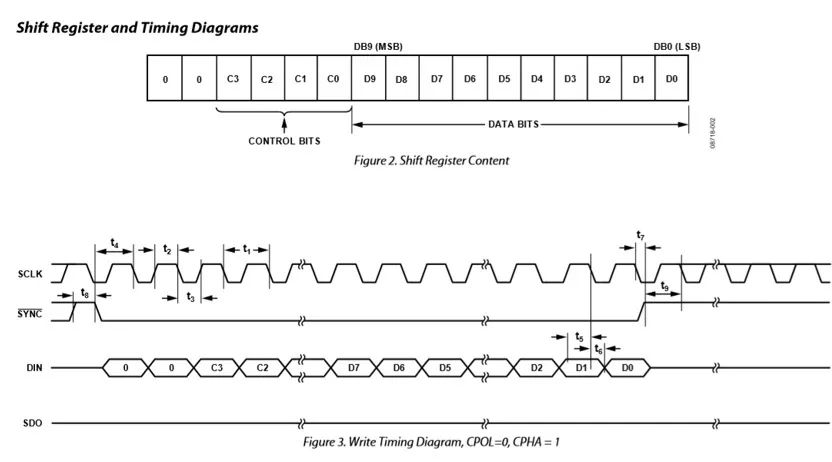

由芯片寄存器内容要求,可知每次需要在SPI中写入16位数据,分别是:00+控制位(4bits)+数据位(10bits)

由芯片写时序框图中,可知,SPI数据在时钟下降沿写入。

芯片SPI读的功能与实现,本文未涉及。

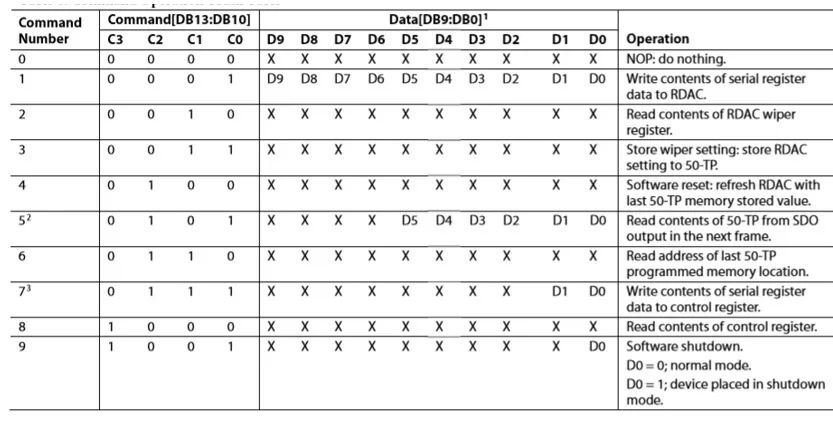

由命令真值表,可得各功能对命令的操作,本文主要介绍对数字电位器的写入操作,所以使用以下两条命令:

第1条:串行数据写入到RDAC寄存器,用于控制芯片电阻值输出。

第7条:串行数据写入到控制寄存器,对芯片进行设置。

由控制寄存器位映射,可得相应位的设置功能。

3.2 FPGA的SPI数据设计

先进行BLOCK的设计,输入部分根据实际应用的平台工程而定,输出则是与数字电位器连接的SPI口。

时钟的输入各位可以定义constant,std_logic_vector(71 downto 0),共72位,其中包括:

起始00(2bits)+控制字时钟(32bits)+分隔位(4bits)+设置数据时钟(32bits)+结束00(2bits)

例:001010101010101010101010101010101000001010101010101010101010101010101000

片选相应各位同时钟定义,在起始、分隔、结束时为高,其它数据传输为有效低电平

例:100000000000000000000000000000000011100000000000000000000000000000000011

数据输入定义同时钟定义,详细如下:

控制字输入36位:

起始00(2bits)+ 补充两位0(4bits)+控制字0111(8bits)+ 10位数据(20bits)+结束00(2bits)

此处注意,之所以每位数据,在代码中用了2个bits,是为满足FPGA模拟出的时钟高低电平对应的数据都有保持。

例:000000001111110000000000000000111100

数据输入36位:

分隔无效位(6bits)+控制字0001(8bits)+10位数据(20bits)+结束00(2bits)

例:00000000000011“R9R9R8R8R7R7R6R5R5R4R4R3R3R2R1R1R0R0”&“00”

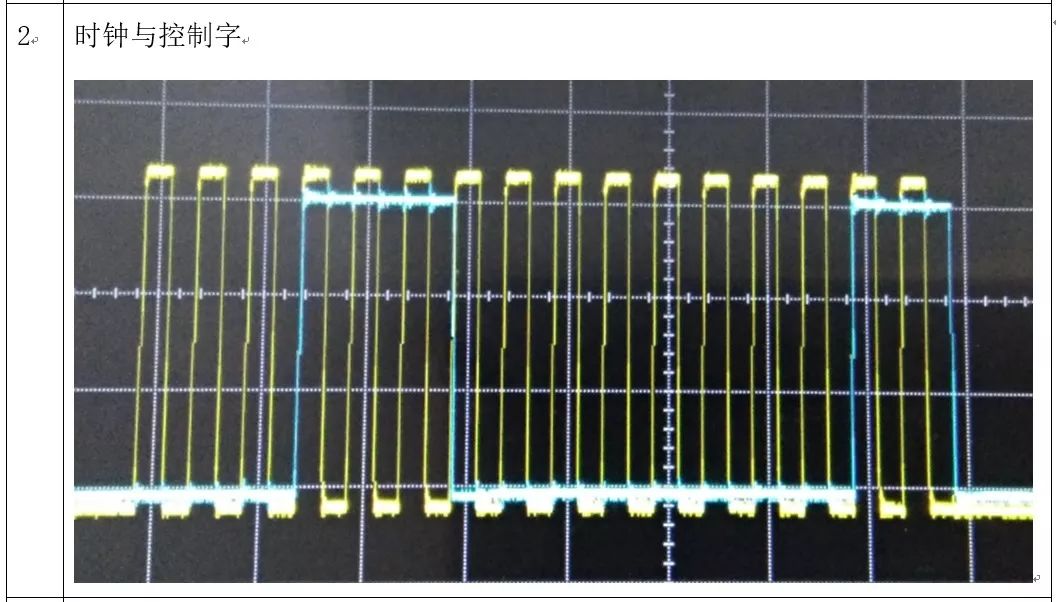

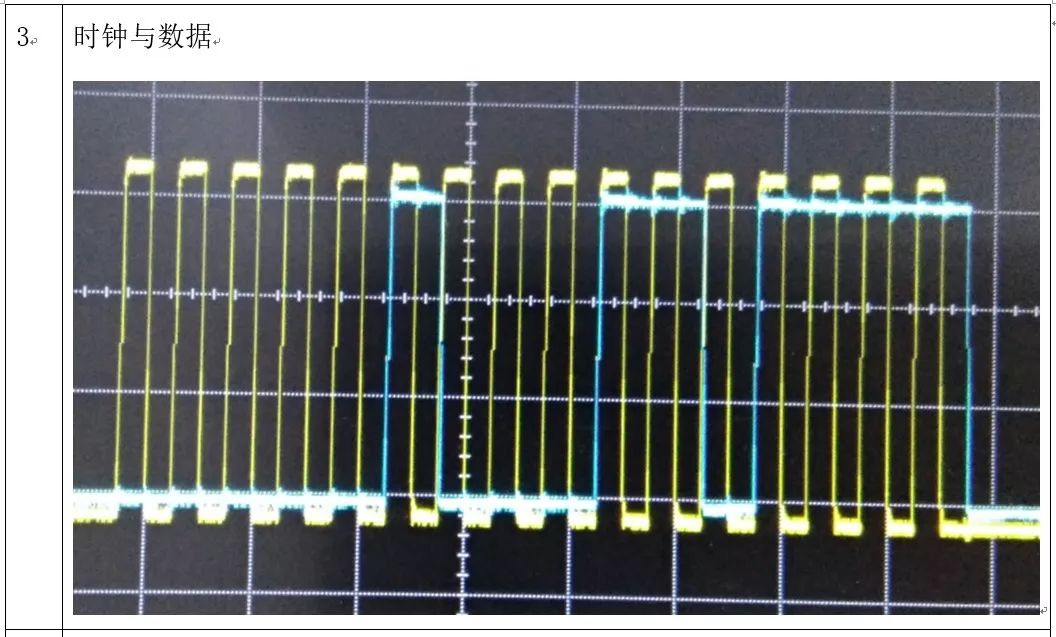

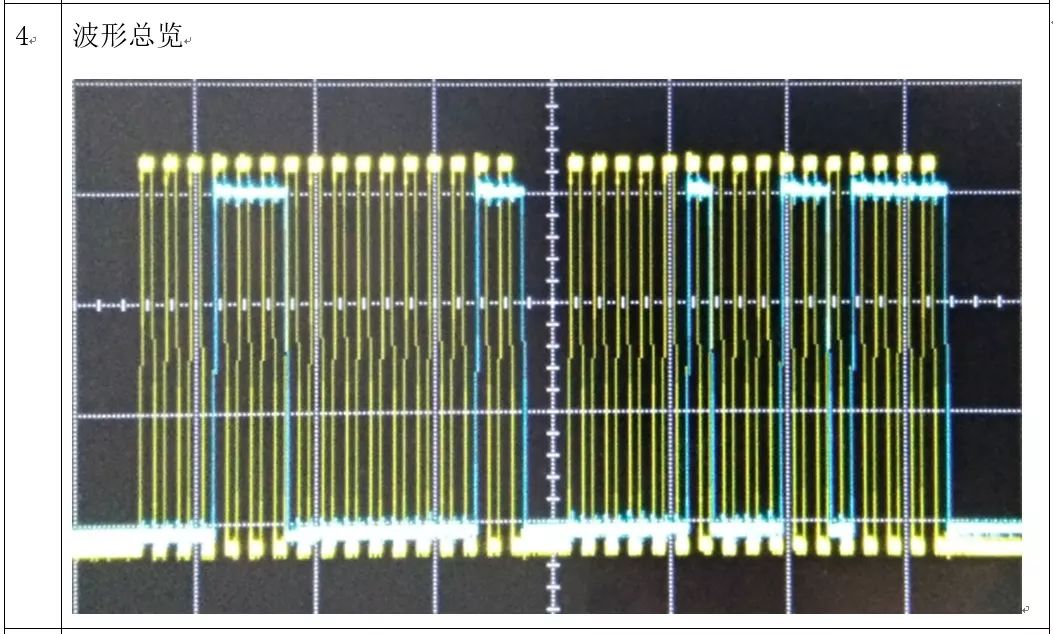

3.3 波形测量

3.4 验证

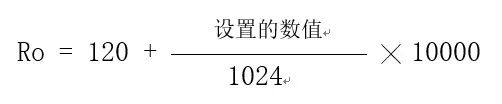

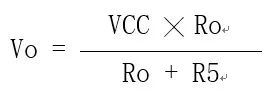

根据数字输入数据,结合原理分压情况,可得理论值,与实际测量比较可以进行确认。 需要注意的事,在0标度情况下,数字电位器AD5174BRMZ-10有120Ω的电阻限制。

数字电位器输出电阻Ro计算公式如下:

输出电压Vo的计算公式如下:

-

数字电位器的优势与应用 电位器的调节方法和技巧2024-12-03 3553

-

什么是数字电位器?2021-04-08 2990

-

数字电位器2018-03-28 5174

-

数字电位器怎么选型_数字电位器选型指南2018-01-23 10639

-

数字电位器的应用2009-11-16 788

-

理解和应用数字电位器2009-10-23 739

-

用数字电位器替代机械电位器2008-11-27 3360

全部0条评论

快来发表一下你的评论吧 !