硬件设计案例分析之常用存储器FLASH与DDR的设计

电子说

描述

常用电路模块的布局布线原则

常用存储器设计

*SDRAM

*FLASH

*DDR

*DDR2

*DDR3

*QDR

1、FLASH的设计

FLASH(闪速存储器)-速率较低

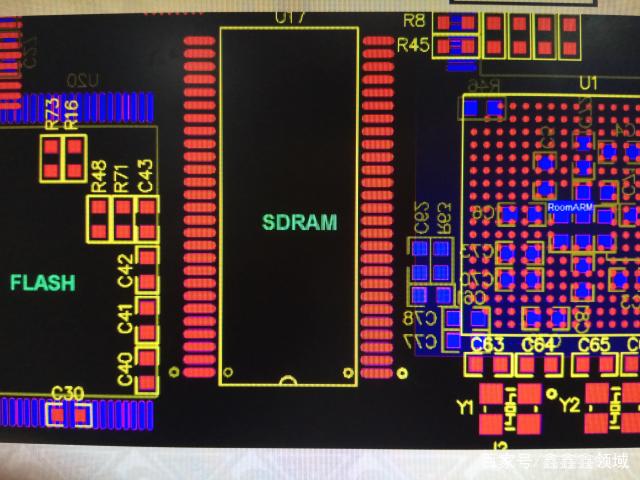

布局:一般采用菊花链

BGA->SDRAM->FLASH

(FLASH和SDRAM推荐距离为500~1000MIL),如下图:

2、FLASH的设计

布线(如图)

3W原则

等长范围:+-100MIL

特性阻抗:50欧

3、DDR的设计

管脚定义解释(如下图)

4、DDR的布局

布局原则:靠近CPU摆放

DDR X1片时,采用点对点的布局方式,

DDR到CPU的推荐的中心距离:

当中间无排阻时:900~1000MIL;

当中间有排阻时:1000~1300MIL。

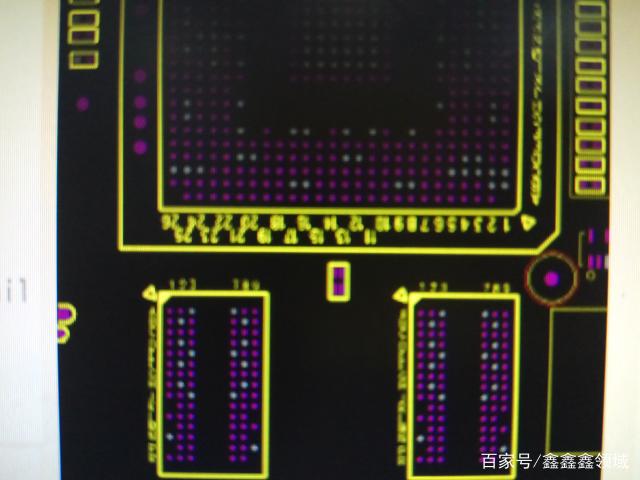

DDR X2片时,相对于CPU严格对称,如下图:

VREF电容的位置,如下图:

5、DDR的保护区域

DDR2保护区域(KEEPOUT REGION):DDR2内存组,所有同DDR相关的阻容电路,一直向CPU方向延伸至CPU的DDR控制器,称为DDR保护区域(DDR KEEPOUT REGION)。这个区域里需要满足一下条件:

A)不得出现与DDR无关的信号;

B)必须提供完整的地平面(信号线下方地平面不得中断);

C)必须提供完整的VCC_1V8电源平面(信号线下方电源平面不得中断)。

如下图:

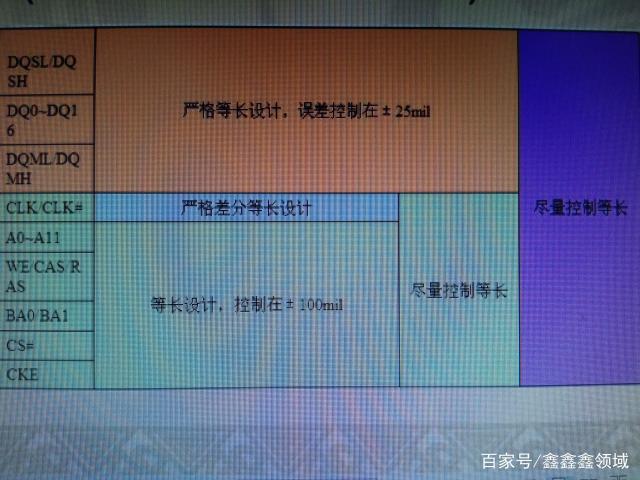

6、DDR的布线

特性阻抗:单端50欧,差分100欧;

数据线每10根尽量走在同一层;

信号线的间距满足3W原则

数据线、地址(控制)线、时钟线之间的距离保持20MIL以上或者至少3W

完整的参考平面

VREF电源走线推荐>=20~30mil

误差范围:

差分对误差严格控制在5MIL;

数据线误差范围控制在+/-25MIL;

地址线误差范围控制在+/-100MIL;

7、DDR的时序设计

DDR(采用树形或者星形拓扑)如下图:

-

求助 数据存储器 FLASH程序存储器 FLASH数据存储器的区别2011-11-29 7193

-

未来DDR4、NAND Flash存储器芯片该如何发展2021-03-12 2880

-

单板硬件设计:存储器( NAND FLASH)2023-05-19 1098

-

基于ColdFire MCF5249的Flash存储器扩展技2009-08-29 1070

-

Flash存储器的内建自测试设计2010-07-31 1130

-

Flash存储器概述2010-11-11 5452

-

flash存储器的类型2017-10-11 9253

-

基于MSP430功能模块详解系列之——FLASH存储器2017-10-12 1183

-

flash存储器的读写原理及次数2017-10-13 22641

-

DRAM、NAND FLASH、NOR FLASH三大存储器分析2018-04-09 114439

-

介绍DRAM、FLASH和DDR技术分析和对比2019-02-04 9812

-

PCB的常用存储器设计的详细资料说明2019-07-29 1588

-

NAND Flash和NOR Flash存储器的区别2023-09-27 2916

-

EEPROM与Flash存储器的区别2024-05-23 11792

-

DDR存储器接口的硬件和布局设计考虑因素2024-09-11 608

全部0条评论

快来发表一下你的评论吧 !