DDS的基本原理是什么?DDS的性能分析

电子说

描述

1、为什么要用DDS

优点:切换速度快、频率分辨率高、相位连续等优点,易于集成,功耗较低。输出信号的相对带宽较宽,一般为参考信号的三分之一以上。小步进捷变频的频率源的实现,一般采用DDS方案实现频率源的小步进。

缺点:DDS输出频率的限制导致其不能实现较为宽带的频率源。输出频率较低,一般为MHz数量级。DDS在部分频段杂散大,从而影响频率源的性能。DDS的最大劣势也就在于其输出较多杂散。

DDS基本原理

2、DDS基本原理

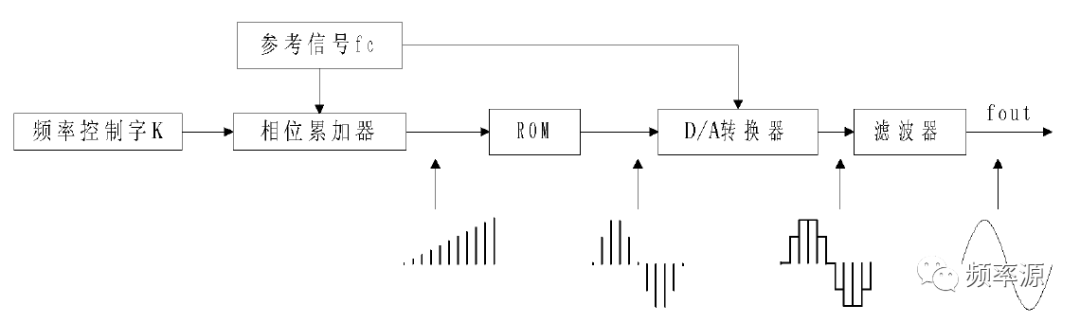

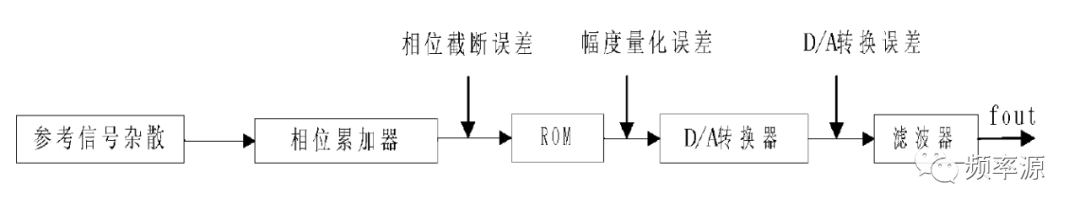

DDS是通过数字的方式构建幅值相位之间的关系,通过查表读取对应离散的相位幅值数据,后经过数模转换输出需要的模拟正弦信号。常规的DDS是由相位累加器、波形存储器、D/A转换器以及滤波器组成。

一个周期内正弦波的幅度随时间的变化并不是线性的,但它的相位随时间是线性变化的。在一个周期内相位与幅度是一一对应的,所以将原有数字正弦信号进行重新组合产生新的正弦信号。

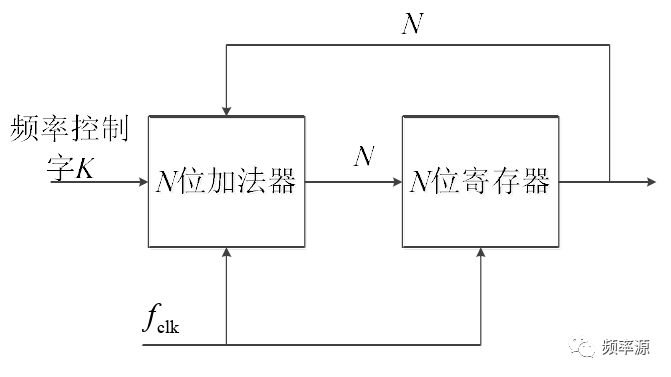

相位累加器是系统的核心,它控制了系统的最终输出频率,它由一个加法器和一个寄存器组成。波形存储器以相位码为地址存储了正弦波形的幅值码,相当于正弦函数的相位幅值对照表,根据相位码ROM读取相应地幅值码。

相位累加器的输出的相位码作为地址信息不断对ROM进行寻址,ROM将相位信息转化为对应的幅值给到A/D转换器。A/D转化器将传输的二进制数字信号转化为模拟信号,经滤波器滤波后,形成所需频率的正弦信号。

2.1 相位累加器

结构中包含一个N位加法器和一个N位寄存器。每当一个参考时钟脉冲触发,加法器就会将输入频率控制字与寄存器输出的寻址数据相加,并把相加后的结果送入寄存器进行数据更新。一个N位的相位累加器就可以存储2^N^个相位点。相位累加器的溢出频率就是DDS输出信号的信号频率。

2.2、波形存储器

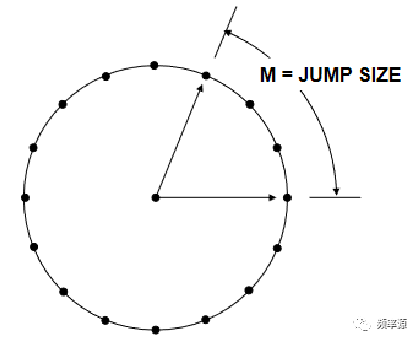

频率控制字K则是这个寻址序列的“步进”,其决定了在DDS输出波形的一个周期中包含存储器中幅值数据的个数。频率控制字K越高,一个周期中包含的幅值数据越少,DDS输出波形的频率越高,波形的质量越差。图中M=K

2.3、数模转换器D/A

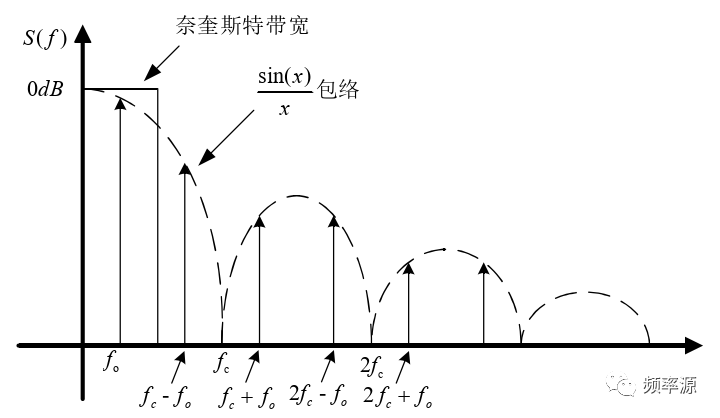

数模转换器就是将数字信号转化为模拟信号。D/A转换器输出的阶梯波,由于不是标准的正弦波,除开产生所需要的主频外,还会包含谐波,为了抑制这些谐波和使阶梯波更平滑,需要在输出前加滤波器。

2.4、输出频率

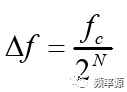

其中N为频率控制字的长度,K为频率控制字,fc为参考时钟的频率,f0为输出时钟的频率。DDS实际上完成了对参考信号fc的分频过程,分频值为2 ^N^ /K。

DDS的性能分析

3.1、频率分辨率

理想的DDS系统,所以默认频率控制字长度与波形存储器、D/A转换器位宽相同,均取值为N。而在现实设计中,由于波形存储器存储位数有限、DAC分辨率有限等原因使得这些位宽并不相同,引起截断误差,这也是DDS杂散的来源。目前的频率控制字长度可达48位,其频率分辨力可以轻松地达到Hz数量级。

3.2、频率切换速度

DDS是一个开环系统,与锁相环系统相比的频率切换时间极短,与频谱纯度和频率分辨率互不相干,其频率切换时间可以达到纳秒级别。

3.3、输出频率范围

根据奈奎斯特抽样定理,在DDS中,直接合成的离散信号的抽样频率为参考时钟频率,要想无失真的将数字离散信号转换为所需频率的模拟信号,则DDS的参考时钟频率应大于等于输出频率的两倍。为了保证输出信号的质量,DDS的输出信号一般要小于参考时钟频率的五分之二。

虽然DDS的相对输出带宽较宽,能够达到参考频率的40%,但同时参考频率值也限制了的输出上限。目前,较长使用的芯片的最高参考频率可达1GHz,输出频率最高可为400MHz。

3.4、杂散分析

独立于输出信号存在的无用谱称为杂散。它们一般对称的出现在频谱上,其幅度与噪声相比较高。下图中理想离散信号的频谱相比,实际中输出的频谱中存在更多的杂散。参考时钟中存在的杂散,相位截断误差,幅度量化误差以及转换误差,都会给的输出信号带来杂散。

除上述四种杂散外影响系统输出杂散的因素还有电路板的布线有关。错误的布线会给系统带来较多的杂散,使其输出性能下降。

3.5相位噪声分析

参考时钟的相位噪声对输出信号的相位噪声影响较大。通常选用相位噪声很低的晶振作为的参考信号。

-

DDS基本原理及性能特点2011-07-13 7569

-

DDS工作原理是?用DDS芯片AD9858宽带雷达信号源要设计最佳?2021-04-06 2812

-

DDS基本原理及性能特点,实现DDS的技术方案有哪几种?2021-04-07 2792

-

如何采用VHDL硬件实现DDS的优化设计与实现?2021-04-12 1212

-

请问怎样去设计一款DDS芯片?2021-04-14 1927

-

基于DDS技术的任意波形发生器是怎样设计的?2021-04-30 1747

-

怎么实现基于FPGA+DDS的正弦信号发生器的设计?2021-05-11 1764

-

dds的工作原理2008-04-03 9636

-

DDS,什么是DDS,DDS的结构2009-09-03 5102

-

DDS是什么意思,DDS结构,DDS原理是什么2010-03-08 47963

-

基于FPGA的DDS杂散分析及抑制方法2012-11-26 888

-

STM32的AD9854 DDS模块调试总结2018-05-16 20239

-

DDS基本原理与工程应用2019-11-13 3606

-

DDS的基本原理 :相位累加器、存储的波形表、高速DAC2020-09-24 17857

-

MT-085: 直接数字频率合成(DDS)基本原理2021-03-21 1227

全部0条评论

快来发表一下你的评论吧 !