简易运放构成反相输入的迟滞比较器设计

描述

简易运放构成反相输入的迟滞比较器

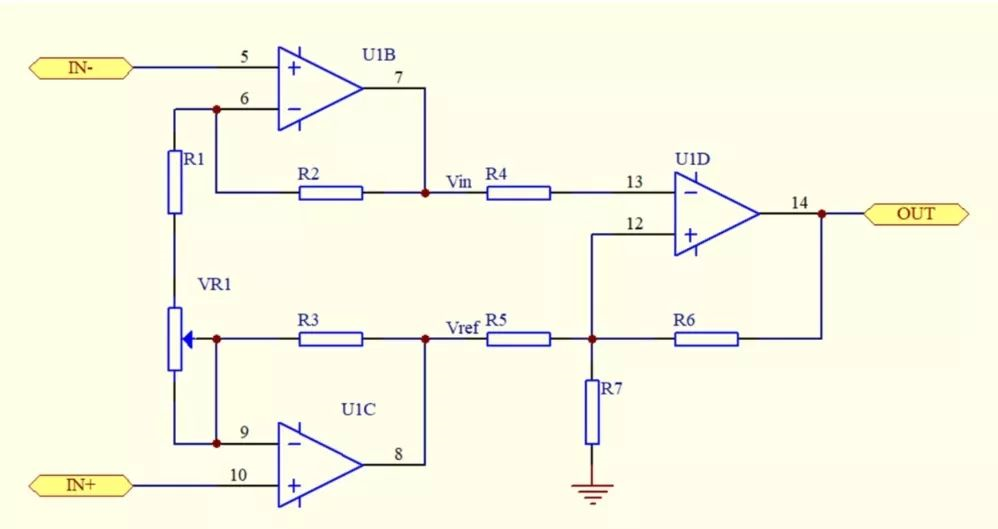

一、电路原理图

二、原理分析

U1B与U1C构成此电路的输入部分,R2=R3,R4=R5,这是一个增益可调的差分输入端,对于差分信号有放大作用,也可以当作仪表放大的输入,由于输入的信号都加到了R2,R1,VR1,R3这几个电阻网络两端,则闭环增益可以通过可调电阻器VR1进行调整,增益总电阻RG是由R1和VR1共同决定的。

当共模信号进入输入级,RG两端具有相同的电位,则RG上没有电流通过,对于U1B和U1C,起到跟随器功能,对信号并没有放大,且提高了输入阻抗,而差分信号按照不同RG构成的系数被放大了,这就是说明此电路具有较大的共模抑制比。

增益电阻:

RG = R1 + VR1

输入级每个运放的放大倍数:

A = 1 + 2* (R2/RG)

U1D是此电路的输出部分, 是带有正反馈的单限比较器;普通的单限比较器,在输入信号处于门限值附近受到干扰时,输出也同时会发生微小变化,这就造成信号的不稳定,它是在比较器的基础上增加了正反馈,实现了反相输入的迟滞比较,可以避免由于输入端的抖动造成输出的不稳定,另外,正反馈的引入可以加速比较器的响应速度。

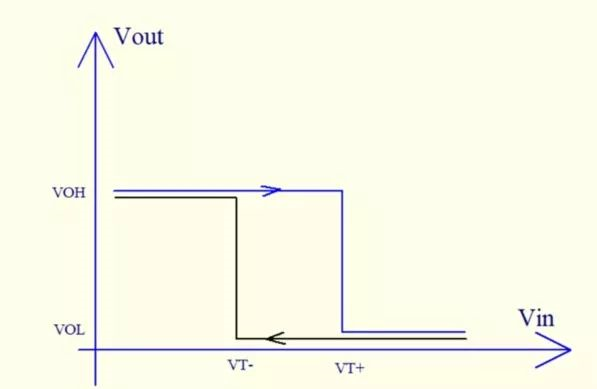

见上图是迟滞比较的电压输出过程。

当Vin增大,超过上限门值VT+时,输出电压Vout跳变为VOL;当输入电压减小,低于下限门值VT-时,输出电压Vout跳变为VOH。因此,当输入电压被干扰时,干扰电压不超过VT+与VT-的差值时,输出是稳定的。

此电路笔者在相关设计中多次应用于电桥接口类的传感器信号输入端,经验证,性能稳定、可靠,大家可以放心借用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

具有迟滞电路的反相比较器2024-09-02 387

-

迟滞比较器门限电压计算公式2023-12-28 7580

-

运放作为比较器怎么连接2023-12-19 4367

-

比较器和运放的区别 比较器和运放的功能是否相同,能相互代替?2023-11-22 2520

-

运放的同相输入端和反相输入端之间的电阻怎样设置?2023-10-26 8233

-

运放比较器电路及原理2023-08-27 8434

-

基于集成运放构成的窗口电压比较器和滞回电压比较器设计2023-02-08 8843

-

运算放大器作电压比较器的分析2021-12-10 3982

-

电压比较器的工作原理,电压比较器与运放的差异2021-01-20 5708

-

单运放构成的振动报警电路2020-09-18 4053

-

典型迟滞比较器电路图大全(四款典型迟滞比较器电路设计原理图详解)2018-03-26 136221

-

同相迟滞比较器和反相迟滞比较器的区别2016-10-21 17430

-

运放和比较器的区别2009-03-11 3293

全部0条评论

快来发表一下你的评论吧 !