液相法、3C-SiC!中科院又取得新成果

描述

中科院物理所陈小龙团队又一次公布他们在SiC方面的研发新成果:

4月18日,中科院物理所在期刊上发表了关于采用液相法生长3C-SiC衬底的技术文献。

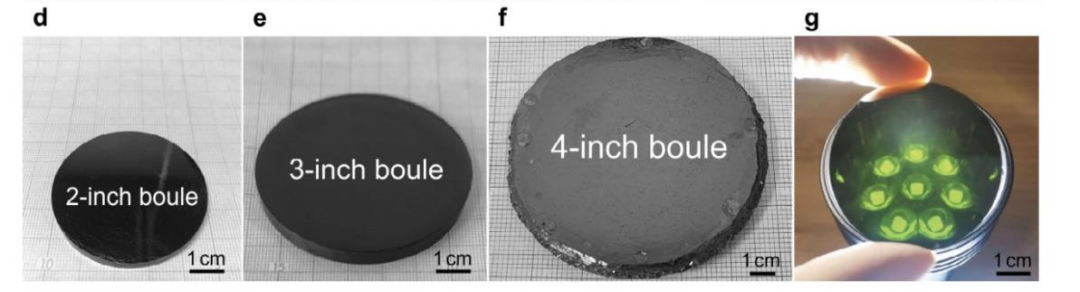

文献提到,该团队是通过在4H-SiC衬底上生长3C-SiC单晶,技术成果超出了以往理论预期,通过这项技术,他们能够持续稳定地生长高质量和大尺寸的3C-SiC晶体——直径为2~4英寸,厚度为4.0~10毫米。

该团队认为,该技术拓宽了异质晶体生长的机制,并为3C-SiC晶体的大规模生产提供了可行的途径,未来3C-SiC功率器件性能有望比目前主流的4H-SiC更好。

液相法生长3C-SiC 4英寸、10mm

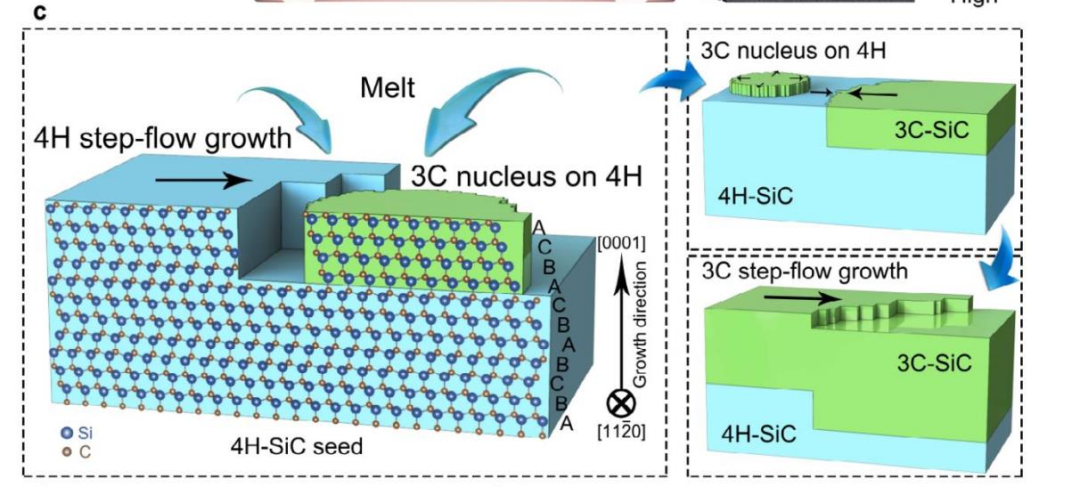

该团队开发了一个生长3C-SiC的液相TSSG长晶设备,其生长过程是这样的:首先,在高温石墨坩埚区域中溶解C粉;然后在对流作用下,将C粉从高温区输送到低温区;最后在低温籽晶上进行3C-SiC结晶。

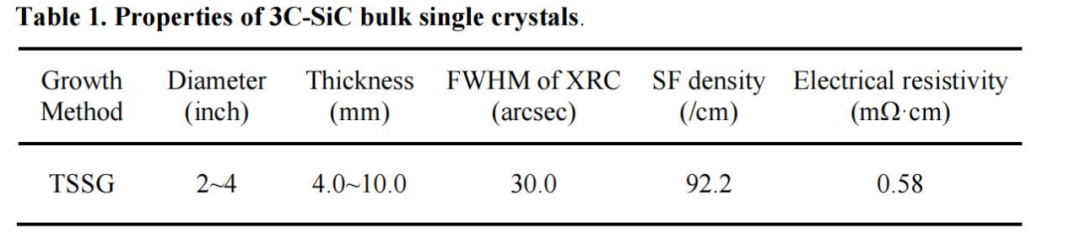

该技术的相关数据汇总如下:晶圆尺寸为2-4英寸、晶体厚度为4-10mm。

这种3C-SiC晶体的液相TSSG生长模型示意图如下:

质量方面,经过测量,所生长的3C-SiC晶体(111)面半峰全宽(FWHM)为28.8至32.4弧秒,平均为30.0弧秒,整体晶圆非常均匀。

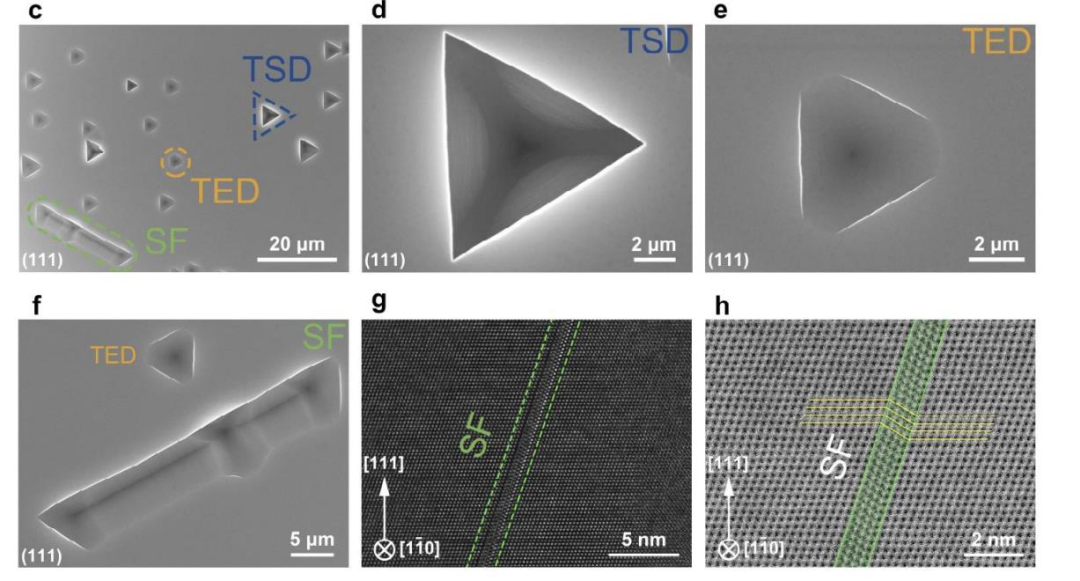

从3C-SiC的切片上看,典型的三角形凹坑大小约为5微米,可能来自螺纹位错(TSDs)和螺纹边缘位错(TEDs)的密度分别约为4.3×104/cm2和13.9×104/cm2,并且没有观察到在3C-SiC中常见的双定位边界(DPBs)。

3C-SiC“闪光点”有哪些?

其实,业界很早就进行3C-SiC的研发,在1987年左右,日本电工实验室开发出第一款基于硅衬底的3C-SiC横向MOSFET。

但是由于种种原因(下面展开讲),3C-SiC“沉寂”了,发展速度远不如4H-SiC。但是最近几年,3C-SiC块材和硅基3C-SiC取得了巨大进展,业界的关注度又重新回来了。

我们先来看看3C-SiC的优势。

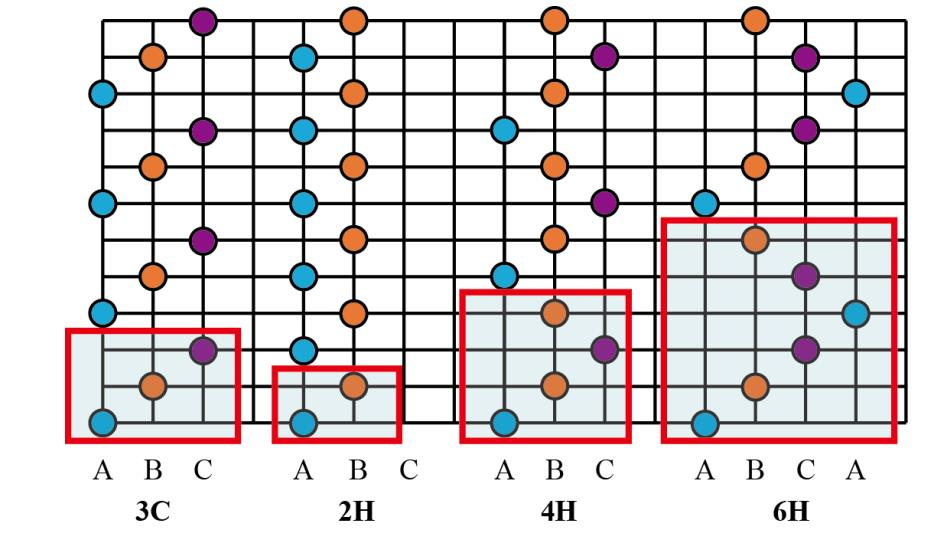

目前,SiC材料已知的晶体结构有250多种,主要类型有六方体(2H-SiC、4H-SiC、6H-SiC)和立方体3C-SiC等。

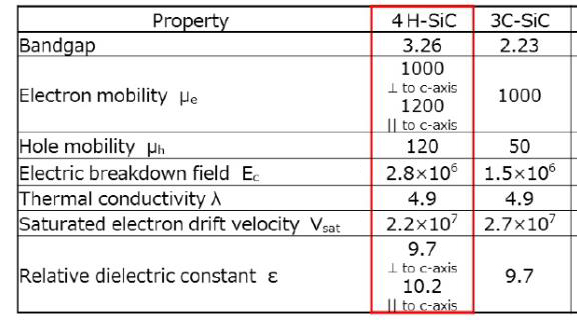

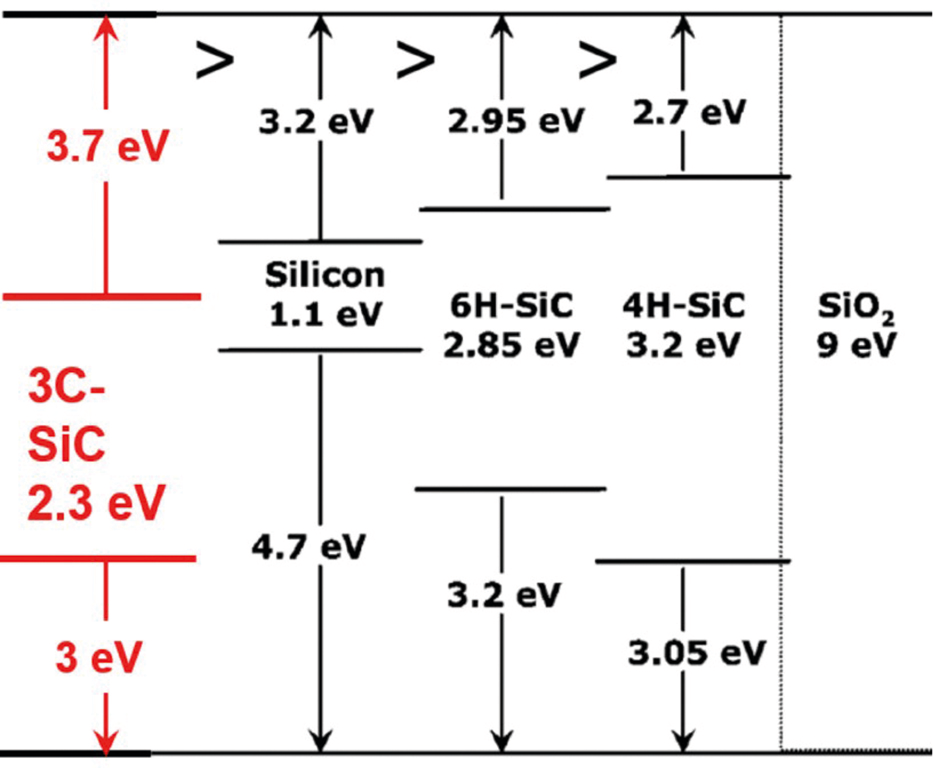

实际上,如果从材料特性来看,相比4H-SiC晶型材料,3C-SiC在禁带宽度、击穿场强等各方面都处于劣势,这也是为什么主流的商用器件都是在4H-SiC上制造的原因之一。但是,3C-SiC被认为是“明日之星”,前景备受看好,这又是为什么?

首先是电子迁移率。

据报道,硅基3C-SiC MOSFET的n沟道迁移率范围为100-370cm2/V·s。而横向4H-SiC MOSFET通常为20-40cm2/V·s,沟槽器件为6-90 cm2/V·s。京都大学通过氮气钝化在A面上创建SiC MOSFET,将沟道迁移率提升到131cm2/V·s,但也低于硅基3C-SiC器件。

其次是可靠性。

目前,SiC MOSFET核心技术瓶颈集中在栅氧层界面质量差,不仅沟道迁移率低,而且会影响阈值电压稳定性,栅极氧化物在高温下还存在失效的弱点。而3C-SiC和绝缘氧化物栅之间的界面陷阱浓度低得多,有助于制造可靠和长寿命的器件。

3C-SiC势垒高度为3.7 eV,该值远大于硅和4H-SiC,因此在栅极驱动电路漏电流相同时,3C-SiC MOSFET内的电场比4H-SiC高两到三倍。因此,3C-SiC 沟槽功率 MOSFET 的降额要求远没有4H-SiC产品严格。

第三是加工。

4H-SiC和GaN的加工与传统硅完全不同,更具挑战性。相比之下,低能禁带宽度的3C-SiC更接近硅,这在加工成器件时具有许多好处。3C-SiC难点在哪?液相法生长有何意义?

前面提到,全球研究人员对3C-SiC进行了几十年的努力,但产业化仍然是一个挑战。我们来看看3C-SiC的难点。

首先,3C-SiC晶体生长较难。

目前,六方碳化硅(4H、6H)晶体的生长技术已经成熟,高质量的衬底已经完全商业化,但是体块3C-SiC单晶的生长依然滞后。

一是生长方法不太合适,传统PVT法是生长4H-SiC和6H-SiC晶体的成熟技术,但不适用于生长3C-SiC晶体,因为在它需要更高的Si/C比率,即使采用改良式密闭空间PVT方法,晶体厚度也非常有限,并不适用于大规模生产。

二是在实际生产中,3C-SiC并不稳定,在高于1900-2000℃高温下会转变为六方SiC多晶。正是如此,相较之下,4H-SiC更具商业可行性,相较于6H-SiC,4H-SiC还具有较高的临界电场强度和高电子迁移速率,成为了制作功率器件的首选。

其次,硅基3C-SiC薄膜问题多多。

体块3C-SiC晶体生长路不通,为此,大部分的研发都转向了在硅衬底上进行3C-SiC薄膜沉积,然后再加工成器件。但这种方式存在几个问题需要克服。

一是会存在巨大的晶格失配(约19%)和热膨胀失配(约8%),从而导致缺陷密度过高,大大恶化了器件的性能。试验结果表明,在硅衬底上生长的3C-SiC缺陷密度达到103-104cm-2。

尽管α-SiC在晶格参数、热膨胀系数和化学相容性方面和3C-SiC匹配性非常好,是非常理想的制备3C-SiC的衬底。然而α-SiC/3C-SiC存在双定位晶界(Double positioning boundaries,DPBs)结构缺陷的问题,它与杂质相互作用会导致肖特基接触不良行为。因此,制备3C-SiC晶体的首要问题是减少α-SiC的DPBs。

二是硅基3C-SiC难以实现选择性掺杂。高杂质掺杂对于 3C-SiC 功率器件中的低欧姆接触和薄层电阻是必要的。在1800 °C以下,SiC掺杂扩散率通常较低,所以才需要离子注入,注入后采用高温退火 (PIA) 来修复晶格损伤并将掺杂剂激活。SiC PIA需要极高的温度,n型SiC通常高于1400 °C,p型需要更高的温度 (>1600 °C)。而硅基3C-SiC的激活退火温度通常被限制在 1412 °C(硅熔点)。

三是硅基3C-SiC器件加工的主要挑战之一是实现优质整流接触。硅基3C-SiC的肖特基势垒高度(SBH) 实验值通常低于1eV,远低于肖特基-莫特理论值。

所以,相比硅基3C-SiC,体块3C-SiC晶体更具潜在优点,主要包括离子注入和金属化等加工,而且单晶衬底还能够通过调整外延层厚度来实现更多器件耐压操作。

为此,据陈小龙团队的文献介绍,他们改变思路,转而采用TSSG液相法来生长3C-SiC单晶,这主要是基于2个方面的考虑:

首先,与PVT法相比,TSSG方法可以更容易地调整SiC和熔体之间的界面能量(通过改变它们的化学成分)。

其次,该团队在2021年就已经通过TSSG成功获得大于4英寸的4H-SiC晶体(1700~1800℃)。而他们这次的研发工作,证明了TSSG策略是行之有效的——成功生长了直径4英寸、厚度4-10毫米的大尺寸3C-SiC晶体。

那么,假设未来液相法实现了3C-SiC单晶的大规模制造,会有哪些商业意义?

首先,碳化硅器件的制造成本能够得到大幅降低,采用液相法理论上,晶体缺陷更少,根据中科院物理研究所研究员陈小龙此前的观点,液相法生长碳化硅的“最重要的一个好处就是晶体良率比较高,相当于变相地降低了每一片的成本”。

与此同时,3C-SiC的加工难度与硅类似,可以减少加工成本。

其次,成本更低的3C-SiC,未来将对600V-1200V电压段的功率器件市场产生巨大影响。

审核编辑 :李倩

-

中科院发布“香山”与“傲来”两项开源处理器芯片2023-05-28 6189

-

半导体材料“3C-SiC”的晶体纯度和质量进展2022-12-21 3897

-

3C-SiC有望PK单晶金刚石,成为高导热材料的选择2022-12-15 3168

-

中科院3D打印机CEST400|国产工业级3D打印机2018-08-10 3266

-

中科院的重大科技成果进入井喷期2018-01-31 3441

-

中科院WSN讲义 时间同步2017-10-24 1575

-

数字图像处理_中科院课件2017-02-07 1025

-

中科院_遥感课件及资料32016-05-05 598

-

中科院深耕网络摄像机领域2015-02-05 5282

-

Banana PI开源项目与中科院先研院举行开源硬件介绍交流活动2014-08-09 5440

-

中科院剖析 LED怎样克服困难2012-07-18 8434

-

中科院电子技术考研真题2011-08-07 4080

-

C++课件及范例代码(中科院研究生用)2008-10-07 803

全部0条评论

快来发表一下你的评论吧 !