FPGA上可以用一个比较器实现ADC的功能?1

电子说

描述

- FPGA的使用

- ADC的原理及构成

- PWM的产生

- 比较器的应用

- 数字滤波器的使用

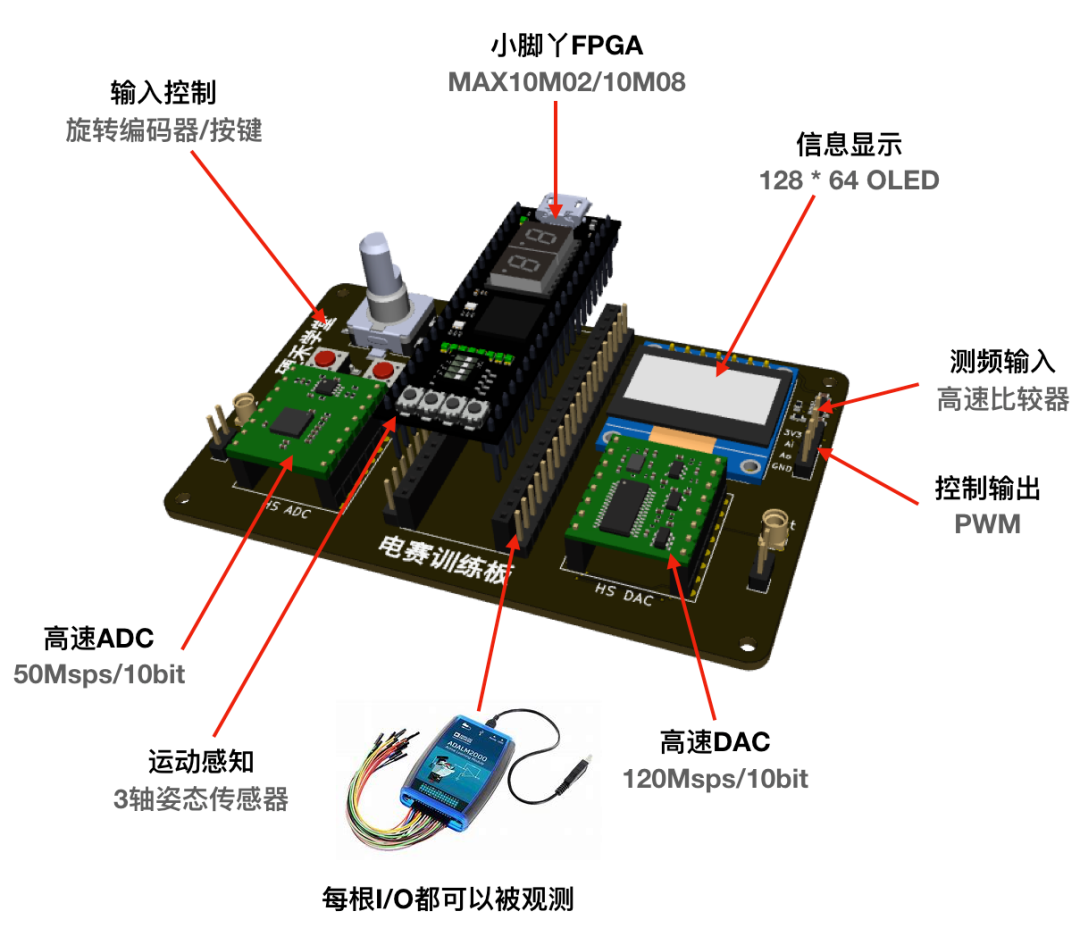

使用的平台:

多数FPGA芯片上没有ADC的功能,而一些应用则需要用到ADC对一些模拟信号,比如直流电压等进行量化,有没有特别简单、低成本的实现方法呢?

在要求转换速率不高的情况下,完全可以借助一颗高速比较器(成本只有几毛钱)来实现对模拟信号的量化,Lattice的官网上一篇文章就介绍了如何制作一个简易的Sigma Delta ADC,如果FPGA能够提供LVDS的接口,连外部的高速比较器都可以省掉。由于我们的小脚丫FPGA核心模块在设计的时候没有考虑到LVDS的应用场景,所以还是需要搭配一个高速的比较器来实现Lattice官网上推荐的简易Sigma Delta ADC的功能。

让小脚丫FPGA通过锁相环PLL运行于120MHz的主时钟(还可以更高,提速到240MHz、360MHz都应该没有问题),测试1KHz以内的模拟信号是没有问题的。

Lattice的官网上就可以下载到简易Sigma Delta ADC的Verilog源代码,可以非常方便地用在其它品牌、其它系列的FPGA上。

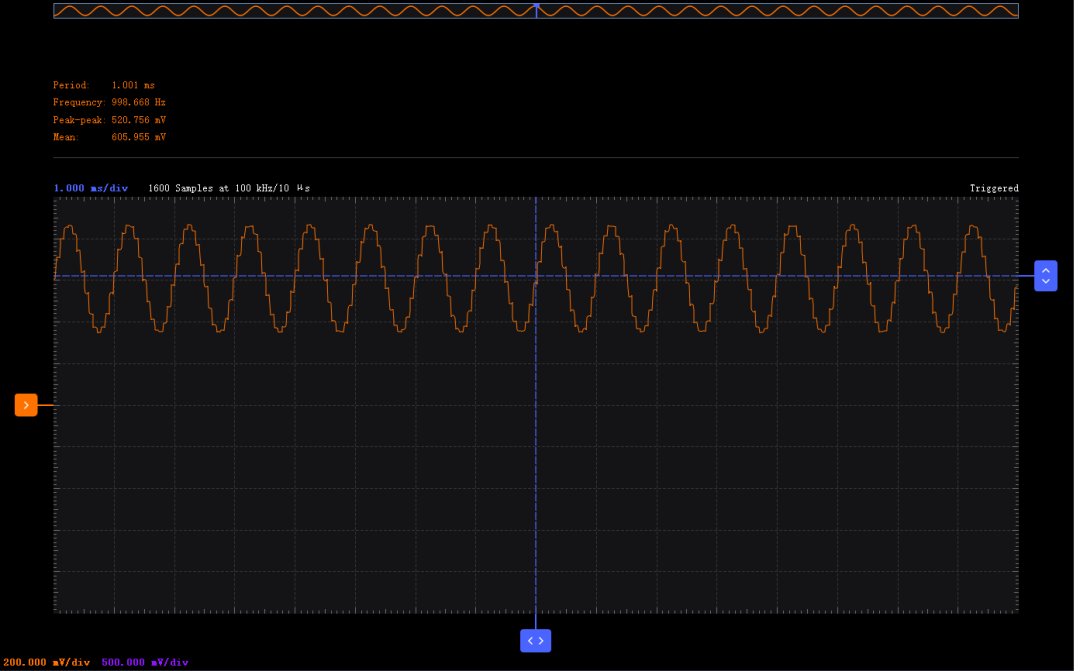

下面的截图就是采用120MHz的主时钟实现的对1KHz模拟信号的采样,并通过DDS/DAC输出,口袋仪器M2000采集并显示的模拟信号波形。

M2000口袋仪器显示的1KHz的波形

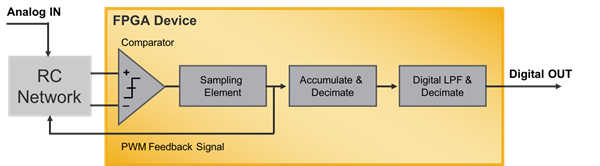

工作原理

详细的工作原理介绍可以参考项目https://www.eetree.cn/project/detail/255 及项目页面中的参考资料,在这里以几幅图片来示例一下。

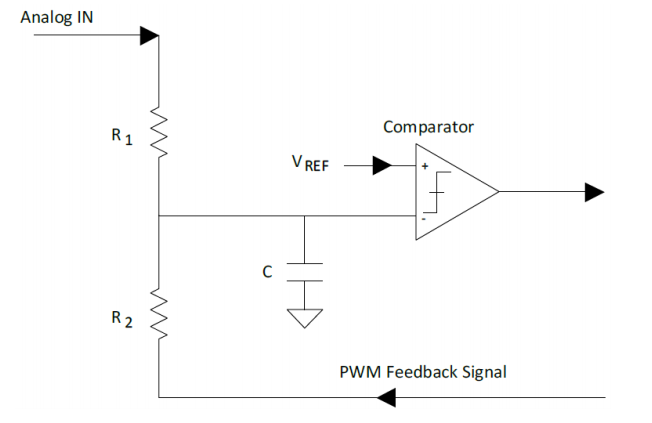

简易Sigma Delta ADC的工作原理

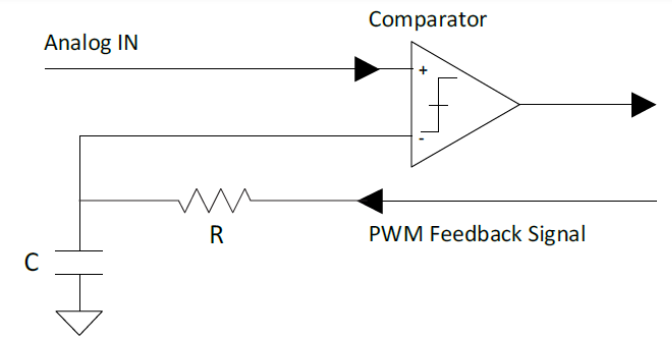

直接连接 - 被测模拟信号的幅度范围为0-3.3V

通过电阻分压网络输入,并在比较器+端提供参考电压,则被采集模拟信号的电压变化范围可以扩展

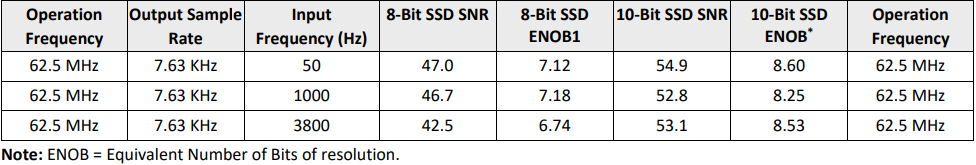

简易Sigma Delta ADC的性能与逻辑电路的工作频率

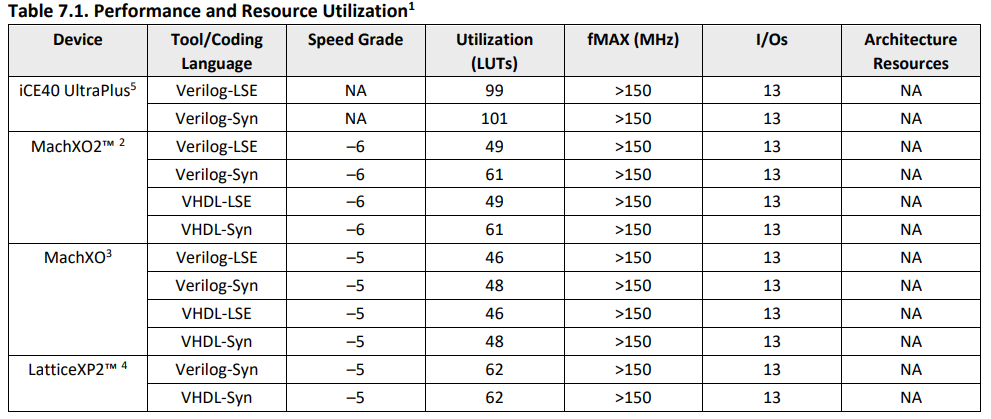

在不同的FPGA平台上消耗的逻辑资源

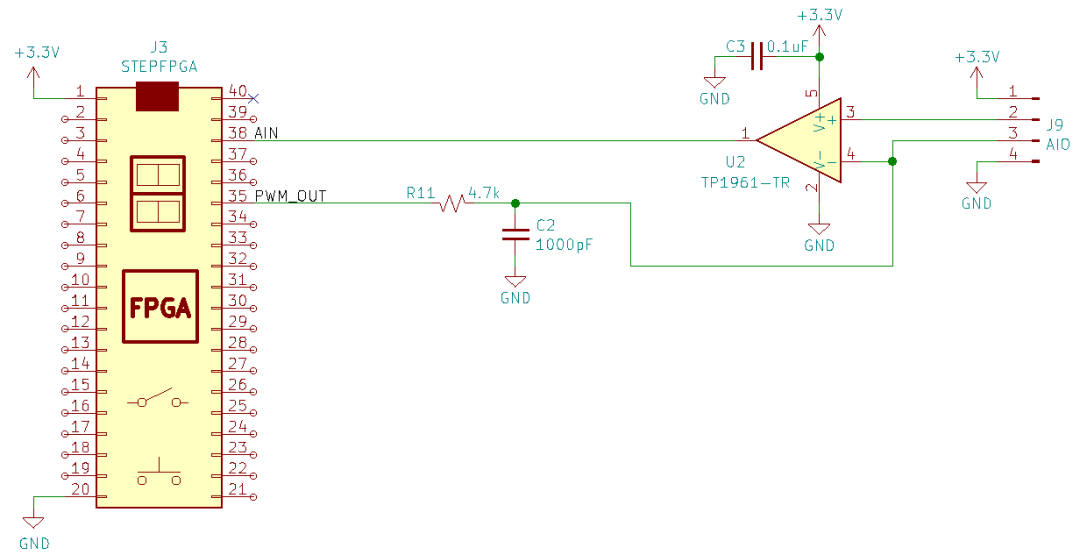

以下就是我们的电赛综合训练板上简易Sigma Delta ADC部分的电路连接

核心代码:

顶层调用代码:

wire [7:0] sd_adc_out; // sigma delta adc data output

wire sample_rdy; // flag for adc conversion

ADC_top my_adc(.clk_in(clk_hs),.rstn(1'b1),.digital_out(sd_adc_out), .analog_cmp(comp_in),.analog_out(ad_pwm),.sample_rdy(sample_rdy));

assign dac_data = sd_adc_out;

assign dac_clk = clk_hs; //120MHz generated by PLL

Sigma Delta ADC顶层程序

//*********************************************************************

//

// ADC Top Level Module

//

//*********************************************************************

module ADC_top (

clk_in,

rstn,

digital_out,

analog_cmp,

analog_out,

sample_rdy);

parameter

ADC_WIDTH = 8, // ADC Convertor Bit Precision

ACCUM_BITS = 10, // 2^ACCUM_BITS is decimation rate of accumulator

LPF_DEPTH_BITS = 3, // 2^LPF_DEPTH_BITS is decimation rate of averager

INPUT_TOPOLOGY = 1; // 0: DIRECT: Analog input directly connected to + input of comparitor

// 1: NETWORK:Analog input connected through R divider to - input of comp.

//input ports

input clk_in; // 62.5Mhz on Control Demo board

input rstn;

input analog_cmp; // from LVDS buffer or external comparitor

//output ports

output analog_out; // feedback to RC network

output sample_rdy;

output [7:0] digital_out; // connected to LED field on control demo bd.

//**********************************************************************

//

// Internal Wire & Reg Signals

//

//**********************************************************************

wire clk;

wire analog_out_i;

wire sample_rdy_i;

wire [ADC_WIDTH-1:0] digital_out_i;

wire [ADC_WIDTH-1:0] digital_out_abs;

assign clk = clk_in;

//***********************************************************************

//

// SSD ADC using onboard LVDS buffer or external comparitor

//

//***********************************************************************

sigmadelta_adc #(

.ADC_WIDTH(ADC_WIDTH),

.ACCUM_BITS(ACCUM_BITS),

.LPF_DEPTH_BITS(LPF_DEPTH_BITS)

)

SSD_ADC(

.clk(clk),

.rstn(rstn),

.analog_cmp(analog_cmp),

.digital_out(digital_out_i),

.analog_out(analog_out_i),

.sample_rdy(sample_rdy_i)

);

assign digital_out_abs = INPUT_TOPOLOGY ? ~digital_out_i : digital_out_i;

//***********************************************************************

//

// output assignments

//

//***********************************************************************

assign digital_out = ~digital_out_abs; // invert bits for LED display

assign analog_out = analog_out_i;

assign sample_rdy = sample_rdy_i;

endmodule

Sigma Delta ADC主程序

//*********************************************************************

//

// SSD Top Level Module

//

//*********************************************************************

module sigmadelta_adc (

clk,

rstn,

digital_out,

analog_cmp,

analog_out,

sample_rdy);

parameter

ADC_WIDTH = 8, // ADC Convertor Bit Precision

ACCUM_BITS = 10, // 2^ACCUM_BITS is decimation rate of accumulator

LPF_DEPTH_BITS = 3; // 2^LPF_DEPTH_BITS is decimation rate of averager

//input ports

input clk; // sample rate clock

input rstn; // async reset, asserted low

input analog_cmp ; // input from LVDS buffer (comparitor)

//output ports

output analog_out; // feedback to comparitor input RC circuit

output sample_rdy; // digital_out is ready

output [ADC_WIDTH-1:0] digital_out; // digital output word of ADC

//**********************************************************************

//

// Internal Wire & Reg Signals

//

//**********************************************************************

reg delta; // captured comparitor output

reg [ACCUM_BITS-1:0] sigma; // running accumulator value

reg [ADC_WIDTH-1:0] accum; // latched accumulator value

reg [ACCUM_BITS-1:0] counter; // decimation counter for accumulator

reg rollover; // decimation counter terminal count

reg accum_rdy; // latched accumulator value 'ready'

//***********************************************************************

//

// SSD 'Analog' Input - PWM

//

// External Comparator Generates High/Low Value

//

//***********************************************************************

always @ (posedge clk)

begin

delta <= analog_cmp; // capture comparitor output

end

assign analog_out = delta; // feedback to comparitor LPF

//***********************************************************************

//

// Accumulator Stage

//

// Adds PWM positive pulses over accumulator period

//

//***********************************************************************

always @ (posedge clk or negedge rstn)

begin

if( ~rstn )

begin

sigma <= 0;

accum <= 0;

accum_rdy <= 0;

end else begin

if (rollover) begin

// latch top ADC_WIDTH bits of sigma accumulator (drop LSBs)

accum <= sigma[ACCUM_BITS-1:ACCUM_BITS-ADC_WIDTH];

sigma <= delta; // reset accumulator, prime with current delta value

end else begin

if (&sigma != 1'b1) // if not saturated

sigma <= sigma + delta; // accumulate

end

accum_rdy <= rollover; // latch 'rdy' (to align with accum)

end

end

//***********************************************************************

//

// Box filter Average

//

// Acts as simple decimating Low-Pass Filter

//

//***********************************************************************

box_ave #(

.ADC_WIDTH(ADC_WIDTH),

.LPF_DEPTH_BITS(LPF_DEPTH_BITS))

box_ave (

.clk(clk),

.rstn(rstn),

.sample(accum_rdy),

.raw_data_in(accum),

.ave_data_out(digital_out),

.data_out_valid(sample_rdy)

);

//************************************************************************

//

// Sample Control - Accumulator Timing

//

//************************************************************************

always @(posedge clk or negedge rstn)

begin

if( ~rstn ) begin

counter <= 0;

rollover <= 0;

end

else begin

counter <= counter + 1; // running count

rollover <= &counter; // assert 'rollover' when counter is all 1's

end

end

endmodule

-

fpga开发板使用教程之在K7上用Ibert实现基本的GTX测试2020-12-31 9436

-

ADC实现一个IO上挂多个按键2022-09-01 3846

-

如何用STM32F407实现一个可编程的模拟比较器的功能?2018-11-28 2602

-

STM32F303VCT6比较器只有三个可以用2019-02-13 3762

-

怎么利用FPGA和CPLD数字逻辑实现ADC?2019-08-19 2707

-

如何利用FPGA实现高频率ADC?2019-09-19 4625

-

用matlab来实现fpga功能的设计2008-01-16 11748

-

基于FPGA和CPLD数字逻辑实现ADC技术2010-05-25 1924

-

基于fpga和cpld低频/最小逻辑ADC实现2018-04-26 1836

-

编写一个可以用GRUB来引导的简单x86内核2018-01-21 8458

-

将UART功能集成到FPGA内部实现多模块的设计2019-10-18 3594

-

如何制作一个简易的Sigma Delta ADC?2021-04-01 6110

-

用FPGA搭配3个电阻、1个电容制作的1bit SDR接收机2021-11-09 6538

-

FPGA上可以用一个比较器实现ADC的功能?22023-04-25 1712

-

一文看懂电感可以用大的替换小的吗2024-01-13 2282

全部0条评论

快来发表一下你的评论吧 !