AD9361数据路径在低电压差分信号(LVDS)模式下运行

电子说

描述

1

概述

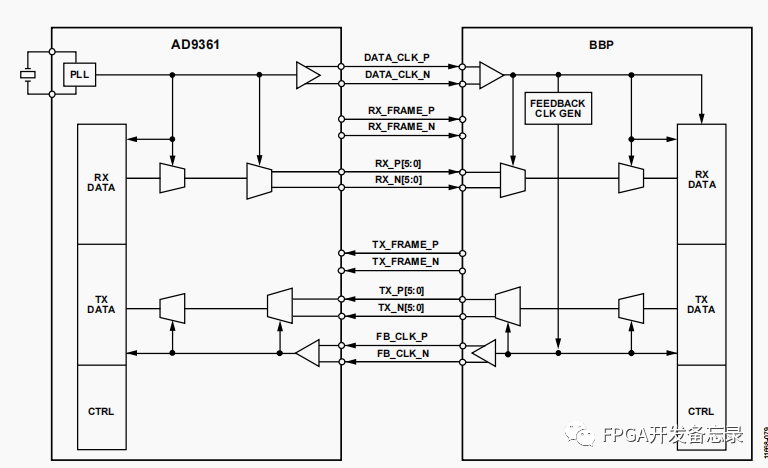

接下来将介绍AD9361数据路径在低电压差分信号(LVDS)模式下运行。AD9361数据接口使用并行总线(P0和P1)在AD9361和BBP之间传输数据样本。这个总线传输使用简单的硬件握手信号进行控制。在LVDS模式,两个总线都与差分LVDS信令一起使用。9361的LVDS接口有助于连接到具有LVDS能力的自定义的ASIC和FPGA。

当一个系统需要在噪声环境中有优越的交换性能和高于CMOS标准接口能提供的更高的传输速率时,通常会选用LVDS接口。当使用LVDS接口时,建议所有的的路径长度不超过12英寸以及保持差分路径紧挨着且等长。下面是LVDS模式下的数据路径。

2

LVDS接口模式下的数据路径信号

数据路径接口由下面这些信号组成。

2.1

数据时钟(DATA_CLK)

DATA_CLK是由9361产生的差分信号并提供给BBP为RX数据路径提高主时钟。BBP使用主时钟作为数据样本的基带处理和接口的数据传输的时序参考。DATA_CLK在接收操作时为RX_D[5:0]提供了具有DDR操作的源同步定时。SDR在LVDS模式无效。

DATA_CLK的频率取决于系统架构(包括射频通道,过采样程度以及带宽(BW)模式)。频率通过SPI接口写入到AD9361。

DATA_CLK可以被AD9361停止(以响应来自BBP的项目)在接口空闲期间减少电力消耗。如果没有使能DATA_CLK,从 nontoggling状态的切换必须符合电力层对对clean信号转换的需求,且valid层始终由AD9361驱动。

2.2

FB_CLK

FB_CLK是由BBP驱动的差分LVDS信号,是DATA_CLK反馈的一个信号。FB_CLK为TX_D[5:0]在Tx bursts期间提供了具有双边沿捕获的源同步定时。

FB_CLK在空闲期间可被BBP停止,以此来减少电能消耗。假如这样的话,从 nontoggling状态的切换必须符合电力层对对clean信号转换的需求,且valid层始终由BBP驱动。

2.3

RX_FRAME

RX_FRAME是由AD9361驱动的差分LVDS信号,送到BBP 作为9361提供的数据采样的帧信号。切换到高时指示帧信号的开始。RX_FRAME在突发传输开始时可以被设置为一个单一的到高的变迁,在整个突发传输中保持高,或者也可以设置为每个帧信号开始都有一个上升沿的脉冲序列(占空比为50%)

2.4

RX_D[5:0]

RX_D[5:0]是由6个差分对组成的差分LVDS数据总线。它由9361驱动送到接收数据的BBP。数据以数据字对在总线上传输,创建了12bit的数据总线。

2.5

RX_FRAME

TX_FRAME是由BBP驱动的差分LVDS信号,供给9361作为由BBP提供的数据采样的帧信号。切换到高时指示帧信号的开始。Tx_FRAME可以接受在突发传输开始时的一个到高信号的切换,在整个突发中保持高,或者在每帧开始时有上升边缘的脉冲序列(50%占空比)

AD9361一直传输空数据(全为0)直到第一个TX_FRAME信号指示有效数据。当Tx路径在FDD独立模式下完成一次传输操作时并且数据路径没有自动刷新时,这将是一个有用的特征。在这种情况下TX_FRAME将会维持低电平来完成数据刷新操作。更多细节参考状态机使能部分。

注意:RX_FRAME和TX_FRAME都是接口正常工作所必须要的信号。

2.6

TX_D[5:0]

TX_D[5:0]是由6个差分对组成的差分LVDS信号。它由BBP驱动送到9361,数据由发射器输出。数据以数据字对在总线上传输,创建了12bit的数据总线。

2.7

ENABLE

ENABLE是由BBP驱动到9361,在TDD模式提供数据突发传输控制(与TXNRX)。BBP提供的ENABLE信号至少触发一个DATA_CLK周期,以指示每个突发的开始,随后第二次也至少触发一个DATA_CLK周期来指示突发传输结束。AD9361在内部跟踪ENABLE脉冲的序列,以正确地解释每个脉冲是每个突发传输的开始还是结束。ENABLE信号也能配置为电平模式,其中信号的状态(而不是脉冲)决定ENSM何时在状态之间移动。

在LVDS模式,该端口一直为有效状态(高电平)。在TDD模式,BBP和9361都忽略了inactive方向上的数据。开始和结束延迟(由AD9361采样的ENABLE脉冲与总线上第一和最后一个有效数据采样之间)取决于数据路径配置的不同。Rx_FRAME和Tx_FRAME信号分别由BBP和AD9361用来确定有效数据。FB_CLK信号用于对输入进行采样。

在FDD模式下,ENABLE信号作为单个控制输入来确定ENSM的状态.还有一种替代的FDD模式,其中ENABLE信号可以重新定义为RxON,控制Rx功能的ENSM直接由硬件输入来控制。该模式称为FDD独立控制模式,BBP独立地控制RX功能,这样可以节省能源消耗。

2.8

TXNRX

TXNRX是由BBP驱动到9361,当ENSM在TDD模式时提供数据突发传输控制(与ENABLE)。当ENABLE被AD9361采样为高时开始一个突发时,TXNRX上的电平也会被采样来确定数据的方向。在TDD模式,TXNRX采样为高指示发送数据,采样为低电平指示接收突发传输。

TXNRX电平信号必须维持在整个数据突发传输(以一个有效的电平逻辑)。在采样ENABLE启动脉冲之前,TXNRX信号可以建立任意数目的周期(≥0),在采样ENABLE完成脉冲后,也可以改变任意次数的周期(≥0)。需要注意的是,TXNRX信号应该只在ENSM处于ALERT状态时改变状态,因为TXNRX上升和下降边缘在TDD模式下直接开关相应的合成器。

在正常的FDD模式下,TXNRX信号将被忽略,但必须保持在一个有效的逻辑电平。也有一种可替换的FDD模式,TXNRX信号可被重定义为TxON,直接的硬件输入到ENSM来控制TX功能。在FDD独立控制模式,BBP独立地控制TX功能,这样可节省消能源耗。

3

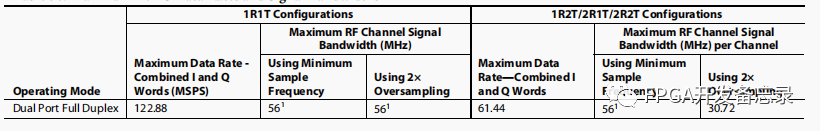

LVDS最大时钟速率和信号带宽

下表中列出的数据比较了LVDS数据总线配置在不同允许的工作模式下的最大数据时钟速率和信号带宽。列出了以下两种情况下的最大射频带宽:使用避免混叠的最小采样率进行采样,使用避免混叠的最小采样率进行采样,采样采用两倍的过采样。每种模式的细节将在后面的章节中给出。在LVDS模式下,最大DATA_CLK速率增加到245.76 MHz。该时钟和56 MHz最大模拟滤波器带宽限制了射频信道信号带宽。请注意,TDD和FDD模式的数据总线定时是相同的,因为每个路径(传输和接收)都有一个专用的总线。

4

双端口全双工模式(LVDS)

双总线全双工LVDS模式通过SPI写寄存器使能,在这个模式,p0和p1都被作为LVDS信号,并且数据总线(D[11:0])被分割成单独的子总线(Rx_D[5:0]和Tx_D[5:0])。每个子总线同时运行,允许在BBP和AD9361之间进行全双工传输和接收数据。传输数据(Tx_D[5:0])、FB_CLK和Tx_FRAME是由BBP驱动的,这样在FB_CLK、Tx_D[5:0]和Tx_FRAME之间的建立和保持时间允许AD9361使用FB_CLK捕获Tx_D[5:0]和Tx_FRAME。

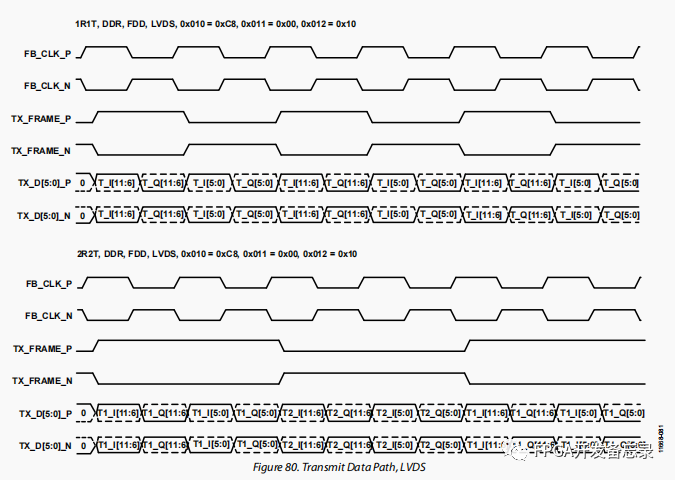

Tx_D[5:0]总线上的数据采样由Tx_FRAME信号构成,如时序图所示。传输数据样本以两个数据包的补体格式携带,每个数据包中的第一个6位字包含MSB,第二个6位字包含LSB。最大的正样本值是0x7FF,第一个字是0x1F,第二个字是0x3F,最大负值是0x800,第一个字是0x20,第二个字是0x00。Tx_D[5]是最重要的位,而Tx_D[0]是每个字中最不重要的位。

接收数据(RX_D[5:0]),DATA_CLK和RX_FRAME由AD9361驱动,DATA_CLK,RX_D[5:0]和RX_FRAME之间的建立保持时间允许BBP使用DATA_CLK去捕捉RX_D[5:0]和RX_FRAME。RX_D[5:0]总线上的数据采样由RX_FRAME组成,如时序图所示。传输数据样本以两个数据包的补体格式携带,每个数据包中的第一个6位字包含MSB,第二个6位字包含LSB。最大的正样本值是0x7FF,第一个字是0x1F,第二个字是0x3F,最大负值是0x800,第一个字是0x20,第二个字是0x00。Tx_D[5]是最重要的位,而Tx_D[0]是每个字中最不重要的位。

注意,在CMOS模式下,FB_CLK必须由DATA_CLK生成,以便保持相同的频率和占空比。这两个时钟信号之间没有相位关系的要求。

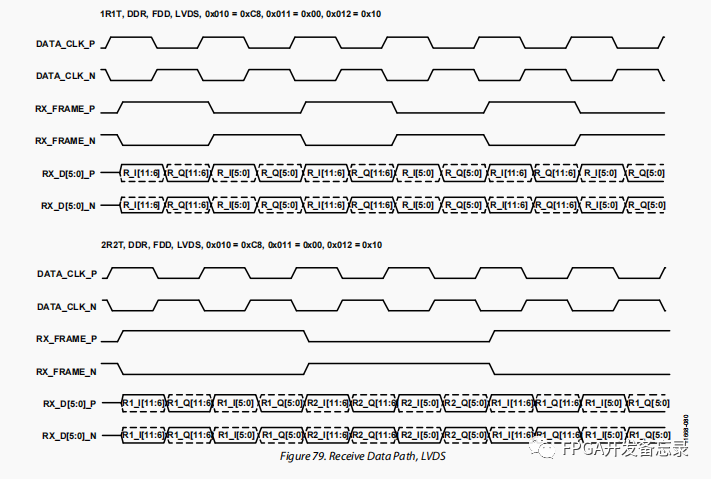

如前所述,I和Q数据采样在每个数据总线上进行时间交错。对于1R1T系统,I和Q采样以4路交错的方式携带:IMSB, QMSB, ILSB, QLSB, …在这种情况下,Tx_FRAME和Rx_FRAME信号与数据切换相一致。当启用50%占空比框架时,高状态时是IMSB和QMSB,低状态时是Ilsb和QLSB,然后,这些信号再次用IMSB调高,以指示新帧的开始。

对于2R2T系统,来自RF路径1和路径2的I和Q样本以8种方式交错携带:I1 MSB, Q1 MSB, I1 LSB, Q1 LSB, I2 MSB, Q2 MSB, I2 LSB, Q2 LSB, …在这种情况下,Tx_FRAME和Rx_FRAME信号与数据切换相一致。当启用50%占空比框架,高状态时是I1 LSB, Q1 LSB, I2 MSB, Q2 MSB,低状态时是 I2 MSB, Q2 MSB, I2 LSB, Q2 LSB.然后,这些信号再次用IMSB调高,以指示新帧的开始。

对于2R1T或1R2T配置的系统,时钟频率、总线传输速率和采样周期以及数据捕获时序与2R2T的系统的配置相同。

然而,在只使用一个通道的路径中,每个数据组中的禁用通道的I-Q对都未使用。这些未使用的IQ对将会被9361所忽略。例如,2R1T系统使用TX通道1,突发发送将会有4个未使用的slot:I1 MSB, Q1 MSB, I1 LSB, Q1 LSB, X, X, X, X, …在这种情况下,Tx_FRAME和Rx_FRAME与数据切换一致,高电平代表I1MSB, Q1MSB, I1LSB, Q1LSB,而低电平代表未使用的slot。这些信号再次用I1LSB切换高,以指示新帧的开始。未使用的Xslot可以由BBP填充任意的数据值

这些值可以是常量值,也可以重复前面的数据样本值,以降低总线切换点,从而降低功耗。

5

数据路径功能时序(LVDS)

图79和图80中的时序图说明了双端口FDD LVDS模式下总线信号之间的关系。时序图中的差分数据用实线和虚线绘制,以说明数据线的差分性质。

请注意,由于2R1T和1R2T系统遵循2R2T时序图,因此在图79和图80中省略了它们。

LVDS 模式中不支持以下bit:

-交换端口—在LVDS模式下,P0为Tx,P1为Rx。

无法更改此配置.

-单端口模式—两个端口都在LVDS模式下启用。

-FDD Full端口—在LVDS中不支持。

-FDD Alt Word Order—在LVDS中不支持。

-FDD交换bit—在LVDS中不支持。

-

低电压差分信号(LVDS)接口浪涌静电放电防护电路图2023-06-08 3370

-

LVDS振幅差分信号技术的优势和劣势2023-04-06 3594

-

一文详解LVDS低电压差分信号2023-03-08 13542

-

LVDS低电压差分信号的优点及布板注意事项2022-07-03 6057

-

如何利用低电压差分信号接口器件实现数据远距离传输的设计2021-04-30 2609

-

AD9361工作在LVDS模式下有一个通道的噪声特别大2019-02-19 5770

-

AD9361在TDD lvds工作方式下的管脚时序2018-12-27 4711

-

ad9361 lvds接口调试2018-08-30 8267

-

LVDS低电压差分信号2016-04-15 2784

-

未使用端接的低电压差分信号总线输入方案2011-08-01 1938

-

基于低电压差分信号(LVDS)的高速信号传输2010-12-17 1174

-

低电压差分信号传输(LVDS)在汽车电子中的应用2010-08-31 2827

-

通过低电压差分信号(LVDS)传输高速信号2009-04-24 2094

-

什么是lvds信号2008-10-16 9268

全部0条评论

快来发表一下你的评论吧 !