FPGA双端口RAM的使用简述

电子说

1.4w人已加入

描述

1 简述

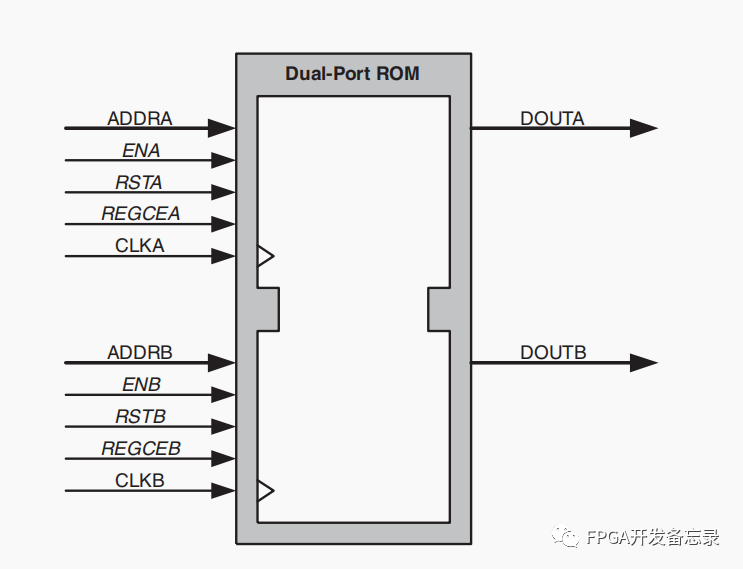

RAM :随机存取存储器(random access memory,RAM)又称作“随机存储器”。在FPGA开发过程中经常使用到,而所谓的双端口RAM就是有两组独立的端口对存储块进行读写操作,如下图所示。

一般在应用时,一个作为读端口,另一个作为写端口(也可以同时写和读)。

2 例化IP核

在开发过程中,常会用到双端口RAM,下面说一下FPGA中双端口RAM的常规使用方法,更多的使用方案可翻阅参考文献。

本次仿真采用Xilinx的 Block Memory Generator v8.4的IP核来进行例化,例化参数如下。

porta端口配置

portb端口配置

若以端口a作为写端口,b作为读端口,则写端口的数据位宽为128bit,深度为8192,则地址位宽为14bit,而读端口的数据位宽为32bit,深度为3276,则地址宽度为15bit。

3 端口描述

在写仿真激励之前,需要了解各端口在IP核中的功能,例化后的IP核如下图所示

各端口定义如下,端口b定义和a一样。

4 仿真激励编写

根据端口定义设计仿真激励,tb代码如下。

`timescale 1ns / 1ps

module tb_memory();

reg [12:0] addra;

reg clka ;

reg [127:0] dina ;

reg wea ;

reg ena ;

reg [14:0] addrb;

reg clkb ;

wire [31:0] doutb;

reg enb ;

reg web ;

initial begin

addra = 13'd0;

clka = 1'b0 ;

dina = 128'h40000000300000002000000010000000;

wea = 1'b1;

ena = 1'b1;

addrb = 15'd0;

clkb = 1'b0 ;

enb = 1'b1;

web = 1'b0;

end

always #10 clka = ~clka;//写时钟为50M

always #20 clkb = ~clkb;//读时钟为25M

reg [15:0] counta = 16'd0;

always @(posedge clka) begin;

if(wea==1'b1) begin

addra <= addra + 13'b1;

dina <= dina + 128'b1;

if (addra == 13'h3fff) begin

addra <= 13'h0;

end

end

end

reg [15:0] countb = 16'd0;

always @(posedge clkb) begin

if(enb==1'b1) begin

addrb <= addrb + 15'b1;

if (addrb == 15'h3fff) begin

addrb <= 15'h0;

end

end

end

design_1_wrapper tb_memory(

.BRAM_PORTA_0_addr(addra),

.BRAM_PORTA_0_clk (clka ),

.BRAM_PORTA_0_din (dina ),

.BRAM_PORTA_0_we (wea ),

.BRAM_PORTA_0_en (ena),

.BRAM_PORTB_0_addr(addrb),

.BRAM_PORTB_0_clk (clkb ),

.BRAM_PORTB_0_dout(doutb),

.BRAM_PORTB_0_we (web),

.BRAM_PORTB_0_en (enb)

);

endmodule

仿真结果如下图所示

由上图所示,由于写数据的位宽为128bit,读数据的位宽为32bit,因此需要读4次拼接起来才能恢复写入的数据。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

fpga双口ram的使用2024-03-15 2395

-

什么是双口RAM? 基于FPGA的双口RAM有哪些应用?2021-05-06 1850

-

请问双端口RAM在高速数据采集中有什么应用?2021-04-14 1711

-

简单的双端口和真正的双端口RAM之间的资源使用差异?2019-06-10 3306

-

【FPGA开源教程连载】第十三章A 嵌入式RAM使用之双端口RAM2017-01-02 6967

-

求大神!!!单端口和双端口RAM的区别是啥???2015-02-10 17736

-

FPGA双口ram2013-10-21 2093

-

关于FPGA设计双口ram的问题2012-07-13 3632

-

双端口RAM原理介绍及其应用2011-12-29 21891

-

基于Actel FPGA的双端口RAM设计2010-11-15 903

-

利用FPGA实现双口RAM的设计及应用2010-04-16 11944

-

双端口RAM的并口设计应用2010-03-03 2134

-

基于FPGA的双口RAM实现及应用2010-02-11 689

-

介绍带8×8双端口RAM的数据采集系统AD7581与μP接口2009-06-11 775

全部0条评论

快来发表一下你的评论吧 !