晶圆制造的三大核心之薄膜沉积的原子层沉积(ALD)技术

制造/封装

540人已加入

描述

薄膜沉积是晶圆制造的三大核心步骤之一,薄膜的技术参数直接影响芯片性能。半导体器件的不断缩小对薄膜沉积工艺提出了更高要求,而ALD技术凭借沉积薄膜厚度的高度可控性、优异的均匀性和三维保形性,在半导体先进制程应用领域彰显优势。

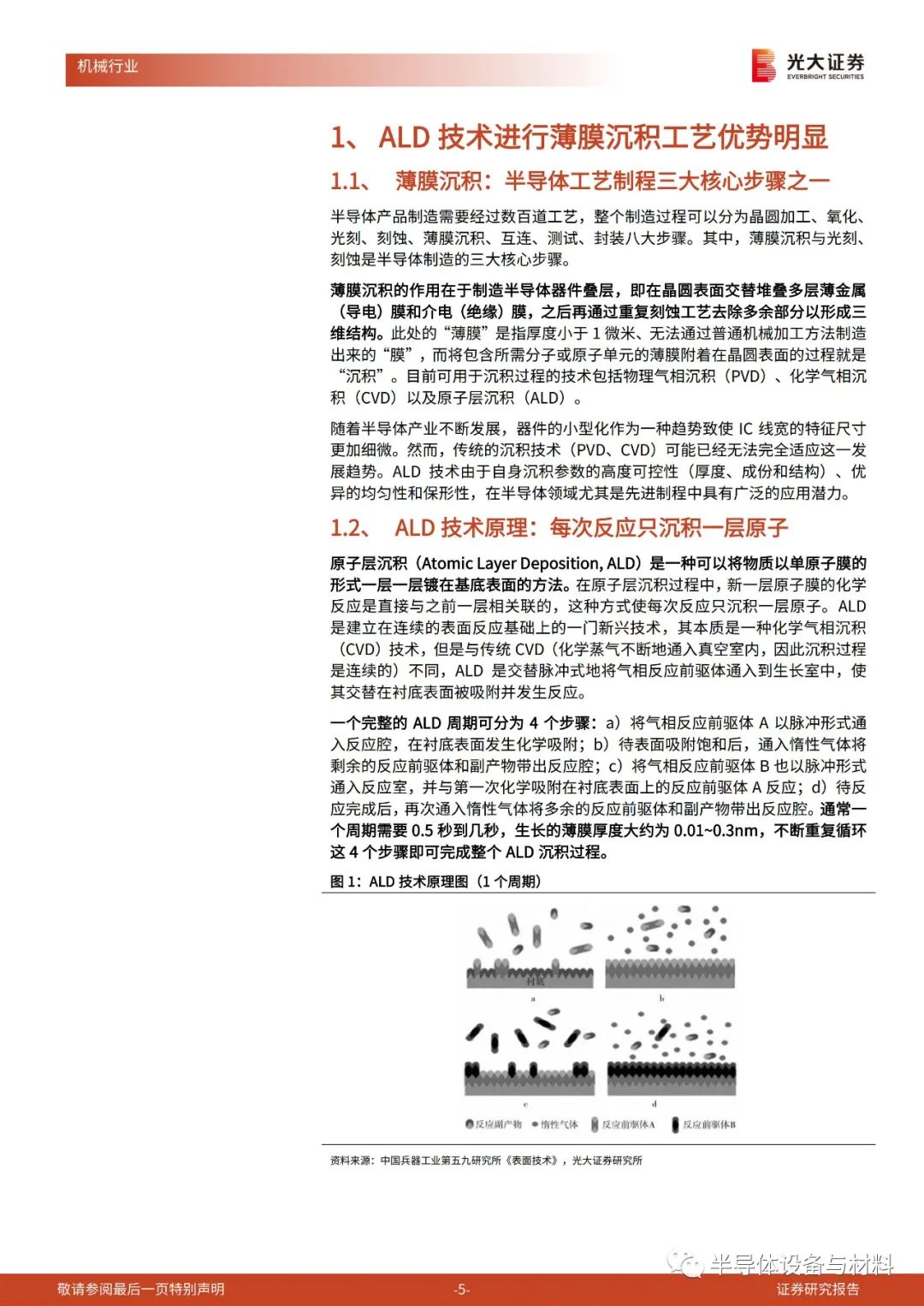

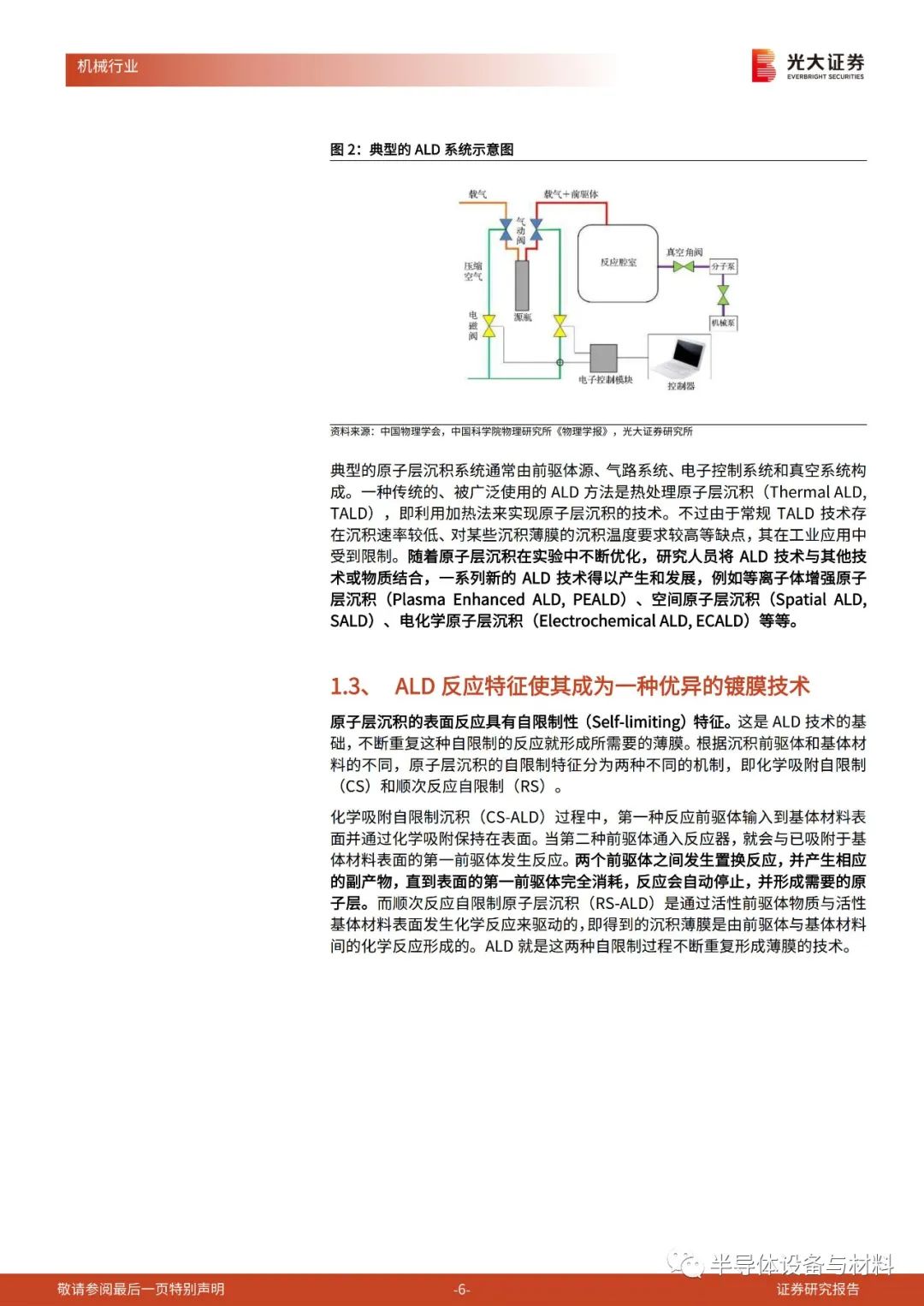

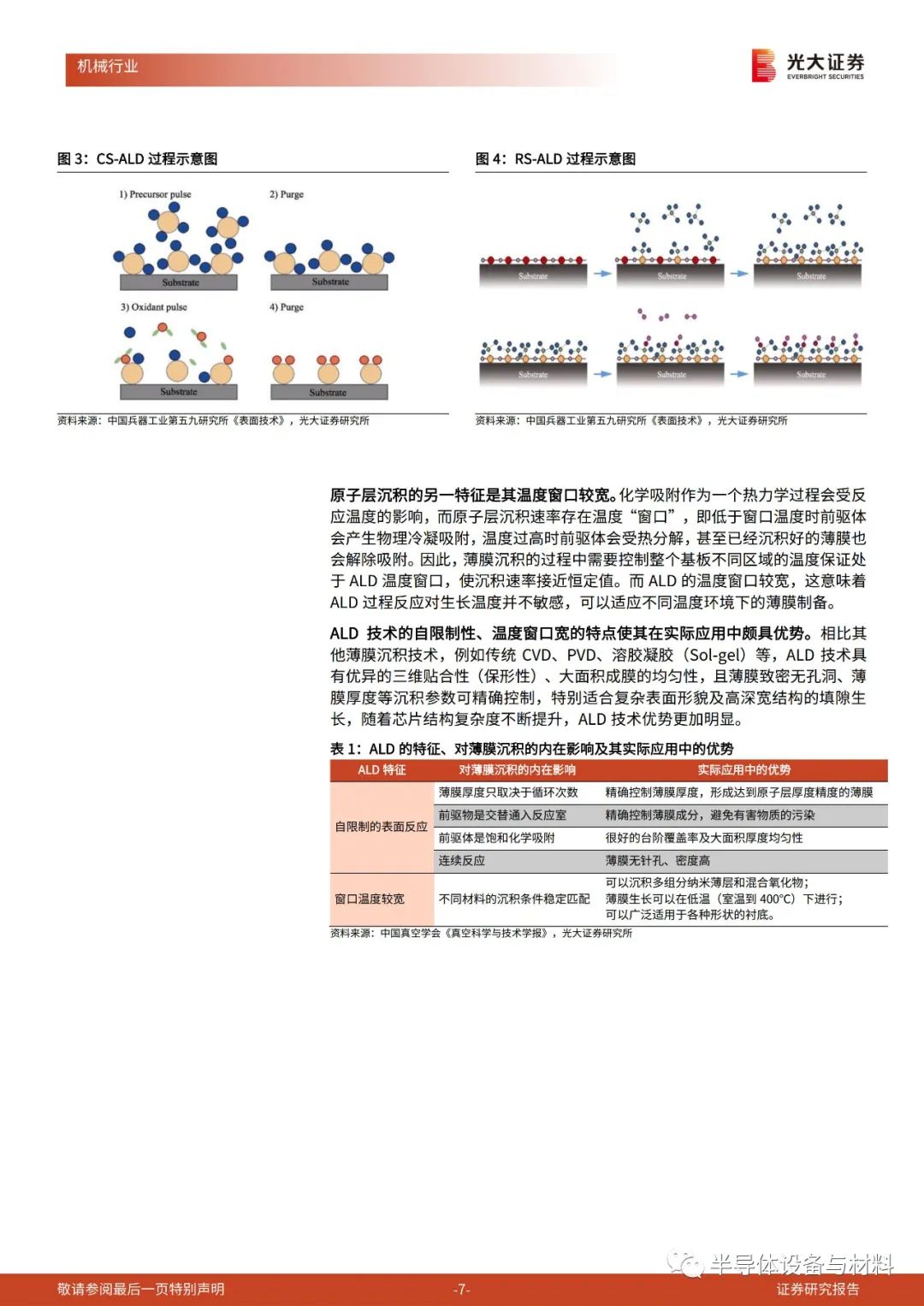

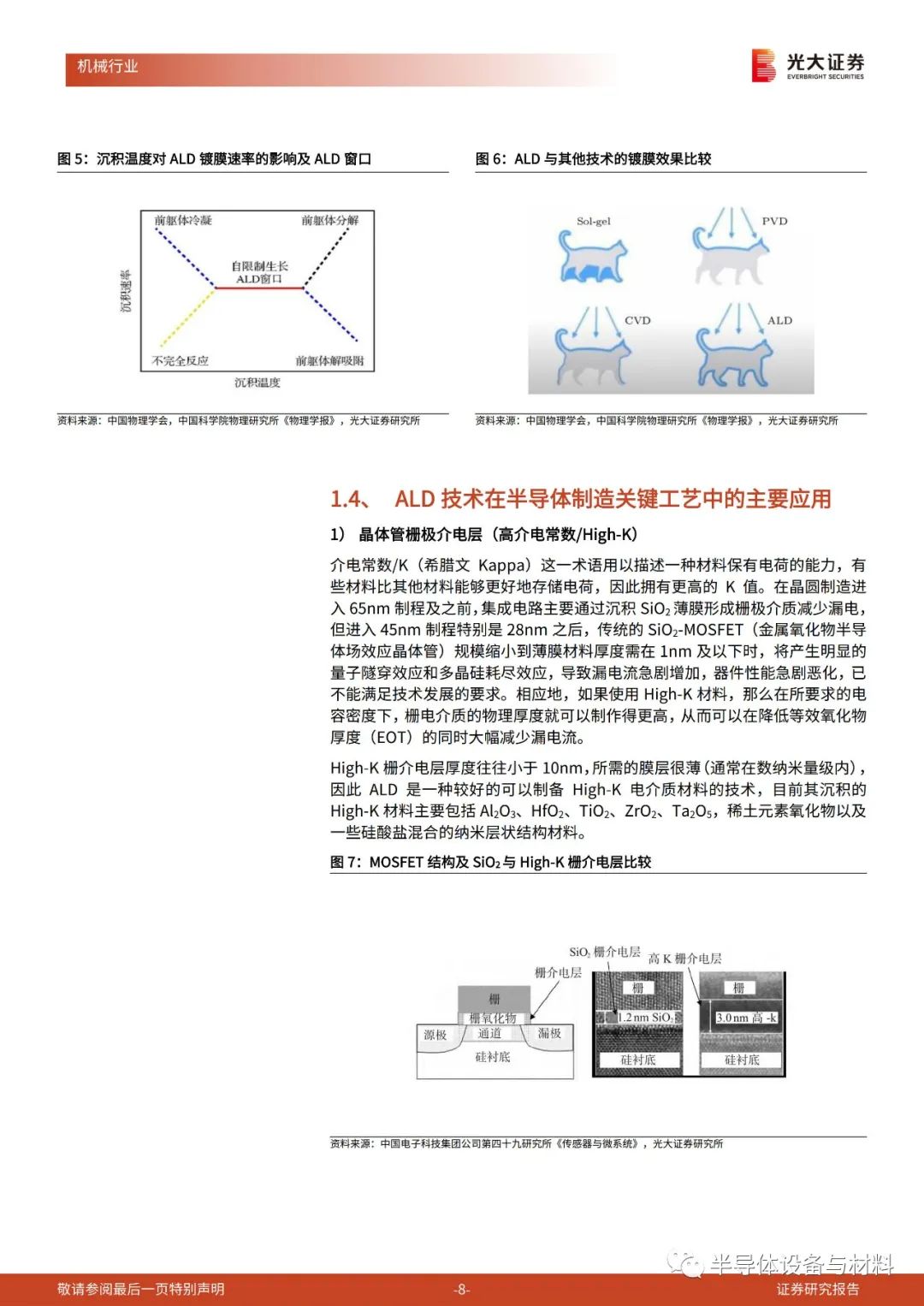

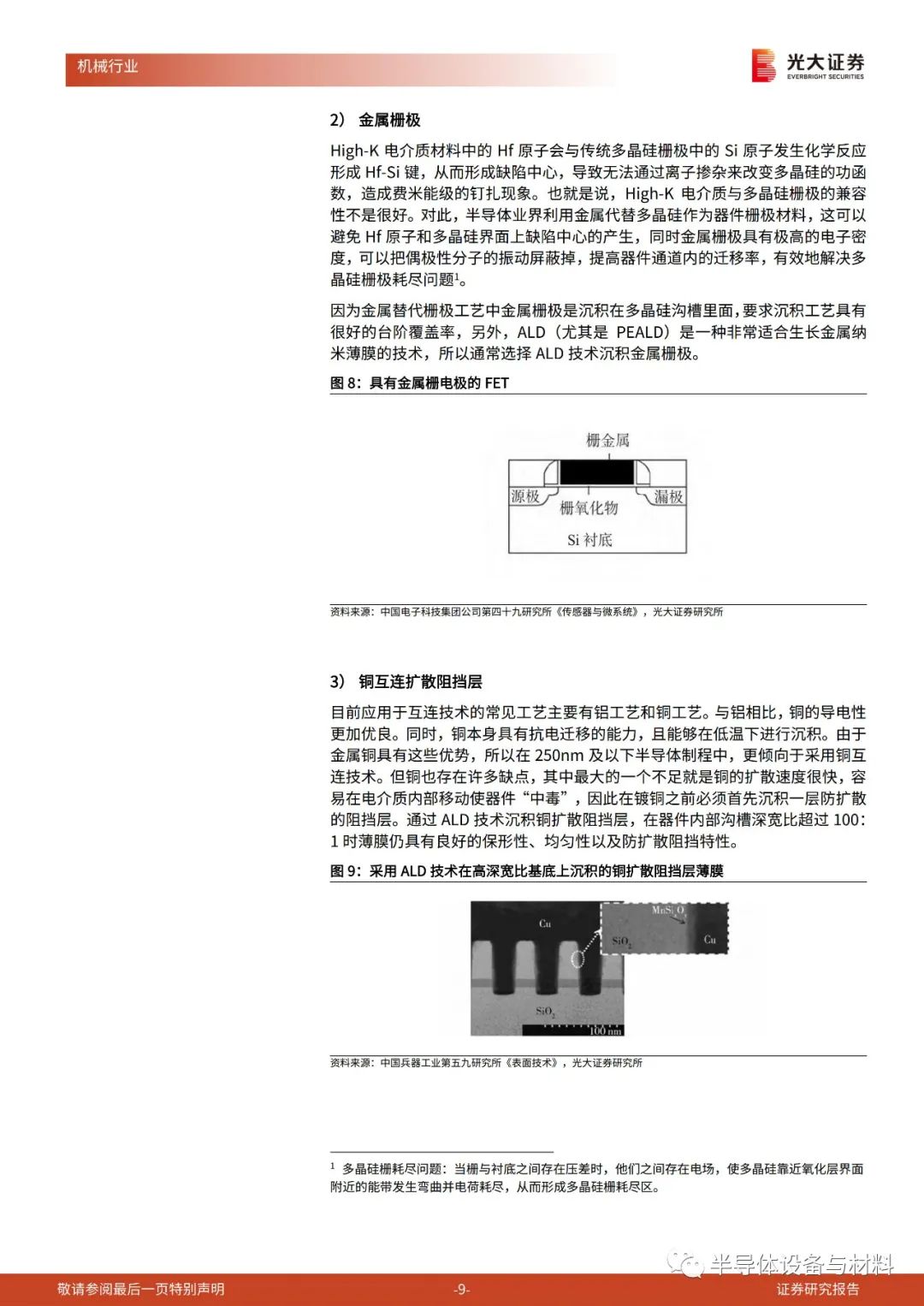

用于薄膜沉积的技术包括物理气相沉积(PVD)、化学气相沉积(CVD)和原子层沉积(ALD)。其中ALD技术是一种将物质以单原子膜的形式逐层镀在基底表面的方法,能够实现纳米量级超薄膜的沉积。目前ALD技术可以细分为TALD、PEALD、SALD等,制备的薄膜类型包括氧化物、氮(碳)化物、金属与非金属单质等,涵盖介电层、导体和半导体。ALD反应的自限制性和窗口温度较宽的特征,使其生长的薄膜具有很好的台阶覆盖率、大面积均匀、致密无孔洞且厚度等沉积参数易于精确控制。ALD技术特别适合复杂形貌、高深宽比沟槽表面的薄膜沉积,被广泛应用于High-K栅介质层、金属栅、铜扩散阻挡层等半导体先进制程领域。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路制程设备领域原子层沉积技术解析2021-02-05 6373

-

请问一下8寸 原子层沉积设备ALD,单晶片。国内设备大约在什么价位啊?2023-06-16 9926

-

泛林集团宣布推出一种用于沉积低氟填充钨薄膜的新型原子层沉积 (ALD) 工艺2018-05-24 3638

-

全球薄膜沉积设备市场规模至2025年有望达到340亿美元2020-09-07 8469

-

第三代半导体热潮“带货”沉积设备需求,供应链与服务本地化成关键考量2021-09-03 1699

-

原子层沉积(ALD)工艺助力实现PowderMEMS技术平台2022-03-17 3714

-

原子层沉积(Atomic Layer Deposition,ALD)2022-11-07 9988

-

半导体设备行业跟踪报告:ALD技术进行薄膜沉积工艺优势2023-02-16 1437

-

原子层ALD沉积介绍2023-06-15 6837

-

韫茂科技获数亿元融资,加快薄膜沉积设备量产2023-06-28 1826

-

技术前沿:原子层沉积ALD介绍2023-07-13 17931

-

原子层沉积ALD技术实现边缘钝化,TOPCon电池效率提高0.123%2024-12-23 2939

-

原子层沉积(ALD, Atomic Layer Deposition)详解2025-01-17 4575

-

ALD和ALE核心工艺技术对比2025-01-23 2798

-

半导体薄膜沉积技术的优势和应用2025-01-24 2426

全部0条评论

快来发表一下你的评论吧 !