按键抖动消除verilog设计

描述

按键作为一种机械开关,在进行按键操作时,机械接触点的弹性及电压突变等原因,在机械开关合闭的时候会出现电压抖动,因此在实际的应用当中需要做一定的处理。

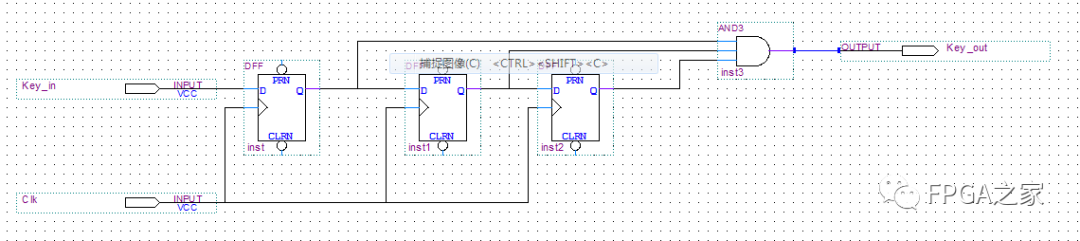

一般按键按下就是低电压,这种按键去抖动的关键就是获取稳定的低电压电平状态,因此,对于对于一个按键信号,可以用一个脉冲信号对其进行采样,如果连续三次采样都为低电平的话,就认为是按键被按下。其数字电路原型为下图

其实,我们在做FPGA设计之前,就应该大概知道自己的coding 在FPGA芯片上面会映射成什么电路,这样写的代码才是可靠的,有了上面的原理图,那么Verilog代码就很容易了,如下

input wire Clk ;

input wire key_in ;

output wire key_out ;

reg key_dly1 ;

reg key_dly2 ;

reg key_dly3 ;

always @(posedge Clk)

begin

if(Rst_n == 1'b0) begin

key_dly1 <= 1'b0; key_dly2 <= 1'b0; key_dly3 <= 1'b0; end

else

begin

key_dly1 <= key_in ;

key_dly2 <= key_dly1;

key_dly3 <= key_dly2;

end

end

assign key_out = key_dly1 | key_dly2 | key_dly3;

对于复杂的电路我们也可以把他分解为每一个触发器,然后心里有个大概的硬件原理图,这样写代码才胸有成竹。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA如何消除时钟抖动2024-08-19 4201

-

rs触发器消除按键抖动的原因2023-11-17 3824

-

单片机按键去抖动的方法2023-11-02 8618

-

开关抖动及消除设计2022-12-26 7157

-

运用外部中断函数消除按键抖动2022-03-02 1198

-

STM32F407 按键抖动 延时消抖2022-01-18 908

-

如何消除按键抖动的影响2022-01-17 2885

-

外部中断的按键抖动(按键消抖)2021-11-22 2110

-

单片机如何消除按键抖动?2021-10-21 1736

-

如何通过软件编程实现消除键盘的抖动2021-07-22 1812

-

消除按键抖动的两种方法分享2020-09-02 5344

-

按键弹跳消除模块的程序设计与应用2019-01-07 3533

-

关于按键抖动问题的解决2017-06-25 5525

-

verilog写cpld的程序如何消除按键的抖动?2014-04-02 4526

全部0条评论

快来发表一下你的评论吧 !