PCB信号完整性设计和测试应用

描述

高频高速电子产品的快速发展需要PCB具有高性能的系统结构,而不仅是有支撑作用的电子元器件。目前的电子系统设计普遍信号频率高于100 MHz,用来进行信号传输的高频高速印刷电路板也越来越容易受到信号完整性问题的影响。信号传输过程更容易出现反射、串扰等信号完整性问题,且频率越高、传输速率越快,信号损耗越严重,如何降低信号在传输过程中的损耗、保证信号完整性是高频高速PCB发展中的巨大挑战。高频时代PCB产品的信号完整性由PCB原材料和PCB设计产品两部分来提升。PCB材料的电性能可以通过测试介质层的介电常数、介质损耗以及导体铜箔粗糙度值来衡量;PCB产品的电性能主要通过测试阻抗和插入损耗(传输损耗)来衡量。主要介绍PCB原材料介质层的介电常数、介质损耗和导体铜箔粗糙度测试以及PCB产品阻抗、插入损耗设计和测试应用。

5G、物联网以及无人驾驶技术都处于高速发展阶段,需要在高频高速条件下传输信号。PCB(Printed Circuit Board,印制电路板)系统需要成为具有高性能的系统结构,而不再仅是起支撑作用的电子元器件。目前,电子系统设计普遍信号频率高于100 MHz,用来进行信号传输的高频高速印刷电路板也越来越容易受到信号完整性问题的影响。信号传输过程更容易出现反射、串扰等信号完整性问题,且频率越高、传输速率越快,信号损耗越严重,如何降低信号在传输过程中的损耗、保证信号完整性是高频高速PCB发展中的巨大挑战。

高频时代PCB产品的信号完整性电性能从PCB原材料和PCB设计产品两部分来提升。PCB材料的电性能可以通过测试介质层的介电常数( D k )、介质损耗( D f )以及导体铜箔粗糙度值来衡量;PCB产品的电性能主要通过测试阻抗和插入损耗(传输损耗)来衡量。

本文主要介绍PCB原材料介质层的介电常数、介质损耗和导体铜箔粗糙度测试以及PCB产品阻抗、插入损耗设计和测试应用。

1 PCB原材料介质层的参数介绍与测试

1.1 PCB原材料介质层的 D k 、 D f 及其测试

1.1.1 介电常数( D k )、介质损耗( D f )

介电常数:材料如果在受到外部电场作用时能够储存电能,就称为“电介质”。比如说,电容可以存储电荷,而当电容平板中间填充有介质时,存储的电荷会更多。介电常数越大,储存的电荷就越多,阻碍信号传输能力越大。

介质损耗:绝缘材料或电介质在交变电场中,由于介质电导和介质极化的滞后效应,使电介质内流过的电流相量和电压相量之间产生一定的相位差,即形成一定的相角,此相角的正切值即损耗因子 D f ,由介质电导和介质极化的滞后效应引起的能量损耗叫做介质损耗,也就是说, D f 越高,介质电导和介质极化滞后效应越明显,电能损耗或信号损失越多,是电介质损耗电能能力的表征物理量,也是绝缘材料损失信号能力的表征物理量。因此,PCB材料介质层的 D k , D f 越低,制作出的PCB产品插入损耗越低。

1.1.2 SPDR(Split Post Dielectric Resonator)法测试 D k 、 D f

测试高频材料电性能特性的方法很多,有传输线法、自由空间法、同轴探针法和谐振腔法,其中谐振腔法是最适合用于低损耗材料的测试。SPDR就是其中一种分离介质谐振腔法,是单频点的低损耗测试方法。SPDR的结构使用了极低损失的介电材料,使其能够建立具有更高 Q 因数且热稳定性优于传统全金属腔体的谐振器。SPDR的主要优势是:

1)较之传输反射法具有出色精度;

2)能够测试低损耗材料(传输反射技术无法测试损耗较低的材料);

3)不需要特殊的样本制备,可对基片和介质层进行方便、快速的无损测试。

SPDR法是无损测试方法,通过测定共振器内插入介质层前后的共振频率和 Q 值的变化量,测试 D k 和D f 值,测试夹具与测试原理如图1所示。不同频率使用不同的共振器目前提供的SPDR夹具可从1.1 GHz覆盖到15 GHz。

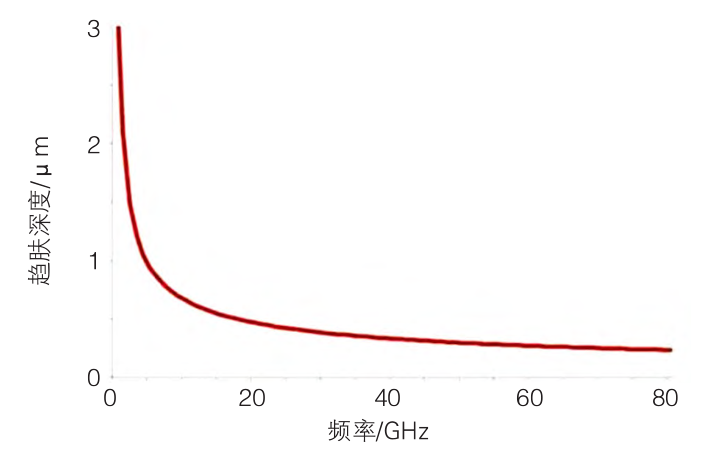

图1 趋肤深度与频率的关系1.2 导体铜箔粗糙度的测试

1.2.1 导体铜箔趋肤效应

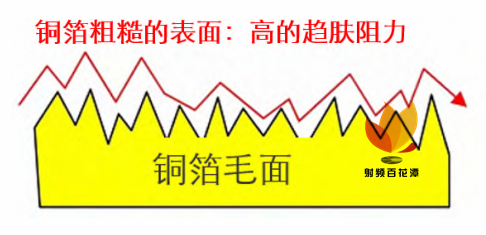

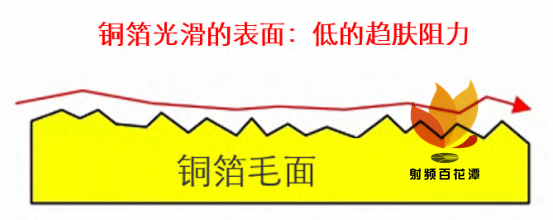

在高频高速条件下,信号传输越来越集中于导体“表层”,即趋肤效应(Skin Effect)。当频率达1 GHz时,其信号在导体表面的趋肤深度仅为2.10 µm;当信号传输频率提高到10 GHz时,其信号在导体表面的趋肤深度为0.66 µm;而在毫米波频段(>30 GHz),趋肤深度进一步降低至0.40 µm以下(如图1所示)。如果导体表面粗糙度大于趋肤深度时,信号传输仅在粗糙度的厚度范围内进行,使传输信号的驻波、反射越来越严重,并导致信号传输路径变长,增加传输损耗(如图2所示),信号在导体表面粗糙度低于趋肤深度时,传输路径短,降低传输损耗(如图3所示)。因此,导体铜箔粗糙度越低,制作出的PCB产品插入损耗(传输损耗)越低。

图2 信号在粗糙度大的铜箔表面传输

图3 信号在粗糙度低的铜箔表面传输

1.2.2 粗糙度测试

常规粗糙度的测试参数有:

1)线粗糙度:R a , R z, R q ;

2)面粗糙度:S a , S z , S q , S dr 。

R a , R z, R q 和 S a , S z , S q 粗糙度的定义同常规粗糙度的定义,这里需要特别强调的是 S dr 粗糙度。

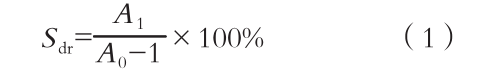

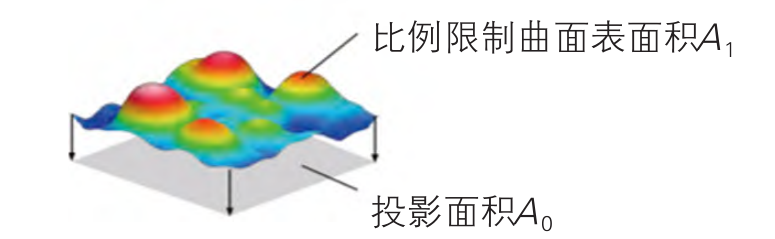

S dr 是界面扩展面积比,定义区域的扩展面积(表面积)表示相对于定义区域的面积增大了多少。如图4所示,其计算公式为:

图4 S dr 的定义图

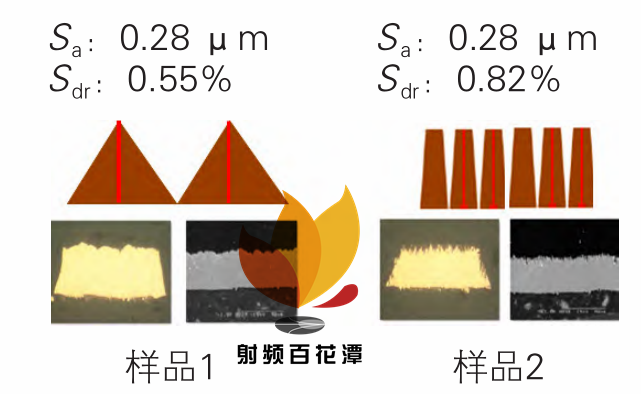

为什么要测 S dr ?如图5所示,样品1与样品2测量的 S a 值相同,测量 S dr 后可以发现样品2表面粗糙度较大。

图5 相同 S a 值样品的 S dr 不同

2 PCB产品阻抗设计和测试应用

2.1 PCB产品阻抗设计

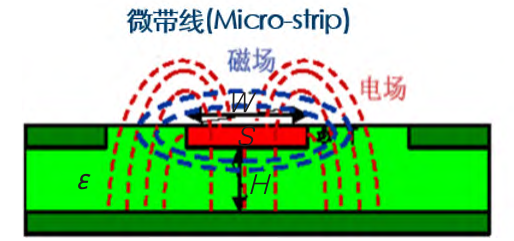

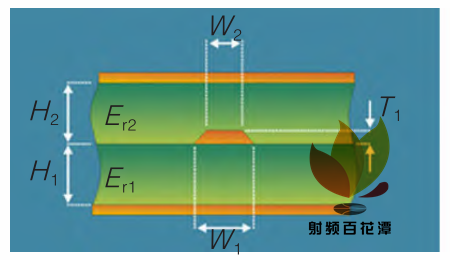

2.1.1 微带线(Micro-strip)和带状线(Stripline)的设计如图6所示,微带线(Micro-strip)是一种分布于电路板外层的传输线,通过介电材料与单个接地平面分离。微带线设计特点为:

1)电场穿透两种不同的介质层,较难控制阻抗;

2)空气的介电常数较PCB为低,所以整体微带线的介电常数较低;

3)受控阻抗走线的宽度较宽;

4)因为在PCB的表面,所以较易受外界干扰。

图6 微带线

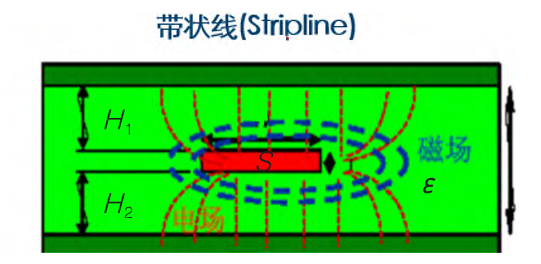

如图7所示,带状线(Stripline)是由介电材料包围的传输线,介于PCB内层两个接地平面之间。带状线设计特点为:

1)电场只在PCB范围内,较易控制阻抗;

2)介电常数较高;

3)受控阻抗走线的宽度要小于微带线中相同阻抗下走线的的宽度,这是因为有第二个接地面的存在,这些更小的走线宽度可以实现更高的布线密度;

4)因为在PCB的里面,所以不易受干扰。

图7 带状线

因此,做样品设计时,推荐使用带状线设计,阻抗易于控制且抗外界干扰能力更强。

2.1.2 单分和差分设计

对于带状线,差分匹配好就不存在远端噪声。与单分信号相比,差分信号在信号完整性方面有很多优势。比如有更好的抗噪声能力,对衰减不敏感,在高频电路设计中的应用越来越广泛,电路中关键的信号往往都要采用差分结构设计,如图8和图9所示。

图8 单分(单根走线)

图9 差分(双根走线)

2.2 PCB产品阻抗测试2.2.1 阻抗控制

为了使电路板走向高密度、小体积及单一零件趋势,多层板组装高速零件时,讯号线的“特性阻抗”必须控制在一定范围内,使高频信号顺利传输,以减少线路传输阻力、反射、失真、干扰等问题,此种品质要求称为“阻抗控制”(一般单分阻抗控制在50 Ω,差分阻抗控制在100 Ω)。

2.2.2 阻抗测试

阻抗测试设备有3种类型:1)阻抗测试仪;2)示波器;3)网络分析仪。

阻抗测试设备带宽频率越高,其组成的阶跃信号上升宽度越窄,阻抗测试精度越高。

3 PCB产品插入损耗设计和测试应用

3.1 PCB产品插入损耗设计

3.1.1 高频产品走线设计

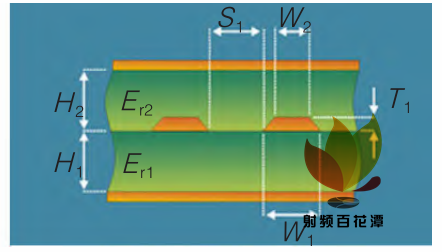

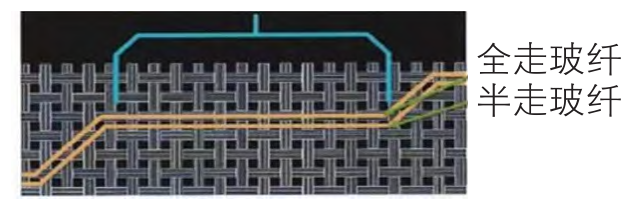

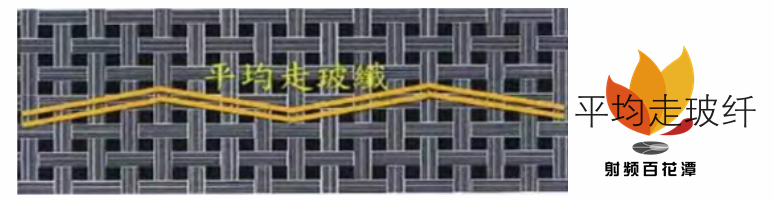

低频时玻纤布对PCB的电气性能影响较小,可以认为介质是均匀的,但高频时,介质层局部特性将会对PCB的电气特性有很大影响。因为玻纤布的相对介电常数和环氧树脂存在较大差异(环氧树脂约为3,玻纤布约为6),所以板面不同位置的介电常数存在差异,从而导致板面不同位置阻抗的差异。同时,同一阻抗线,由于位置不同,介电常数也不均匀,对于差分的影响更为明显,如图10和图11所示。针对上述现象,可能的一些解决方式为:

1)走线避开玻纤束的编织间距;

2)差分走线间距正好避开玻纤束的编织间距;

3)之字形走线;

4)带一定角度(一般15°角度倾斜)的走线;

5)设计人员旋转设计;

6)PCB厂家旋转基板;

7)使用高端基板材料;

8)使用更紧密的玻纤材料(玻纤束编织间距小)。

图10 不正确的高频走线

图11 正确的高频走线

3.1.2 去嵌入设计

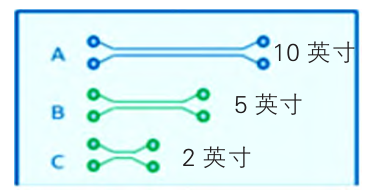

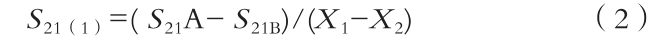

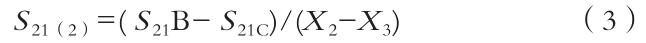

如图12所示,为了消除测试误差和过孔影响,设计三条不同长度的传输线,一般设计传输线线长分别为2英寸(1英寸=25.4 mm)、5英寸、10英寸。通过利用邻近的长短二组线路分别测试插损。二组数据相减除以长度差异即可知纯线路的插损值,可以比较两组插损数据对比的差异值,来判定此次测试插损的精准性。即结构A、B、C的插损值都为各自传输线插损值与过孔插损值的和。

图12 去嵌入设计

每英寸传输线插损值为:

每结构分成传输线插损值为:

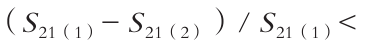

若两组传输线插损值

10%,则说明此次测试插损值精准性正常。

3.1 PCB产品插入损耗测试3.1.1 插入损耗

指输出端口的输出功率与输入端口的输入功率之比。

定义为:

式中:P i 为输入到输入端口的功率;P o 为从输出端口接收到的功率。

3.2.2 信号完整性

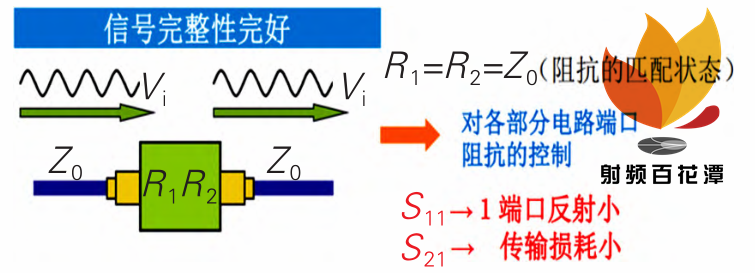

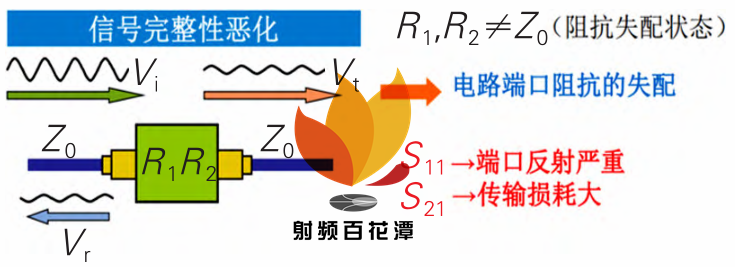

为了满足信号完整性,测试电性能插损之前,先要测试产品阻抗匹配到50 Ω或100 Ω,这个和测试电性能Loss(损耗)仪器设计有关,测试电性能Loss仪器一般都是采购单端50 Ω,差分100 Ω的设计。产品的阻抗与仪器端口阻抗匹配时,测试端口几乎没有反射,测试插入损耗准确(如图13所示);如果产品的阻抗与仪器端口阻抗不匹配及失配的状态下,就会导致测试插入损耗时测试端口反射严重,导致测试插入损耗误差大,测试结果不准确(如图14所示)。

图13 信号完整性完好

图14 信号完整性恶化

3.2.3 插入损耗测试

常用的插入损耗测试方法有探针台法、PLTS-AFR法和Delta-L法。表1是这3种测试方法的介绍。

表1 三种插入损耗测试方法

4 结论

本文简述了高频时代PCB产品的信号完整性电性能的测试。主要内容包括:1)PCB原材料介质层的D k 、 D f 以及导体铜箔粗糙度测试方法,可以直接评估高频原材料的电性能,可以指导工厂选择最优电性能的PCB原材料;2)PCB产品的阻抗与插入损耗设计与测试方法,介绍了如何通过阻抗设计匹配提高插入损耗测试精度,以及根据市场需求、测试频率、操作方便性、测试精度选择什么类型的插入损耗测试夹具作为测试参考。

作者:房兰霞 来源:电子工艺技术

审核编辑:汤梓红

-

浅谈影响PCB信号完整性的关键因素2023-06-30 2684

-

技术资讯 | 信号完整性测试基础知识2025-04-11 2626

-

PCB信号完整性2018-11-27 2733

-

高速PCB电路板的信号完整性设计2017-11-08 1678

-

基于信号完整性分析的PCB设计解析2017-12-04 1846

-

PCB信号完整性有哪几步_如何确保PCB设计信号完整性2018-05-23 12249

-

如何确保PCB设计信号完整性的方法2022-12-22 1586

-

硬件的单元测试:信号完整性测试2023-02-13 7647

-

信号完整性测试概述2023-02-23 3705

-

pcb信号完整性详解2023-09-08 2553

-

信号完整性设计测试入门2023-09-21 3291

-

PCB电流与信号完整性设计.zip2022-12-30 1150

-

高速PCB的信号完整性、电源完整性和电磁兼容性研究2024-09-19 1186

-

高速PCB信号完整性设计与分析2024-09-21 717

-

高速高密度PCB信号完整性与电源完整性研究2024-09-25 790

全部0条评论

快来发表一下你的评论吧 !