关于DC-DC电路中电感的特性与选择

电子说

描述

对于一名硬件工程师来说,电感是常用的元器件,本文将重点分析电感在DC-DC设计中的运用。只有充分理解电感在DC/DC电路中发挥的作用,才能设计出优秀的DC/DC电路。

在开关电源的设计中电感的设计为工程师带来的许多的挑战。我们不仅要选择电感值,还要考虑电感可承受的电流,绕线电阻,机械尺寸等等。本文专注于解释:电感上的DC电流效应。这也会为选择合适的电感提供必要的信息。

理解电感的功能

电感常常被理解为开关电源输出端中的LC滤波电路中的L(C是其中的输出电容)。虽然这样理解是正确的,但是为了理解电感的设计就必须更深入的了解电感的行为。在BUCK降压转换器中,电感的一端是连接到DC输出电压。另一端通过开关频率切换连接到输入电压或GND。

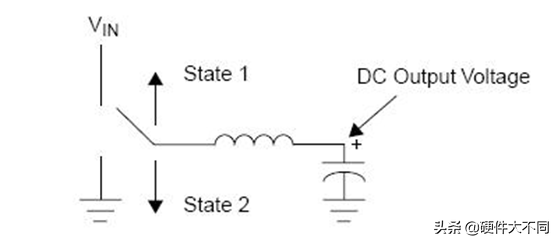

图1

在状态1过程中,电感会通过(高边 “high-side”)MOSFET连接到输入电压。在状态2过程中,电感连接到GND。由于使用了这类的控制器,可以采用两种方式实现电感接地:通过二极管接地或通过(低边“low-side”)MOSFET接地。如果是后一种方式,转换器就称为“同步(synchronus)”方式。

现在再考虑一下在这两个状态下流过电感的电流是如果变化的。在状态1过程中,电感的一端连接到输入电压,另一端连接到输出电压。对于一个降压转换器,输入电压必须比输出电压高,因此会在电感上形成正向压降。相反,在状态2过程中,原来连接到输入电压的电感一端被连接到地。对于一个降压转换器,输出电压必然为正端,因此会在电感上形成负向的压降。我们利用电感上电压计算公式:V=L(dI/dt)

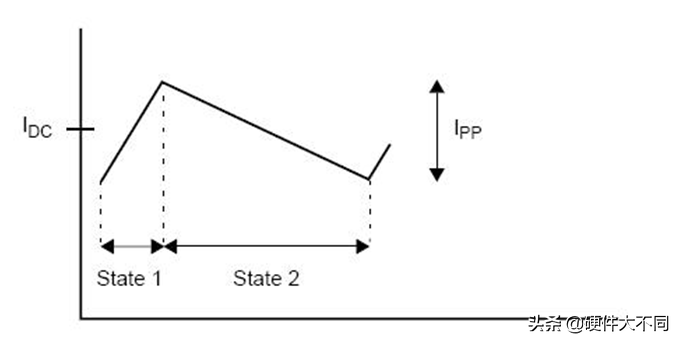

因此,当电感上的电压为正时(状态1),电感上的电流就会增加;当电感上的电压为负时(状态2),电感上的电流就会减小。通过电感的电流如图2所示:

图2

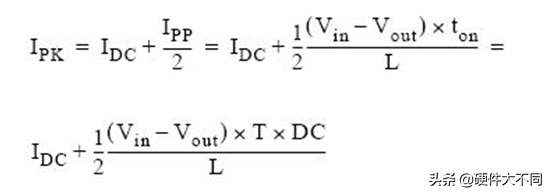

通过上图我们可以看到,流过电感的最大电流为DC电流加开关峰峰电流的一半。上图也称为纹波电流。根据上述的公式,我们可以计算出峰值电流:

其中,ton是状态1的时间,T是开关周期(开关频率的倒数),DC为状态1的占空比。

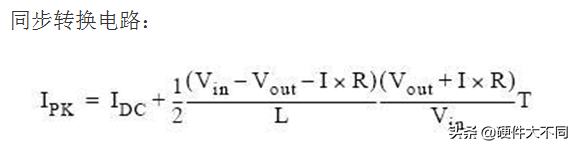

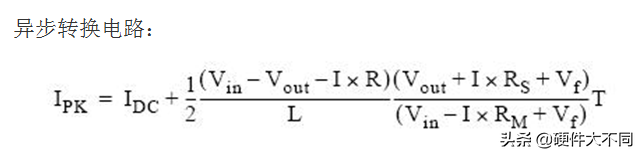

注意:上面的计算是假设各元器件(MOSFET上的导通压降,电感的导通压降或异步电路中肖特基二极管的正向压降)上的压降对比输入和输出电压是可以忽略的。如果,器件的下降不可忽略,就要用下列公式作精确计算:

其中,Rs为感应电阻阻抗加电感绕线电阻的阻。Vf是肖特基二极管的正向压降。R是Rs加MOSFET导通电阻,R=Rs+Rm。

电感磁芯的饱和度

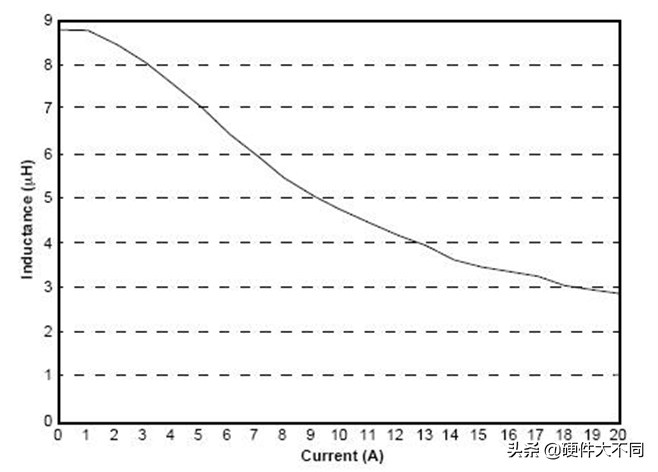

通过已经计算的电感峰值电流,我们可以发现电感上产生了什么。很容易会知道,随着通过电感的电流增加,它的电感量会减小。这是由于磁芯材料的物理特性决定的。电感量会减少多少就很重要了:如果电感量减小很多,转换器就不会正常工作了。当通过电感的电流大到电感失效的程度,此时的电流称为“饱和电流”,这也是电感的基本参数。

实际上,转换电路中的开关功率电感总会有一个“软”饱和度。要了解这个概念可以观察实际测量的电感Vs DC电流的曲线:

当电流增加到一定程度后,电感量就不会急剧下降了,这就称为“软”饱和特性。如果电流再增加,电感就会损坏了。

有了这个软饱和的特性,我们就可以知道在所有的转换器中为什么都会规定在DC输出电流下的最小电感量;而且由于纹波电流的变化也不会严重影响电感量。在所有的应用中都希望纹波电流尽量的小,因为它会影响输出电压的纹波。这也就是为什么大家总是很关心DC输出电流下的电感量的原因。

直接转载来源:头条号(喝枸杞论电子)。

审核编辑:汤梓红

-

DC-DC Boost电路外围元器件如何选择?2024-06-04 1358

-

如何计算DC-DC的电感值2023-06-12 4008

-

降压型DC-DC转换电路之功率电感选型2023-05-12 4511

-

关于DC-DC电路中电感的特性与选择2023-04-07 1920

-

DC-DC电路中电感的特性与选择2023-03-29 2547

-

推荐一个DC-DC电路设计工具2023-03-17 7479

-

DC/DC电路中电感怎么选择2021-11-17 854

-

电感电流 ――DC/DC 电路中电感的选择2021-11-09 1220

-

深入剖析电感电流DC/DC电路中电感的选择2021-10-28 1737

-

如何选择DC-DC转换器输出的电容与电感2018-06-26 9958

-

教您设计:如何选择DC-DC的输出电容和电感2018-06-23 14860

-

DC-DC升压和降压电路电感参数选择详解2016-12-17 2950

-

DC-DC升压和降压电路中电感的参数选择详解2015-05-17 3974

-

DC/DC 电路中电感的选择2011-07-22 30522

全部0条评论

快来发表一下你的评论吧 !