Type-C新技术与接口芯片

描述

芯片测试大讲堂系列又和大家见面了。

本期,我们来聊聊基于消费类接口芯片Type-C,以及支持Type-C的技术规范USB和DisplayPort技术,内容涉及市场趋势,标准演进,设计与测试面临的挑战以及是德科技的解决方案等。

前言

Type-C接口尺寸小、支持正反插和多用途使其在消费类电子行业被广泛使用,围绕Type-C接口的生态蓬勃发展。仅Type-C接口上可支持USB4。USB4 V2规范将数据速率提升至80Gbps使得消费电子产品接口性能有极大提升,以高端笔记本为例,可通过USB4扩展坞连接高端显示器、移动硬盘盒及U盘等外设,满足8K甚至更高y分辨率视频、数据文件同时高速传输要求。高端游戏显卡通常是双HDMI2.1和双DP1.4a配置,连接不同标准的显示器,满足流畅、清晰游戏体验。

随着DP V2.1规范发布,显卡、台式机、笔记本、扩展坞和电缆等支持UHBR速率产品开始增多。UHBR信号4路同时传输,通过认证的DP40、DP80线缆连接高端显示器,满足8K@60Hz、16K@60Hz等显示要求。目前支持USB4 V2.0及DP V2.1接口的芯片与产品较少,仍处在研发阶段,需要IP核、芯片、产品生态链企业共同推动发展及落地。

USB与DisplayPort的标准演进

USB-IF于2022年10月18日发布USB4 Version 2.0规范,替代USB4 Version 1.0规范,主要变化包括:

•是数据速率翻倍到80Gbps;

•支持非对称链路;

•借助Tunneling技术承载PCIe4.0、DP V2.1数据包;

•在低功耗状态仍旧不损失时间同步精度;

•支持交替模式。

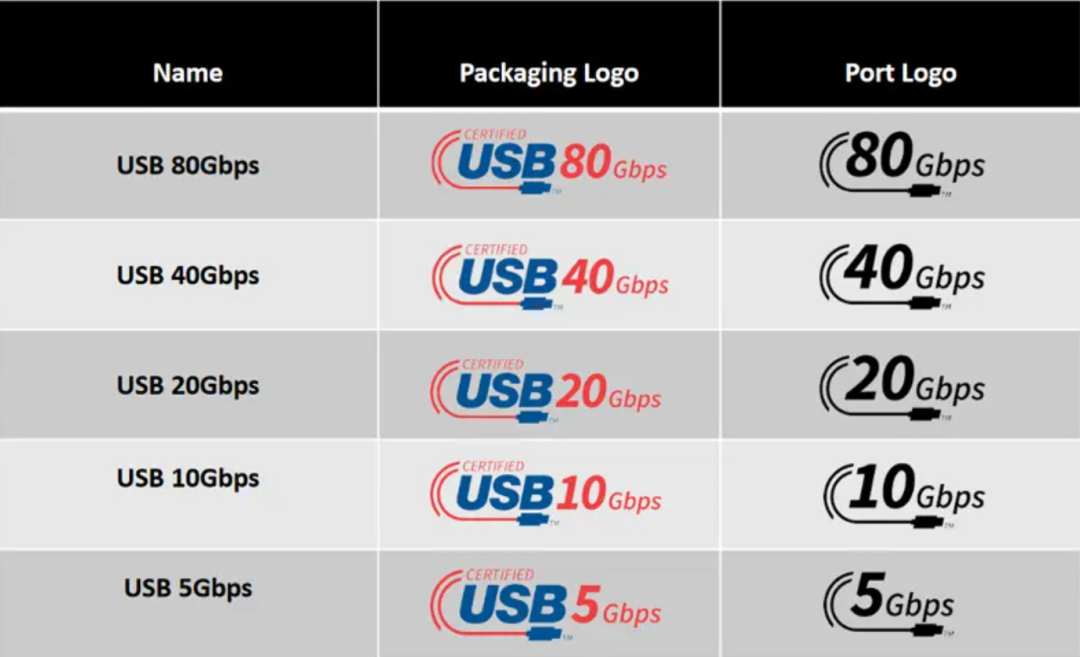

随着新规范的发布,USB接口将统一以传输带宽命名,USB4 V2.0对应USB 80Gbps,USB4对应USB 40Gbps,USB 3.2 Gen2x2对应20Gbps,USB 3.2 Gen2对应USB 10Gbps,USB 3.2 Gen1对应USB 5Gbps。

来源:USB-IF与USB Implementers Forum

VESA在同月发布DP V2.1规范,替代V2.0,性能、互连与USB4 V2.0对齐。DP V2.0规范支持128b/132b编码、UHBR10、UHBR13.5、UHBR20速率,可选支持Pannel Replay功能(满足系统降功耗和未来自适应同步功能),必须支持DSC能力。DP V2.1规范不仅支持DP线缆、USB-C to DP适配器,而且支持USB-C线缆,增加了ALPM电源管理功能,可在Pannel Relay及Adaptive-Sync操作时使能,考虑兼容HDMI,也提出协议转换器DP到HDMI的要求。

USB与DisplayPort设计和测试面临的挑战

USB与DP标准的速率变化:

USB-IF在USB4 V2规范中增加Gen 4模式,将单路速率提升至25.6GBd。通过建立11-bits到7-trits映射(每个trit有0/1/2状态),实现1个符号承载1.57 bits,相比理论极限1.58bits,效率超过99%。信令格式变化,USB-IF在USB4 V2中首次采用PAM3调制格式,相比同幅度NRZ,其信噪比下降6dB,与PAM4比较,其电平判决阈值与迟滞放宽,噪声容忍度增强,是综合考虑性能、Type-C信道、时延和信噪比因素满足原始Trit Error Ratio/1E-8唯一的调制格式。DP V2.1相比DP V2.0,速率没变化,功能及线缆兼容等方面有变化。USB4 V2和DP V2.1用于Router/Host/Device/Captive Device和Source/Sink/DP Cable开发的标准已发布,但物理层一致性测试标准还在草稿阶段。

下面结合仿真和测试,从发送、互连和接收三个方面展开介绍。

01发送端:

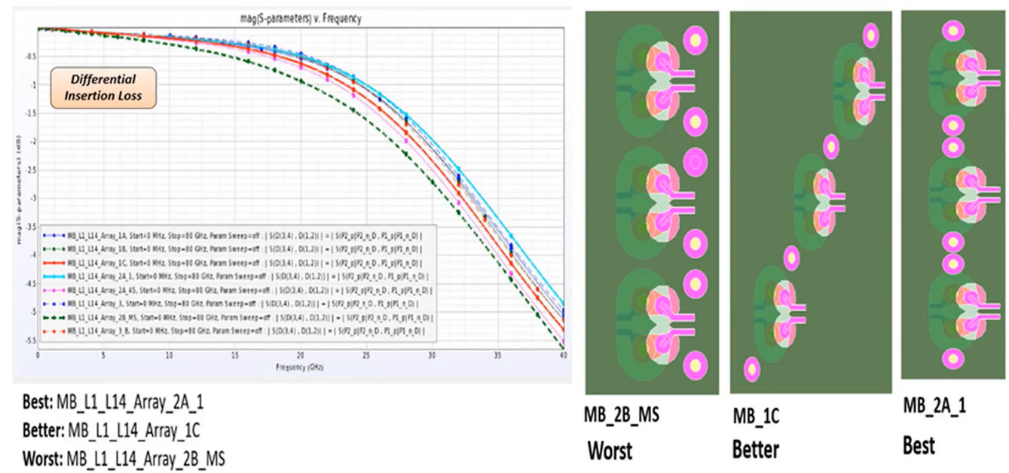

从仿真的角度:需构建IBIS-AMI模型且可修改其参数,支持NRZ、PAM3调制格式。USB4 V2相比V1,增加Gen 4及非对称工作模式。Gen 4模式单路速率25.6GBd/40Gbps,在非对称情况下,3路同时发送,总速率达120Gbps,1路接收,速率是40Gbps。DP V2.1 UHBR最高速率达20Gbps,4路同时传输,信号质量、串扰影响、过孔、过孔阵列、走线、特性阻抗等设计约束均需严格考虑。

图:过孔阵列设计优化及插损对比[1]

从一致性测试的角度:USB4 V2与V1都需使用协会发布的控制软件。该软件通过sideband信号写配置空间寄存器8/9/18,实现port operation,产生测试信号。USB4 V2使用PRTS7测试码型,该码型实现多电平序列。为克服PAM3多电平信号高频损耗,USB4 V2 Gen 4 Tx FFE 比Gen 3多一个precusor-c[-2],Preset数量达42个,明确了归一化的每个抽头系数波动范围。新增TP2多项时域测试参数,比如Level Mismatch、Steady State Voltage、Linear Fit Pulse、SNDR、ISI Margin等,不在使用眼图模板进行约束,增加频域积分回波损耗参数,频率覆盖到20GHz,差分回波损耗模板测试降为Informative项,其频率覆盖到14GHz。DP V2.1相比DP V2.0速率不变,都需使用协会认证的aux channel controller实现 TP2及TP3_EQ自动化测试。DP V2.1 Tx FFE Preset达16种,TP2测试需使用DDJ最小的Preset,Reference CTLE达10种,TP3_EQ眼图与抖动测试需使用160种组合中Eye Area最大的一个组合,测试花费大量时间,VESA协会也在优化测试方法。

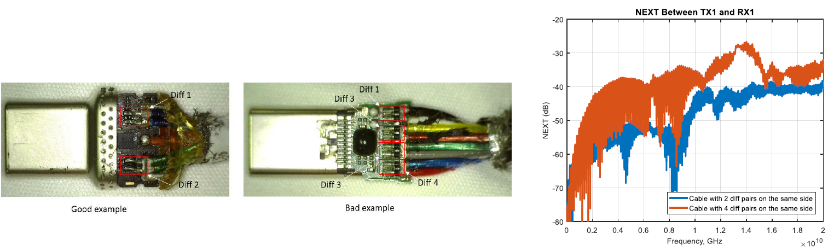

从互连的角度:USB4 Gen 4仅支持Type-C互连,相比Gen3奈奎斯特频点增加2.8GHz,系统损耗预算相比Gen 3放宽6dB,6dB三等分分配到Host、Cable及Device。Host/Device的损耗预算包含封装、pcb线、共模电感、防护器件、耦合电容、连接器。Gen 4可使用0.8米Gen 3线缆,若传输更远距离,需使用LRD线缆。USB 4 Gen 3/Gen 4 Type-C线缆相比USB 3.2 Type-C线缆增加了更严格的覆盖频率范围的积分参数,比如积分多次反射、积分回波损耗、积分串扰等。另外还引入COM方法进行电缆质量评估。Gen 3使用COM,Gen 4使用eCOM。相比COM,eCOM门限大于等于0 dB,信道仅支持S参数导入,不支持信道特性阻抗、衰减、长度参数,增加了接收端抖动和噪声参数。DP V2.1 UHBR信号可在增强型DP/mDP及Type-C接口上通过DP40/DP80电缆进行互连,其中UHBR20信号包含Source/Sink/DP80端到端损耗预算约22.5dB。DP40电缆可支持到UHBR10,长度约1m/1.5m/2m,DP80电缆可支持到UHBR20,两者已有商用认证产品。DP40/80电缆都包含Cable ID,相比DP8K电缆,增加了对间时延参数。

图:USB Gen3/20Gbps近端串扰影响[2]

02接收端:

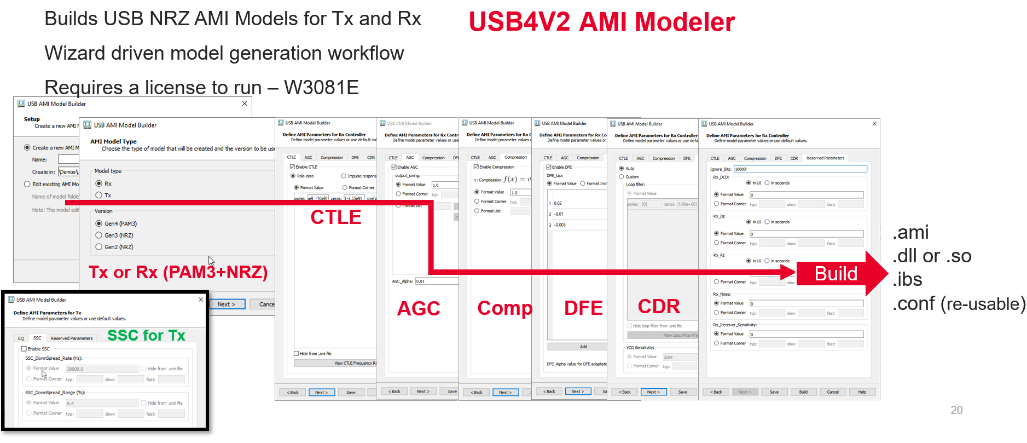

从仿真的角度,需支持PAM3接收机内部模块参数调整,比如CTLE、AGC、Compression、DFE和CDR。

从接收一致性的角度:校准环境下Gen 4相比Gen 3,压力参数ACCM noise大小不变,RJ/PJ大小降至约一半,不在使用眼图约束,而是通过SNDR/RLM/Jitter约束。测试场景包括case 1和case 2。Case 1是直连。case 2包括额外电缆,有USB4 Gen 3 passive cable互连和USB Type-C LRD Cable互连两种场景。测试情况下,需支持多种码型及切换,初始PRBS11不带SSC用于接收机训练,切至PRTS7,带校准的压力参数和优化的Preset用于第2次训练,切至PRTS19,带pre-coding和3400ppm下展频的SSC用于Case 1测试,带pre-coding和3000ppm的下展频用于case 2测试。DP V2.1与DP 1.4a使用相同DPCD寄存器,控制物理层测试模式,寄存器在不同编码时(8b/10b和128b/130b),功能不同。UHBR20 Sink校准参数类型与USB4 Gen 3一样,但TP1和TP3_EQ眼图幅度和眼宽略有压缩,链路训练方法有更新,规范要求被测件物理逻辑子层必须支持128b/132b LANEx_CHANNEL_EQ_DONE和LANEx_CDS_DONE/LANEx_SYMBOL_LOCKED/INTERLANE_ALIGN_DONE两个任务,接收原始误码率小于等于1E-9,置信度大于99.9%。

是德科技测试方案

是德科技提供仿真、物理层发送一致性测试、接收一致性测试和互连一致性测试整体方案。

仿真平台PathWave可提供W3801E软件,帮助用户建立并修改USB AMI模型。该软件可支持NRZ、PAM3信号格式,提供收发及参考信道模型。以Rx为例,提供CTLE功能支持Pole-zero、Impulse response和Step response方法、AGC功能支持Output Swing和Alpha参数调整、增益压缩选项支持电路非线性影响修正、DFE功能支持多抽头系数调整、提供CDR支持自动和手动调整环路滤波器/VCO灵敏度、提供Rx_DCD/Rx_Dj/Rx_Rj/Rx_Noise/Rx_Receiver_Sensitivity保留参数。DP V2.1技术可借助该选件完成相应参数调整。

图:USB4 V2 AMI Modeler-W3801E

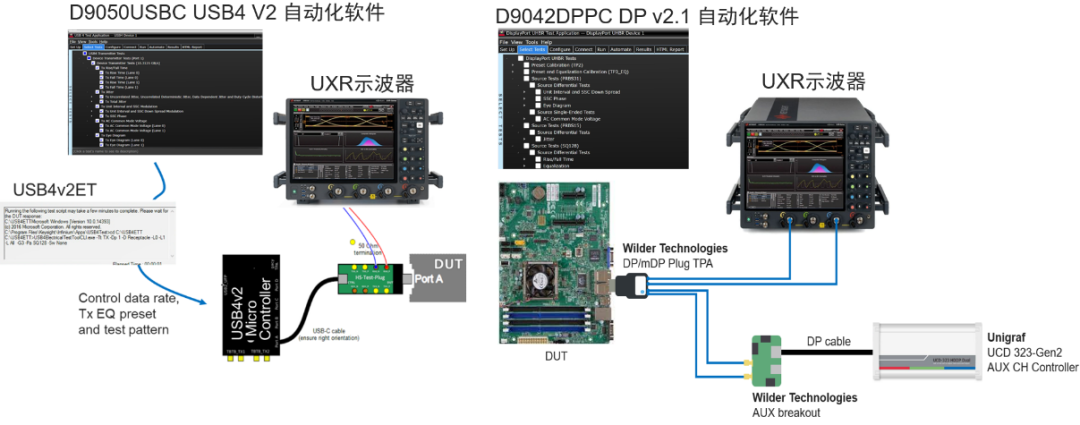

基于UXR高性能实时示波器平台推出D9050USBC物理层一致性测试软件,覆盖USB4 V2.0标准,支持25.6GBd PAM3信号自动化测试。也推出了D9042DPPC软件,覆盖DP V2.1标准Source测试。UXR实时示波器模拟带宽覆盖5GHz~110GHz,集成10 bit高速ADC,固有抖动小,本底噪声低,支持规范提及的噪声移除功能,可满足未来多年高速信号精确测试。

图:USB4 V2 Tx&DP V2.1 Source测试方案

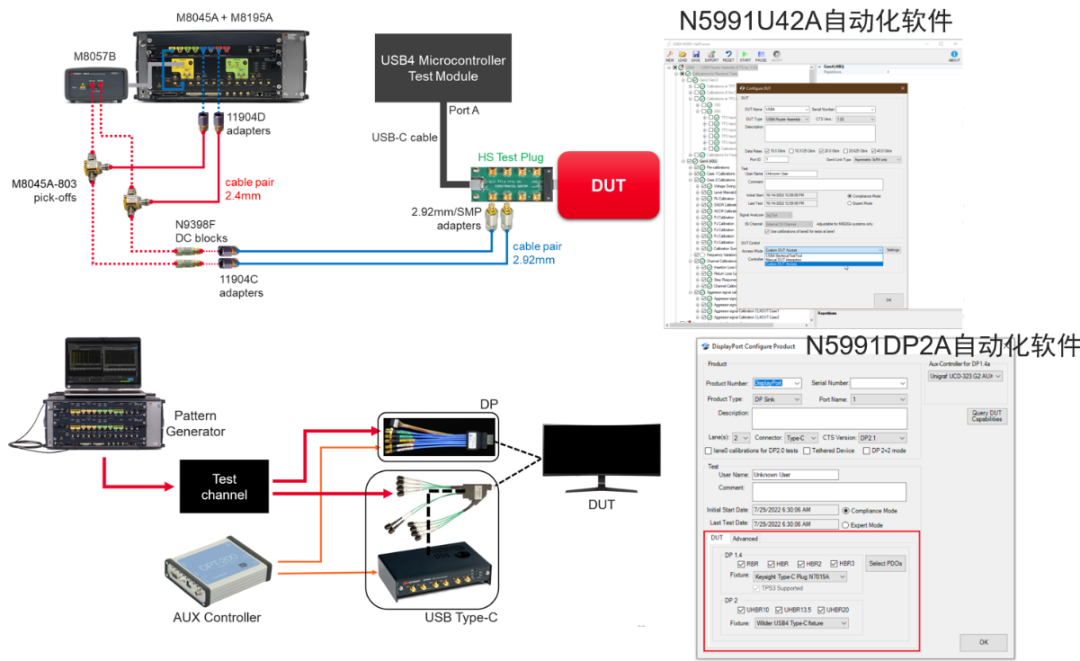

基于M8040A高性能误码仪平台推出了N5991U42A物理层接收一致性测试软件,可产生USB4 V2.0要求的PAM3格式信号和PRBS/PRTS码型,并支持注入PJ、RJ及SSC压力,实现接收抖动容限自动测试。也推出了N5991DP2A软件,覆盖DP V2.1标准,支持DP V2.1 Sink接收抖动容限测试。

图:USB4 V2 Rx&DP V2.1 Sink测试方案

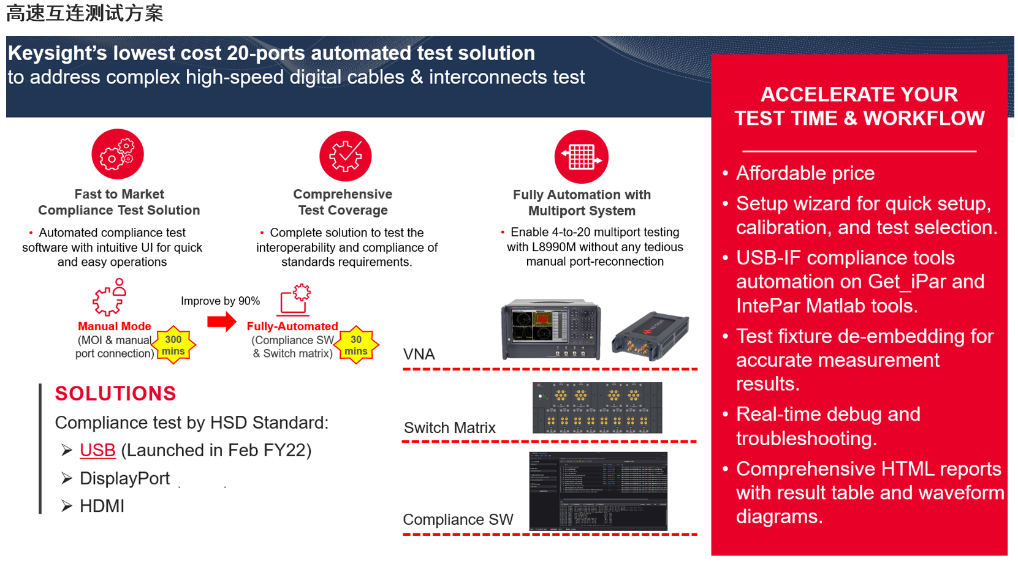

基于ENA/Streamline USB/PXI矢量网络分析仪和开关矩阵推出S94USBCB USB Type-C互连一致性测试软件,提供向导方便完成参数配置、校准及测试,支持去嵌入和AFR功能可实现精确测量,覆盖USB2/3/4标准,支持 Type-C电缆、连接器和裸线测试。

图:USB等高速互连测试方案

综上所述,目前支持USB4 V2.0及DP V2.1接口的芯片与产品较少,仍处在研发阶段,需要IP核、芯片、产品生态链企业共同推动发展及落地;是德科技作为USB-IF与VESA的协会成员,一直致力与业界各企业协作,共同推动规范的完善与测试方案的开发,更多的有关于Type-C的内容,请参考下载资料。

同时也感谢大家一直以来对是德科技的支持,我们准备了精美的抽奖,大家如果有更多的需求,也可以留言给我们。

审核编辑:汤梓红

- 相关推荐

- 热点推荐

- 接口

- usb

- 接口芯片

- DisplayPort

- type-c

-

USB Type-C接口应用2017-08-15 13837

-

type-c是什么接口?type-c和普通接口有什么区别2018-03-09 628423

-

东芝推出采用Type-C接口的双面USB,Type-C接口使用简单方便2018-09-08 6189

-

TYPE-C接口介绍 type-c接口是什么形状2021-09-24 21522

-

Type-c接口是什么 有哪些特点2022-08-19 34102

-

Type-C接口有什么特点?你知道工业级Type-C和普通Type-C有何区别?2023-02-14 10102

-

type-c和USB-c有什么区别 type-c和USB-c接口原理2023-09-01 39932

-

Type-C接口供电优势 Type-C接口供电接法详解2023-12-29 18568

-

国产Type-C接口芯片:PD取电协议芯片Type-C拓展坞 PDHUB 取电IC方案2024-01-04 2873

-

type-c接口的重要性2024-01-07 1884

-

小家电Type-C接口 PD技术方案2024-03-07 2153

-

Type-C接口芯片:现代电子设备的连接核心2024-05-27 4672

-

Type-C接口协议诱骗芯片LDR65002024-06-14 2951

-

LDR6500 type-c 接口 PD协议芯片2024-07-29 2197

-

usb接口与type-c接口区别2024-10-10 14377

全部0条评论

快来发表一下你的评论吧 !