通过仿真了解和缓解电机驱动板寄生效应

描述

本文探讨了如何使用 PSpice for TI 来仿真电机驱动设计中寄生效应的潜在原因,并提供设计技巧来减轻大功率电机驱动系统中常见的负面影响。

大功率系统设计中最令人沮丧的部分之一是寄生效应的结果往往难以捉摸。这尤其适用于大功率电机驱动系统,其中大型电路板设计、大型元件和高输出电流可能导致输出振铃、元件额定值过高或辐射电磁干扰 (EMI)。在本文中,我将使用 适用于 TI 的 PSpice® 模拟电机驱动设计中寄生效应的潜在原因,并提供减轻负面影响的设计技巧。

什么是大功率电机驱动设计?

作为一个完全沉浸在电机驱动系统中的人,我经常理所当然地认为如何根据特定挑战构建电机驱动系统的基础知识。寄生分析在大功率系统中变得至关重要有两个很好的理由。

首先,高功率带来高电流:在电机中切换 1 A 与在电机中切换 100 A 的效果不同。在高电流下,印刷电路板(PCB)上固有的所有寄生电感和电容都会跳出并开始引起麻烦。保持电流越低,这些寄生元件的重要性就越小。然而,对于具有定义的高输出功率的系统,目标输出电流是固定的 - 将设计设置为与任何杂散电感和电容的碰撞过程。

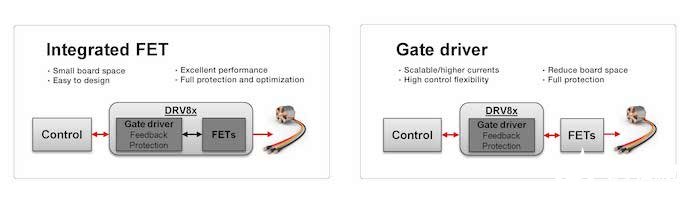

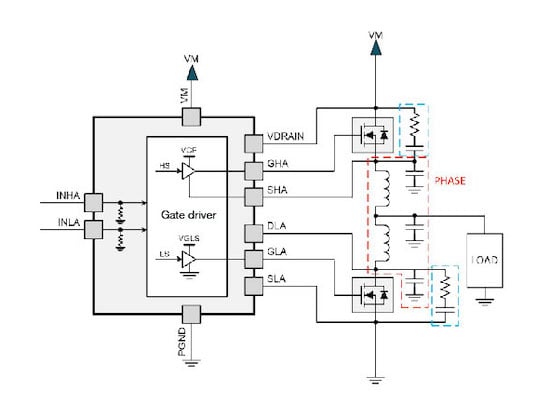

其次,大功率电机驱动系统需要栅极驱动器架构。电机驱动器有两种类型:集成 FET(场效应晶体管)和带有外部 FET 的栅极驱动器——见图 1。集成 FET 电机驱动器对于低功率系统非常有效,因为它们集成了栅极驱动器、功率级和任何其他传感和保护集成在一个封装中。这些器件也非常小——例如,DRV8837C仅为 2x2 毫米,因此它们显着降低了电路板寄生效应。

不幸的是,即使是最高电流的集成 FET 解决方案(例如DRV8873-Q1能够驱动高达 10 A 的电流),您也无法驱动 100 A 电机,因此需要栅极驱动器架构。当将栅极驱动器与外部分立 MOSFET 一起用于电机驱动器系统时,电路板上的组件之间总会有一些 PCB 走线,这会导致寄生效应。

图 1.

集成 FET 与栅极驱动器架构

栅极驱动电路和外加脉冲

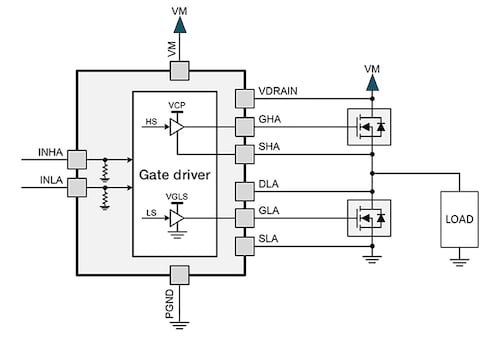

为了构建要分析的电路,让我们从简化的半桥电机驱动器开始(图 2)。我在这个电路中使用的电机驱动器是德州仪器(TI) DRV8343-Q1,带分流放大器的三相智能栅极电机驱动器。MOSFET 是 TI 的 CSD18540Q5B 我选择的栅极驱动强度 (IDRIVE) 是 15mA 拉电流和 30 mA 灌电流。为简单起见,我只使用了一个相位并创建了一个模型负载(240 mΩ和50 μH)。本例中使用的电源为24 V。

图2.

简化的驱动电路(无寄生元件)

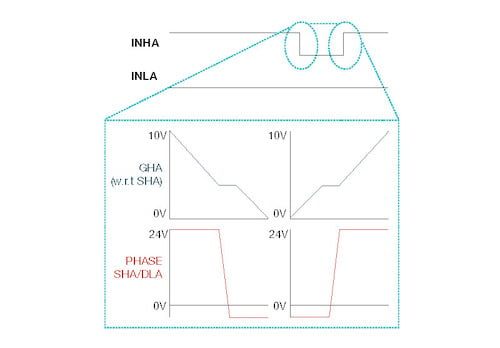

接下来,我模拟了一个“脉冲测试”,其中包括打开高侧 MOSFET 一段时间,然后在大量电流流过电路时快速关闭和打开它。模拟脉冲测试将使您能够观察在高侧 MOSFET 关闭和重新打开时输出的下降沿和上升沿产生的任何影响。

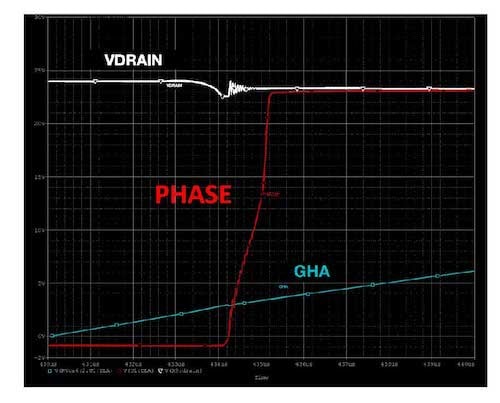

在图 3 中,您可以看到应用的控制信号、高侧栅极的预期理想波形和输出电压。在此仿真中,高侧 MOSFET 导通 400 µs,脉冲低电平 30 µs,并在剩余的 70 µs 中变为高电平。低侧 MOSFET 保持关闭状态,因此任何流过低侧 MOSFET 体二极管的电流都会传导。

图 3.

脉冲测试波形(无寄生元件)

添加寄生元件并进行仿真

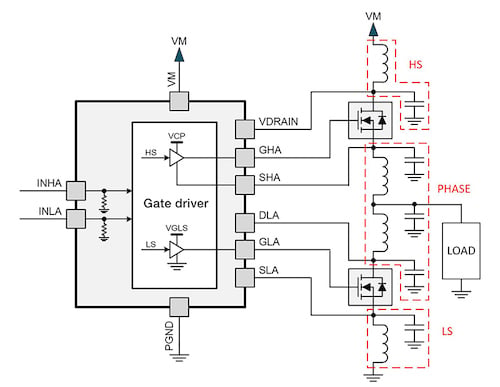

如果在这个电路中加入预期的寄生元件,复杂度会增加得相当快;电路原理图不再看起来“不错”。为此,您需要在三个地方添加重要的寄生组件:

在电源和高侧 MOSFET (HS) 之间。

在接地和低侧 MOSFET (LS) 之间。

在高侧和低侧 MOSFET (PHASE) 之间。

在这三个位置,您通常会在 PCB 上看到非常大的迹线,对应于高载流网络。看一下图 4。

图 4.

带有寄生元件的驱动电路

对于寄生值,我使用了以下内容:

高侧 (HS):10 nF、5 nH/10 mΩ。

相位 (PHASE):2 nF、2 nH/2 mΩ(每条路径,在输出到负载上额外增加 10 nF)。

低侧 (LS):10 nF、5 nH/10 mΩ。

由于这只是一个模拟,我使用了(可能)夸大的寄生电感和电容。可以设计一种最小化这些寄生元件的电路板,从而使缓解更容易(尽管遵循相同的过程)。相反,设计不佳的PCB可能具有更多的寄生电感和电容,这使得减轻寄生效应变得更加困难。为了回顾电机驱动器的布局技术,我推荐 电机驱动器电路板布局的最佳实践 应用说明。

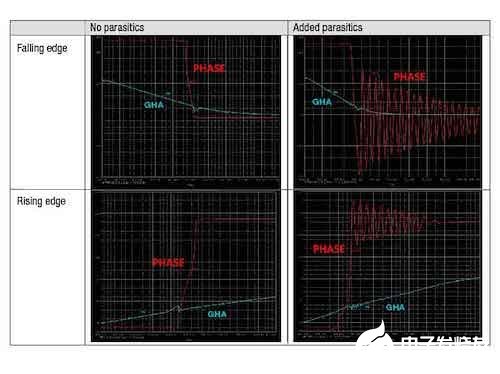

当我在添加这些寄生元件之前(图2)和之后(图4)仿真电路时,我有一种压倒性的感觉,我把电路弄坏了。请看图5,可以看到切换高电平或低电平时相位的显著振荡。减轻这些影响以保护电路免受损坏(例如–20 V负电压尖峰)或防止任何不需要的电磁辐射(振荡网络将充当天线)非常重要。

图5.

添加寄生元件前后用于TI仿真的PSpice结果

为了找出最佳的缓解措施,让我们逐个分解不同的寄生组件,并模拟每个组件的效果。

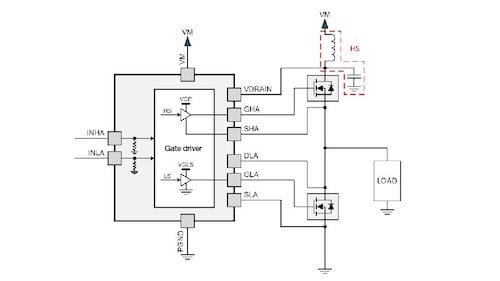

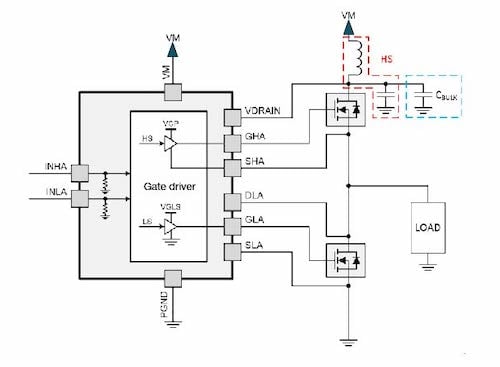

电源和高边 MOSFET (HS) 之间的寄生元件

当我在电源和高边MOSFET之间添加寄生元件时(图6),仿真显示上升沿输出端的振荡非常明显(图7)。深入研究更多细节,您可以看到振荡来自高端MOSFET(VDRAIN)的漏极。在下降沿,当高端MOSFET关断时,即使输出不受影响,您也会看到同样的效果。

图6.

在高端路径(HS)中具有寄生效应的驱动器电路

图7.

在高边路径(HS)中添加寄生效应的情况下模拟上升沿

在此阶段,您可能会认为需要添加缓冲器,或者压摆率过高,需要降低。考虑一下:缓冲器在减少相位振荡方面最有效,而不是VDRAIN振荡。为了进行研究,我在高端和低端MOSFET上实现了1.2 Ω和33 nF的缓冲器。您可以在图8中看到效果,其中VDRAIN在开关事件之前仍然会丢失,因此这不是缓解振铃的最佳方法。

图8.

尽管有缓冲,但由于 VDRAIN 上的振荡,缓解效果不佳

要了解有关缓冲器设计的更多信息,请查看技术文章 电源提示:通过七个步骤计算 R-C 缓冲器.

减少振荡的另一种可能解决方案是降低压摆率,这在仿真中会显著减少但不能消除振铃(图 9)。由于开关损耗较高,压摆率降低会导致更多的功率损耗(更热的组件),应尽可能避免。在本例中,我将栅极驱动电流从15 mA源降低到1.5 mA源,上升时间延长了10倍。

图9.

尽管栅极驱动电流降低,上升时间较长,但由于功耗较高和持续振荡,缓解措施无效

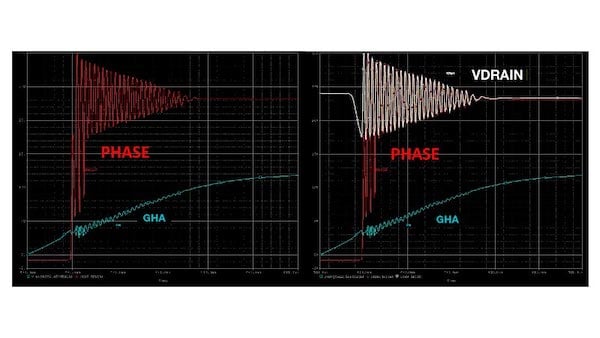

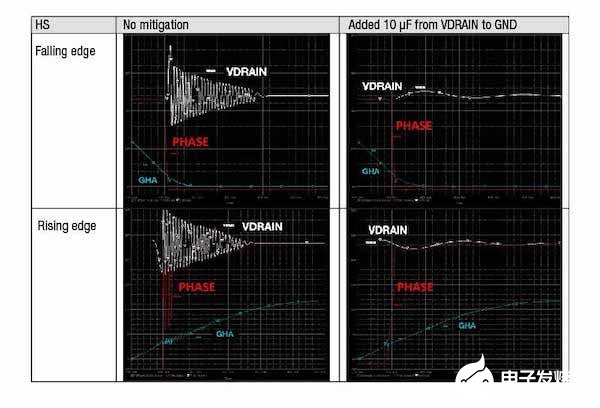

为了更好地缓解这些影响,让我们在VDRAIN节点上添加一个大容量电容(图10);这将使振荡明显变慢,振幅更小。我只是简单地使电感电容时间常数更长。图 11 显示了这种添加的结果。

在仿真中,增加大容量电容使峰值振荡从37 V(高于电源电压13 V)降至更易于管理的25 V(高于电源电压1 V)。该电容器必须尽可能靠近高端 MOSFET,以减轻电容器和 MOSFET 之间的任何额外寄生电感。陶瓷电容器是优选的,因为它们的引线电感较低,高频响应更好。

图 10.

在VDRAIN上增加一个大容量电容器

图 11.

使用大容量电容器(VDRAIN 至 GND)减轻高边寄生元件的影响

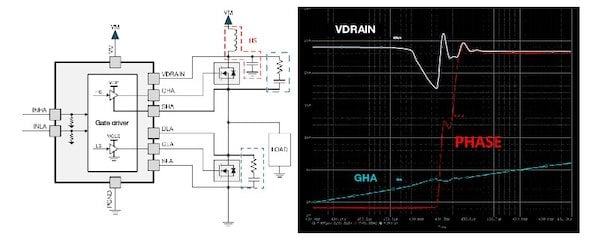

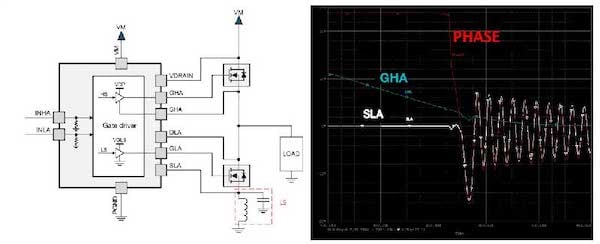

接地和低侧 MOSFET (LS) 之间的寄生元件

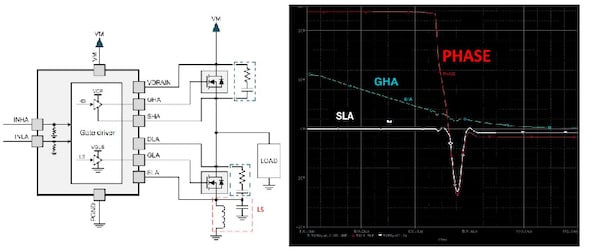

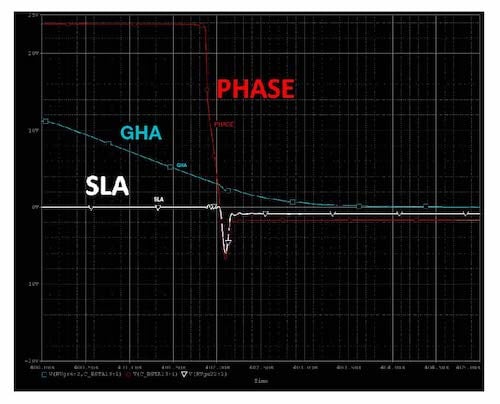

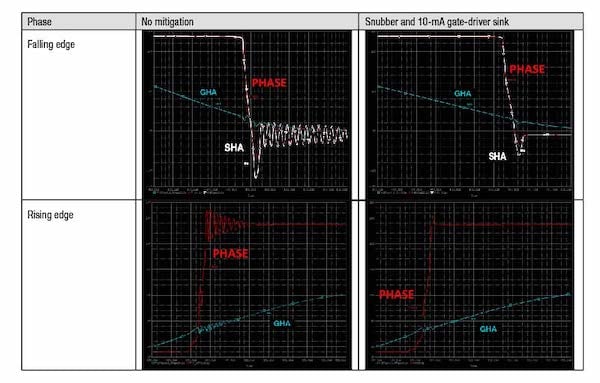

与高侧路径相比,低侧路径几乎相反。下降沿导致显著振荡,而上升沿则显得干净。仔细观察,您可以看到低侧 MOSFET 源极节点 (SLA) 在上升沿和下降沿均出现振铃效应(图 12)。

图 12.

在低侧路径(LS)中添加寄生效应的原理图和仿真

当面对这种情况时,你们中的一些人会想要添加缓冲器或延长上升时间来对抗振铃,但是,在这种情况下,您也应该避免这种方法。与之前一样,我在高端和低端MOSFET上实现了1.2 Ω和33 nF的缓冲器。结果是相位振荡显著改善,但初始负电压脉冲仍然存在(图 13)。

图 13.

尽管存在缓冲,但由于负电压尖峰,缓解措施无效

如果降低压摆率,振铃会显著减少(图14)。在本例中,栅极驱动电流从30 mA灌电流降至7 mA灌电流;下降时间延长>4倍。

图 14.

尽管栅极驱动电流降低,上升时间较长,但由于功耗较高,缓解措施无效

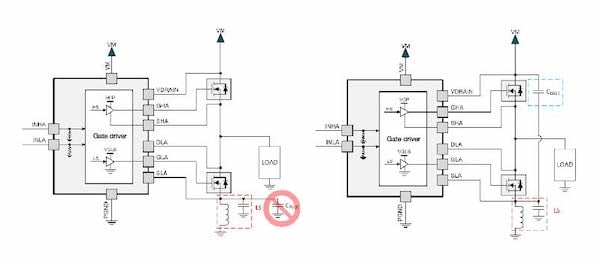

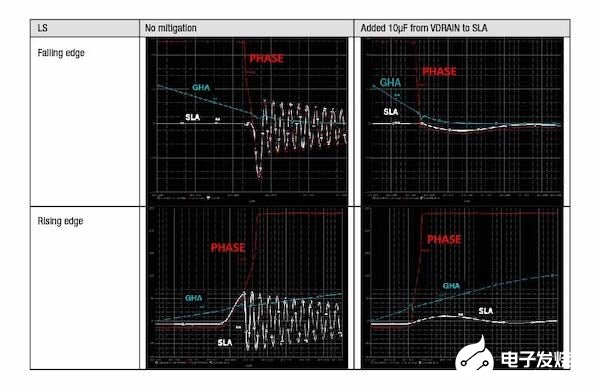

您可以对高边外壳采用类似的方法,并在电路板上增加额外的大容量电容来抵消这种振铃。但是,在这种情况下,您不希望在SLA到地增加一个大电容。大多数电机驱动系统使用电流检测电阻和电流检测放大器实现低侧电流检测。典型的 2512 封装检测电阻将具有 1 至 5nH 的寄生电感,从而为我们假设的寄生值提供了一定程度的可信度。

与检测电阻并联的超大电容器会抑制系统正确检测电流的能力(图 15)。添加此大容量电容器的正确位置是从VDRAIN到低侧源(SLA)。请记住,当添加该去耦电容时,仍然会对通过检测电阻的峰值电流产生一些影响。该电容的非常大的值将影响通过低侧电流检测得出的任何峰值过流限制。

图 15.

大容量电容器的放置不正确(左)和正确放置(右),以减轻低侧寄生效应

图 16 说明了这种添加的结果。在仿真中,增加大容量电容可将峰值振荡从–16 V显著降低到–3 V。 与前一种情况类似,该电容必须尽可能靠近高端MOSFET漏极和低侧MOSFET源极放置,以减轻电容器和MOSFET之间的任何额外寄生电感。陶瓷电容器因其较低的引线电感和更好的高频响应而更受欢迎。

图 16.

利用大容量电容器减轻低侧寄生元件的影响(VDRAIN 至 SLA)

MOSFET 之间的寄生元件(相位)

您可能已经了解到,应始终将高端和低端MOSFET尽可能靠近在一起,以便在开关时将寄生效应降至最低。这是非常好的建议,但你永远无法完全消除这些负面影响。

即使是最有效的多芯片 MOSFET 解决方案(参见 CSD88599Q5直流 例如)在高端和低端MOSFET之间仍将具有一些寄生电感和电容。MOSFET输出电容(COSS)和电机电缆电容(电缆长度较长)可能是PCB外相位节点电容的重要贡献者。

在这种情况下,不可能向电路增加额外的大容量电容来旁路寄生电感。电机的输出将切换高低电平,并且该网络上的其他大型电容器将反复充电和放电 - 这是一种非常低效的系统解决方案。发生这种情况时,最好先使用缓冲器作为第一个策略(图 17)。

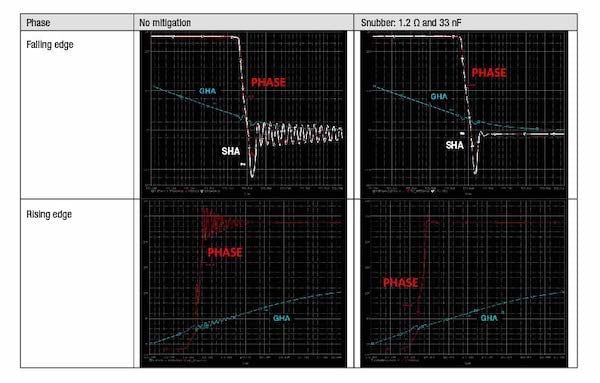

如果你是一个冷落的支持者,你可以松一口气——让我们现在就使用它们吧!您可以在图18中看到在电路中添加缓冲器的效果。

图 17.

在相路径(PHASE)和附加缓冲器中添加寄生效应的原理图

图 18.

使用缓冲器减轻相位寄生元件

缓冲器几乎完全解决了上升沿的振荡问题,并显著改善了下降沿的情况。与之前的实验一样,我在高端和低端MOSFET上实现了1.2 Ω和33 nF的缓冲器。然而,与低侧MOSFET寄生情况(图14)非常相似,第一个负脉冲仍然存在。

在这个阶段,您可以得出结论,为了完全克服这些寄生效应,需要增加下降时间。您必须改善图18下降沿上的–11 V负电压尖峰,以便保持在 DRV8343-Q1 (–7 V,200 ns)。将栅极驱动吸电流从 30 mA 降至 10 mA 时,将在最大额定值内得到该负尖峰(图 19)。

图 19.

通过缓冲器和降低栅极驱动电流吸收器减轻相位寄生元件

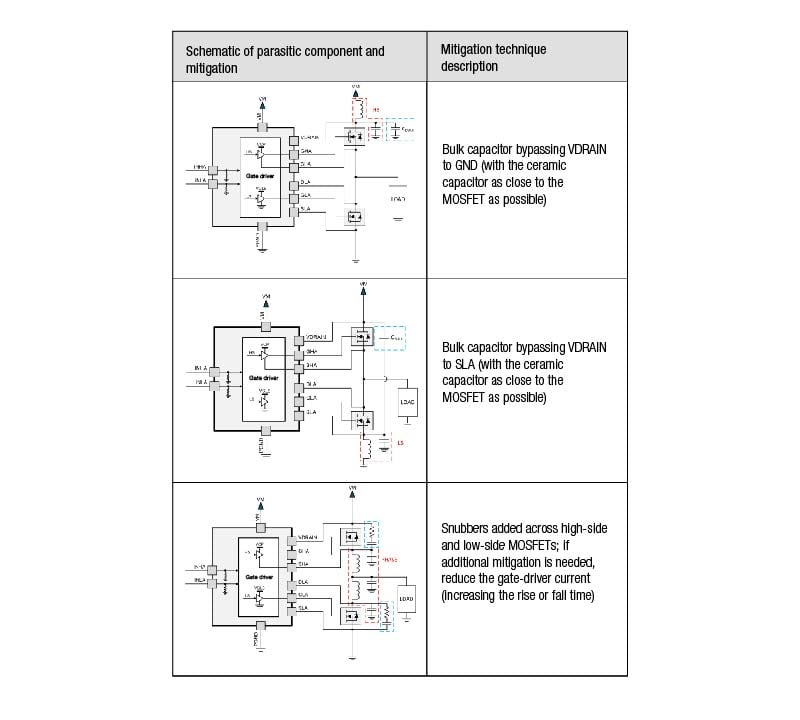

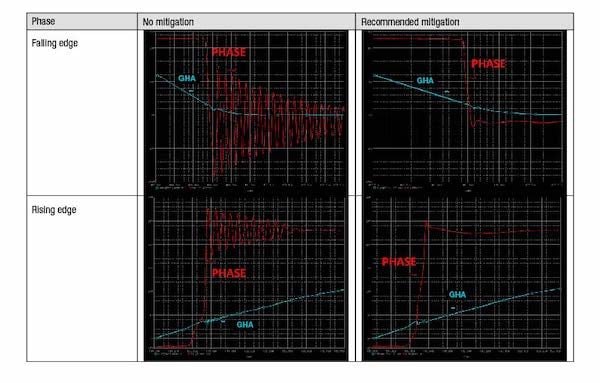

将一切整合在一起

那么,通过这次模拟练习,我们学到了什么呢?对于这三种常见的寄生效应(高压侧、低侧和相位),有三种不同的缓解技术。如果将本文所述的所有缓解技术应用于包含所有寄生元件的电路(表1),则可以显著减少过冲、下冲和振铃(图20)。

表 1.寄生元件抑制技术摘要

图 20.

使用概述的方法减轻所有寄生组件

这对我来说是一个特别有趣的练习,因为它给了我一个很好的机会来尝试 适用于 TI 仿真工具的 PSpice.这些仿真比物理电路板实验更容易、更快捷,并且可以很好地了解当您遇到电路板寄生效应的实际问题时该怎么做。

-

PCB布局的DC电阻,寄生电容和寄生电感2020-12-31 10153

-

求助: 树莓派驱动MOS(场效应)管电机驱动板时高电平无法设置的问题2017-10-25 7694

-

寄生电路的效应:Latch-Up(锁定)2018-08-23 6088

-

【高速PCB布线指南(2)】寄生效应2018-10-19 6713

-

如何减小过孔的寄生效应带来的不利影响?2021-04-21 1831

-

EMI 简介:标准、原因和缓解技术2021-08-31 2023

-

平衡MOSFET差分对中的模拟布局寄生效应2023-02-15 820

-

Spectre和Meltdown的利用漏洞的软件影响和缓解措施2023-08-25 533

-

减小高速PCB中过孔的寄生效应带来的不利影响的方法2018-01-27 8002

-

电容器的寄生效应对电路有何影响?2018-08-15 17240

-

寄生效应和Via及Ground Bounce的详细介绍和综合应用资料概述2018-10-22 3501

-

创新工具和开源软件如何帮助测量和缓解RF问题2019-07-23 3004

-

如何使用有源米勒钳位电路来减轻寄生效应2021-05-17 9406

-

EMI了解功率级寄生效应2022-01-20 2002

-

EMI 的工程师指南第 3 部分 — 了解功率级寄生效应2022-10-31 594

全部0条评论

快来发表一下你的评论吧 !