如何在通道中添加Retimer进行信号完整性仿真分析?

描述

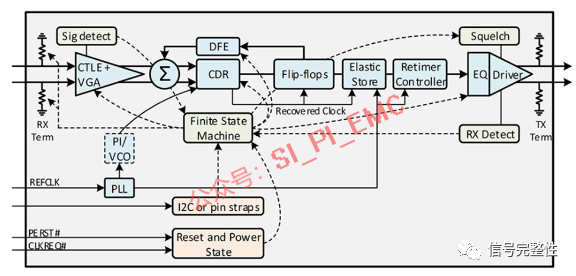

下面是Retimer的结构框图,其中包含了均衡、CDR等模块。

从框图中可以看到Retimer就类似于一颗PHY芯片,信号在经过Retimer的之后,通过内部均衡之后再通过CDR重构信号,使信号传输能力增加,再进行下一阶段的传递。所以信号经过了Retimer之后,降低了信号的抖动、恢复了驱动力能力,这样就传递的更远。以达到更好的信号完整性。但是,复杂的ReTimer会增加更多的潜伏时间。对于一些低传输延时的系统,要慎重使用。

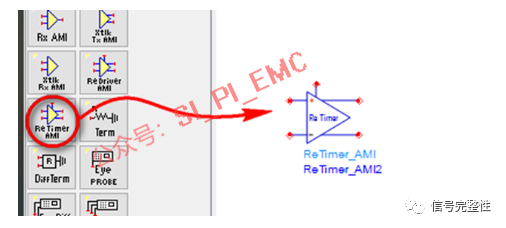

下面我们来看看如何在ADS中添加Retimer进行仿真分析。在ADS中有一个专门的Retimer模型元件ReTimer_AMI,如下图所示:

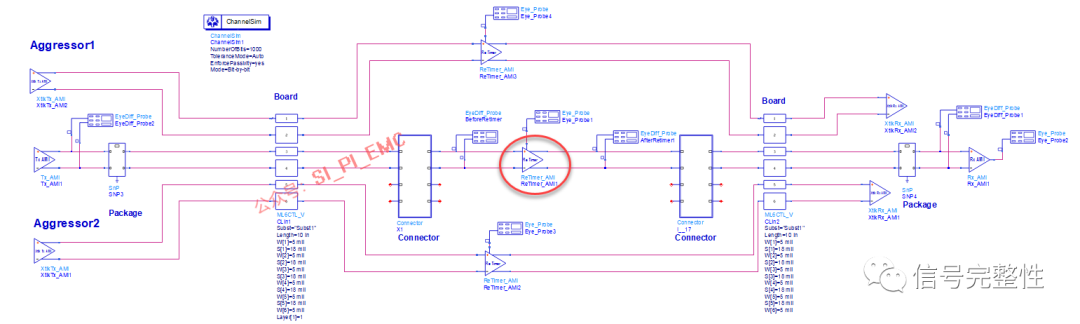

本文以PCIe3.0的仿真为例,由于在PCIe3.0的通道中损耗比较大,且有串扰的影响,所以导致信号不能满足信号完整性的要求,所以在链路中间添加了Retimer。建立带有Retimer元件的仿真原理图如下图所示(红色圈中为Retimer模型),在Retimer前后分别放置了两个Eye_Probe。

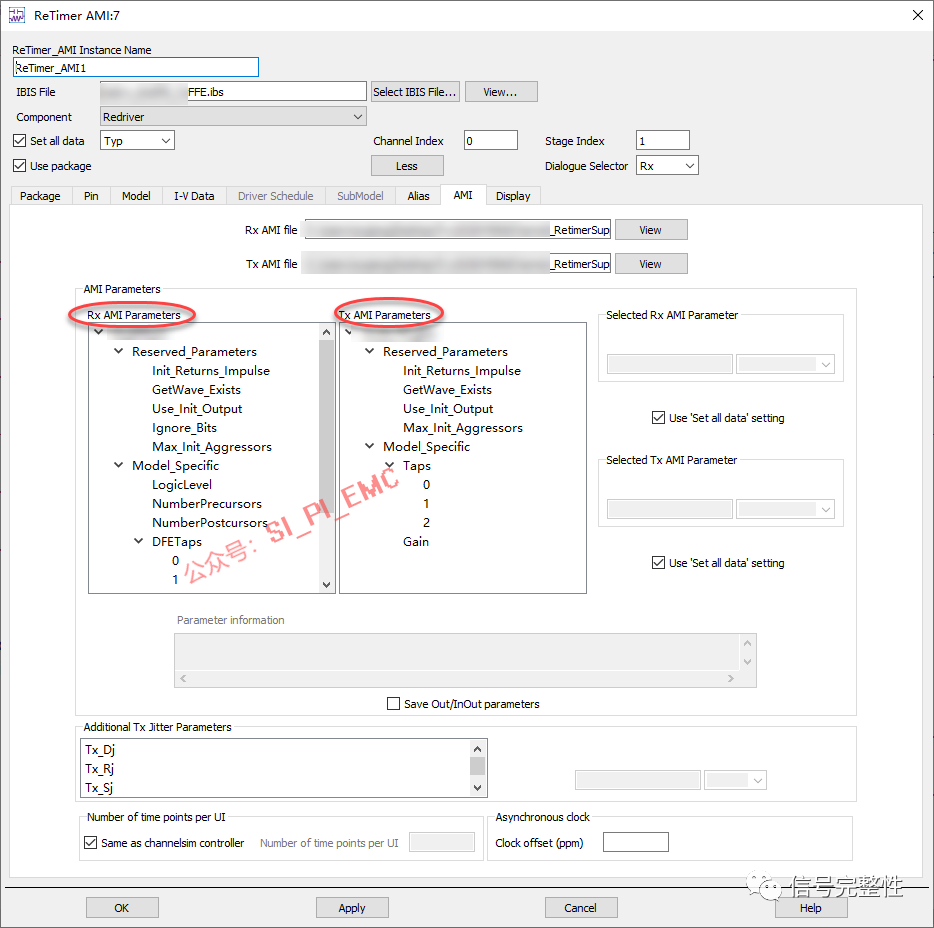

双击ReTimer_AMI导入Retimer的IBIS-AMI模型。在设置Retimer模型时,需要配置好AMI模型,如下图所示:

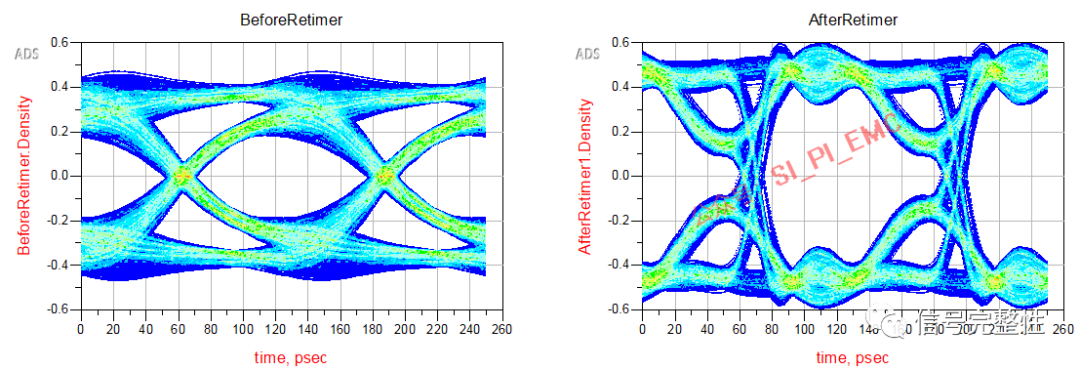

仿真后,分别观察Retimer前后的眼图,眼图如下图所示:

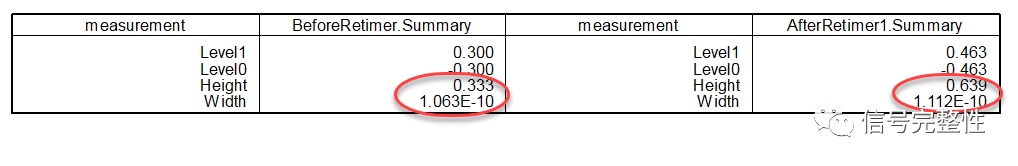

分别读取眼图的眼高和眼宽,如下图所示:

从结果上可以看到,在Retimer前后的眼图差异非常大,眼高和眼宽都改善了很多。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

信号完整性与电源完整性的仿真2021-09-29 1646

-

Hyperlynx信号完整性仿真2021-04-07 2151

-

如何在考虑信号完整性的情况下进行高速的PCB设计2019-01-21 1635

-

高速 PCB 信号完整性仿真分析.pdf2018-05-07 2668

-

Altium Designer中进行信号完整性分析2015-12-28 17280

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 7033

-

信号完整性的仿真分析2011-11-30 695

-

信号完整性仿真应用2009-11-25 4244

-

信号完整性原理分析2009-11-04 1287

-

高速电路信号完整性分析与设计—信号完整性仿真2009-09-12 44449

全部0条评论

快来发表一下你的评论吧 !