介绍使用FIFO和DMA搭配的方式及运作原理

电子说

描述

在单片机或者是嵌入式编程中,通常软件和硬件是紧密相连的。编程者需要同时拥有硬件思维和软件技巧,才能使程序更高效、更稳定的运行在嵌入式系统中。在机器人系统中,各个模块间的通信就像人的神经,往往需要很高带宽与实时性,借助DMA和FIFO能够极大程度的发挥出外设的性能。本文将介绍使用FIFO和DMA搭配的方式,并且详细介绍其运作的原理。

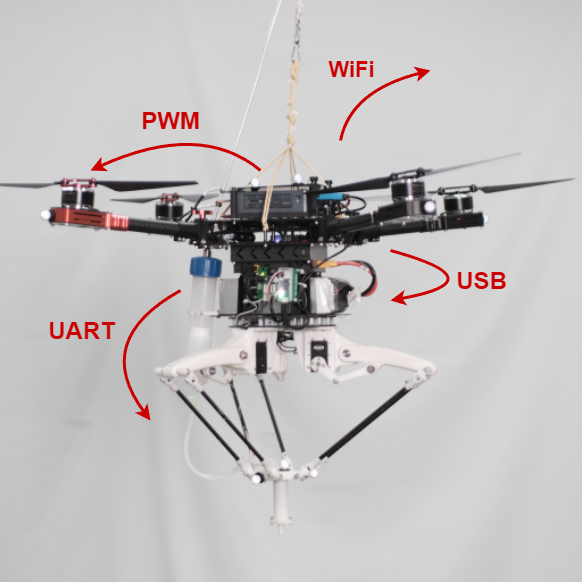

作业无人机的通链路 ▌本文所述FIFO都是软件FIFO,不包括部分DMA控制器中自带的FIFO功能。

FIFO

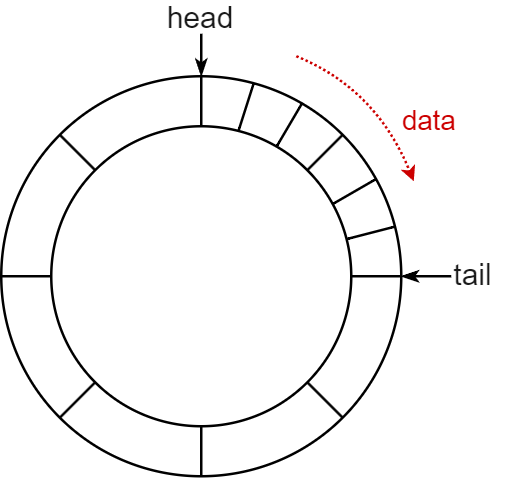

FIFO是“先进先出”的缩写,是一种常用的数据结构和算法。它是一种队列(Queue)的实现方式,即先进入队列的数据项先被处理,后进入队列的数据项则后被处理。 环形队列是一种特殊的FIFO数据结构,其中队列被表示为一个环形结构。在环形队列中,队列的头部和尾部被视为相邻的元素,因此当尾部元素到达队列的末尾时,它会回到队列的开头。这样,队列看起来像一个环,因此称为环形队列。环形队列可以使用数组实现,但需要特殊处理插入和删除元素的操作,以确保它们在队列头部和尾部之间循环。

FIFO可以用于缓存数据,当输入数据的速度超过处理的速度时,FIFO可以作为一个缓冲区,暂时存储多余的数据,以平滑数据的输入和输出速度。另外,当需要频繁地访问内存或外设时,FIFO可以作为一个临时缓存区,将数据暂时存储在队列中,以减少对内存或外设的频繁访问,提高系统的效率。

DMA

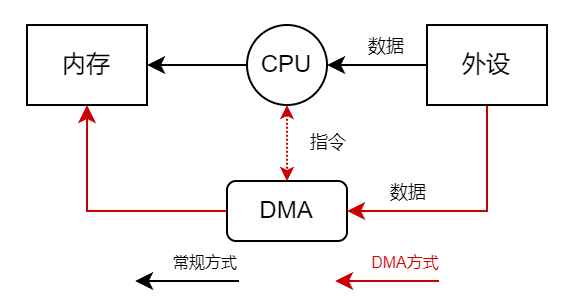

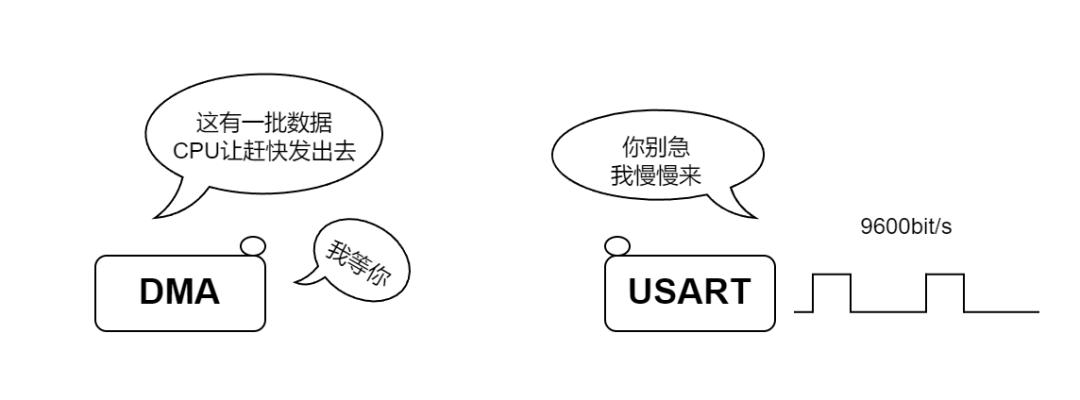

DMA(Direct Memory Access,直接内存访问)。常规情况下,我们对外设的操作都是由CPU直接处理,但面向与一些低速的传输手段,如:IIC、UART、SPI,为了保证时序,使用CPU操作寄存器的方法去处理无疑浪费了大量的运算时间。而DMA的出现,可以使数据可以在主存储器和外设之间自动传输,而不需要CPU的干预。这可以使CPU在数据传输期间执行其他任务,提高整个系统的效率。

如上图所示两条通道中,CPU只需要和DMA进行一些指令通信,DMA就能替CPU完成对外设到内存的数据搬运。 ▌DMA也可完成内存到内存等多种方式的通信,不同的厂商的芯片通常会有一些专用的DMA控制器例如:DMA2D、MDMA等,但本质都是对内存的直接访问。

传输过程

DMA的传输大致分为如下三个步骤:

预处理:由CPU完成一些必要的准备工作。首先,CPU执行几条I/O指令,用以测试I/O设备状态,向DMA控制器的有关寄存器置初值,设置传送方向、启动该设备等。然后,CPU继续执行原来的程序,直到I/O设备准备好发送的数据(输入情况)或接受的数据(输出情况)时,I/O设备向DMA控制器发送DMA请求,再由DMA控制器向CPU发送总线请求(统称为DMA请求),用以传输数据。

数据传送:DMA的数据传输可以以单字节(或字)为基本单位,对于以数据块为单位的传送,DMA占用总线后的数据输入和输出操作都是通过循环来实现。需要特别之处的是,这一循环也是由DMA控制器(而不是通过CPU执行程序)实现的,即数据传送阶段是完全由DMA(硬件)来控制的。

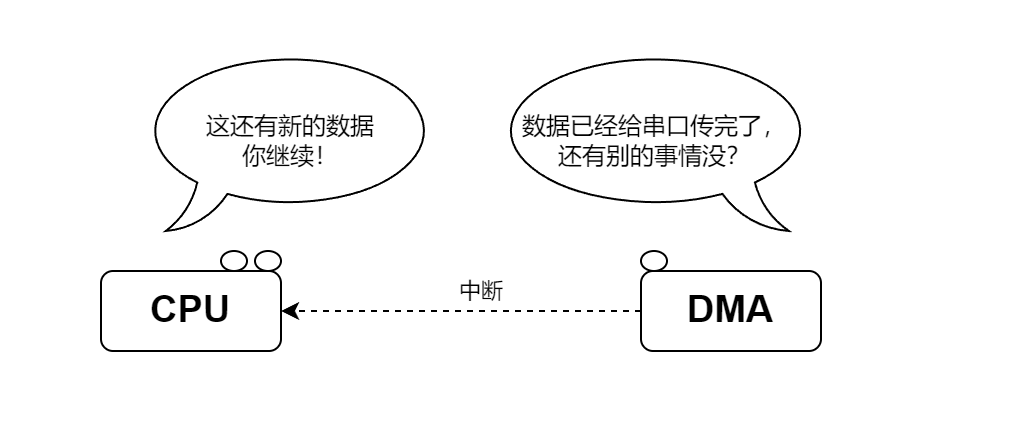

后处理:DMA控制器向CPU发送中断请求,CPU执行中断服务程序做DMA结束处理,包括检验送入主存的数据是否正确,测试传送过程中是否出错(错误则转入诊断程序)和决定是否继续使用DMA传送其他数据块等。

由此可以看出,整个过程中,CPU只需要介入预处理和后处理的少量指令环节。在一些特殊情况下,例如ADC数据的DMA传输,只需要在初始化时进行配置,DMA设置为循环模式,后续的过程完全不需要CPU介入,极大的节约了CPU时间。

快递员与快递站

在实际生活中,我们随处可见DMA和FIFO的身影,为了能更加方便的理解DMA和FIFO的作用,我们可以用快递员和快递站来做比喻:

FIFO(先进先出队列)是一个快递站,快递员将快递按照到达时间顺序放在一个队列中,当需要发货时,按照队列顺序一个一个地取出快递进行发货,保证了快递的顺序性。快递站如果太小,如果收发快递数量太多,快递站就会爆满堵塞,快递丢失。如果快递站过大,则占用过多土地,得不偿失。

DMA(直接内存访问)是一名任劳任怨的快递员,他可以直接到发货地点取出快递并将其送到目的地,中间的驿站可以视为内存或者缓存。在这个过程中,快递员可以不停歇地工作,而不需要等待驿站的确认,同时也不需要用户的干预,可以大大提高快递的效率和速度。

DATA(数据),数据则是快递,快递的尺寸数量要考虑快递员的能力,不能过大过多。

无论是现实还是嵌入式系统,人和内核不可能时时刻刻都带等待快递和数据。数据的处理和接收并不一定是同时进行的,内核对数据的等待造成了系统的阻塞,但数据的不及时处理会造成了数据的丢包,以上两个原因促使了DMA和FIFO的相互补充使用。

更高的效率

以上用具体的例子比喻了DMA和FIFO的应用场景,实际应用也当如此。以下会介绍详细的使用方法和具体的应用场景,同时开发者也要认清,并不是所有的场景都适合使用DMA,使用时要考虑实际的稳定性和必要性。

应用场景

下面将列举几种场景,分别是DMA与软件FIFO配合、DMA以及不适合DMA场景的应用。

▌DMA-FIFO

DMA-FIFO最适合数据量大、不定长的数据包的场景,典型应用为串口通信,无论是串口的接收还是发送,使用DMA-FIFO都能极大的增加芯片的运行效率,且在绝大多数情况下都能提高串口外设的性能。PWM、GPIO操作算是DMA应用中一个比较冷门的应用,使用DMA操作此类外设,能零堵塞、高时序精度去实现W2812全彩灯、DSHOT协议等功能。

▌DMA

单用DMA适合数据量大、定长、定周期的场景,典型应用为SPI-LCD数据传输、摄像头DCMI传输、ADC传输、内存-内存传输,此类传输特点大多数为大块数据周期性传输,传输速度要求高,数据量比较大。例如在摄像头数据的传输过程中,摄像头数据固定以30FPS进行传输,配合DMA的双缓存功能能很好的实现数据的传输与处理同时进行,此外像DMA2D这种专用的图像显示DMA也是相同的道理。

▌不适用场景

虽然DMA在许多情况下可以提高数据传输的效率和速度,但并不是所有情况都适合使用DMA。下面是一些不适合使用DMA的场合:

数据一致性场合:DMA传输过程中不需要CPU干预,所以实际上CPU并不知道内存中数据发生了变动,尤其是在启用了cache的情况下,数据一致性问题就变得尤其严重。例如一些加密、解密、固件写入等场合,对数据一致性要求较高、需要实时校验,不建议使用DMA传输。

时序一致性场合:DMA也不适合对于数据包时序要求严格的场合,例如在SPI写入LCD数据指令前,需要先写入控制指令并操作DC引脚,在这种情况下,如果不能将传输与中断的逻辑进行妥善处理,则会造成严重的数据冲突,所以SPI-LCD屏一般只有在数据阶段采用DMA传输。还有在初始化阶段,程序对于效率速度的要求不高,但时序与稳定性要求较高的时候,不建议使用DMA传输。

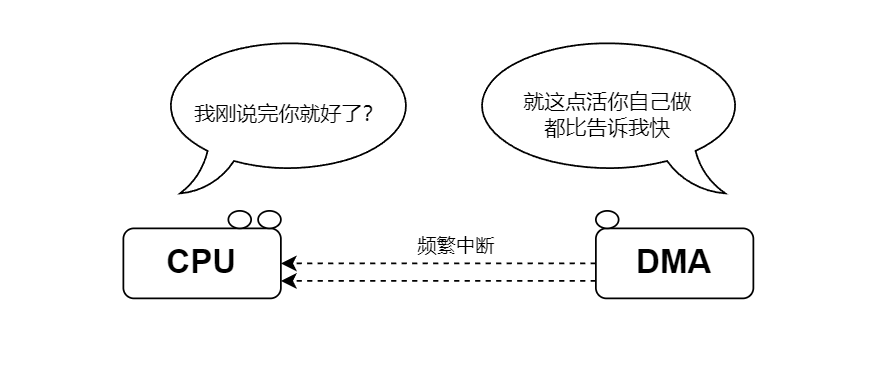

数据传输量较小:由于DMA传输存在预处理和后处理阶段,例如仅传输几个字节的数据,那么使用DMA可能不会带来很大的性能提升。相反CPU可能需要反复进入中断进行处理,增加了额外的复杂性和成本。

技巧与细节

在DMA的使用过程中,也存在很多的使用技巧,例如利用好DMA的全传输中断、半传输中断与双缓存,能使DMA的传输性能得到进一步的提高。熟悉DMA的基本属性,需要仔细的去阅读相应芯片厂商的技术手册,避免其在传输中发生冲突,数据发生覆盖等问题的发生。

总结

FIFO和DMA的应用只是嵌入式系统中优化的一小部分,对于开发者来说,在开发过程中,“能用”并不是调好一个外设的标准。在项目调试工程中,往往会遇到因为打印了几行日志、变更了协议格式、更改了通信速率,就发现程序就不能正常运行了,不严谨、不规范的开发方式容易使项目陷入Bug越改越多的开发陷阱中。

审核编辑:刘清

-

DMA产生FIFO error interrupt错误的原因?2024-05-15 1078

-

关于FIFO DMA2013-08-28 2297

-

请问F28M35x ADC结果使用DMA方式传输时DMA模块有缓冲区(FIFO)可用吗?2018-08-22 2145

-

STM32F765+SN8000+DMA FIFO错误2019-01-07 2079

-

DMA的基本介绍2021-07-30 1372

-

dma+空闲中断加fifo实现串口的高效收发2021-08-13 2344

-

串口DMA发送/接收 FIFO突发模式是什么?2022-02-28 1445

-

LabVIEW FPGA模块实现FIFO深度设定2011-09-26 8158

-

介绍模块化散集 DMA IP及如何与 Nios II 处理器搭配使用2018-06-22 4213

-

以太网基础介绍:MAC地址,FIFO, DMA2018-07-03 8726

-

STM32F429芯片带FIFO的DMA传输实现过程2020-09-04 8867

-

MZ7035系列开发板XILINX FPGA DMA和VDMA的应用教程2020-11-09 2321

-

DMA通信编程与STM32串口中断方式2021-11-26 985

-

STM32采用串口DMA方式向上位机连续发送数据2021-11-30 815

-

AN3109_用STM32F10x微控制器的DMA和DMA超时仿真通信外设FIFO2022-11-21 604

全部0条评论

快来发表一下你的评论吧 !