保护片上系统:小芯片时代的硬件保护

描述

似乎几乎每周,半导体行业包罗万象的晴雨表摩尔定律都会被宣布死亡、垂死或实际上比以往任何时候都更健康。随着争论继续猜测其健康状况,可以肯定的是,随着FinFET技术取代了传统2D平面栅极市场的更大份额,单一的单片芯片设计将变得不可持续。

清算之日

越来越多的公司正在通过制造标准化的“小芯片”并从中组装一系列更复杂的设计来恢复“系统级封装(SiP)”或“异构集成(HI)”方法。这种将类似乐高的硅片组合成单个封装设备的模块化方法并不是什么新鲜事,自 1980 年代以来一直存在于 MCM 中。就连戈登·摩尔(Gordon Moore)的原始文章也承认,他的理论终将迎来清算的一天,并且需要一种更横向的方法。

为什么现在使用小芯片?

Chiplet 提供了一种灵活、可扩展且经济高效的方法,可以满足现代系统不断变化的复杂性需求。

与SoC更均匀的单芯片集成相比,这种异构方法可以大大降低制造和设计成本,因为并非所有小芯片都必须在最新的节点上制造。例如,核心逻辑小芯片可以利用顶级晶圆厂的最新和最好的产品,而I/O小芯片可以在更小、更实惠的代工厂生产。因此,SiP 可以提供比单芯片 SoC 更大的优势,例如更高的晶圆良率和更快的上市时间,尽管将它们集成到具有专用小芯片基板(中介层)的单个封装中很复杂。

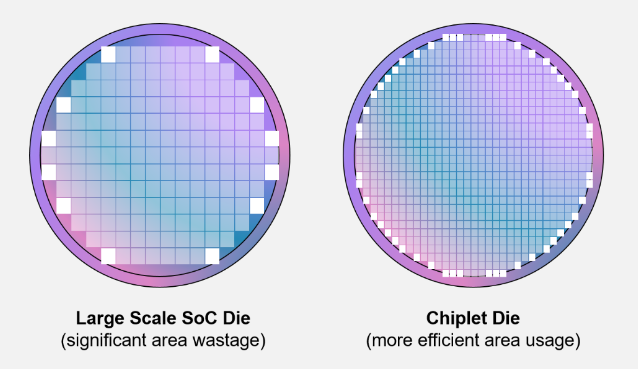

随着每个前进工艺节点的特征尺寸减小,缺陷密度也相应增加,这给制造商带来了重大问题。结合复杂SoC设计的绝对尺寸较大,对于大型单片设计,每个晶圆的可用优质芯片明显减少。如果随着我们越来越向亚纳米技术迈进,缺陷密度继续增长,除了减小模具本身的尺寸之外,还有什么选择?

然而,可以通过生产更小的设计(小芯片)组装成更大的设计(SiP)来提高良率。另一个好处是更好的晶圆利用率,这是通过每个晶圆封装比大型SoC芯片更多的小芯片来实现的,这浪费了大量空间。

今天的小芯片实施

系统的灵活性意味着只有与功能更新相对应的小芯片需要重新设计,从而最大限度地减少设计过渡到新节点的总体工作量。成本节约也可以沿着供应链传递,无需针对不同市场单独设计的产品系列。这通过替换适当的小芯片来在价格和性能上与目标细分市场相匹配,从而简化了库存单位 (SKU) 成本。

鉴于基于小芯片的设计的优势,许多行业重量级人物已经开始他们的小芯片计划也就不足为奇了:英特尔的 Agilex FPGA 和 SoC、AMD 及其 EPYC 和锐龙处理器系列、NVIDIA 使用他们的小芯片互连技术 NVLink-C2C,甚至台积电在 2020 年推出了他们的 3DFabric 技术来帮助客户设计自己的基于小芯片的 SiP。为了不错过这一行动,美国政府还投入了资源,通过DARPA的通用异构集成和知识产权重用策略(CHIPS)探索这种有前途的芯片设计风格。最后,证明基于小芯片的设计不仅仅是一种昙花一现的时尚,已经有人推动了小芯片相互通信的方式正式化,通用小芯片互连快递(UCIe)开放标准正在被英特尔、AMD、Arm、台积电、三星、高通、谷歌和微软等公司推广。

安全隐患

由于流行趋势倾向于基于小芯片的方法而不是单片单芯片SoC,我们可能会将超过十个小芯片集成到单个设计中,每个小芯片可能来自不同的晶圆。从安全角度来看,当从单个SoC芯片移动到多个SiP芯片时,攻击面的数量将迅速增加。采购的每个小芯片都涉及许多可能的铸造来源和设计公司。不仅需要保护多组 I/O,而且每个供应商不一定遵守同一组安全协议。

目前,这可能不是一个问题,因为小芯片只占据很小的市场份额。然而,随着小芯片开始得到更广泛的采用,小芯片供应商的数量将会扩大,管理不同的安全约定将很快成为一个重大风险。

小芯片供应链风险

连接国际供应商的地缘政治紧张局势只会增加复杂性,尤其是在美国和中国之间的紧张局势继续加剧的情况下,双方都试图将本已脆弱的半导体供应链分叉。因此,通过供应链从一个位置到另一个位置安全地跟踪组件对于确保SiP至关重要。因此,供应链中的任何潜在薄弱环节都是攻击者插入受感染小芯片的成熟目标,可能带有恶意负载、特洛伊木马或间谍软件。

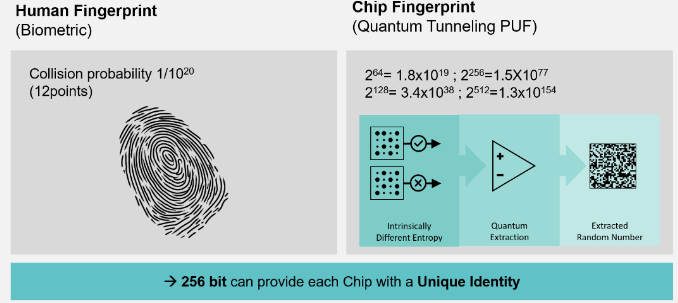

PUF 芯片指纹识别

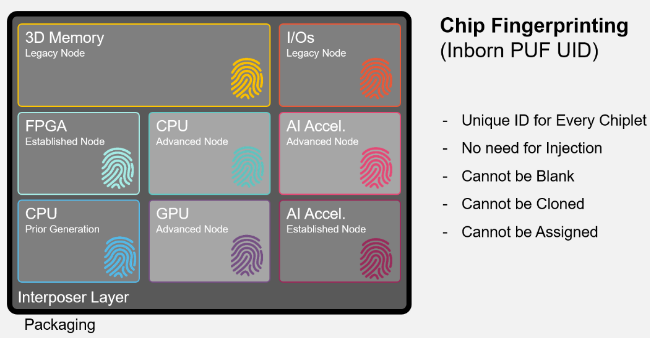

鉴于在向基于小芯片的架构过渡期间面临的这些新的安全挑战,令人欣慰的是,目前与 SoC 一起部署的相同 PUF 保护也可以为 SiP 创建基础信任根。当集成到设计中时,它们可以为每个小芯片提供源自PUF芯片指纹的唯一标识(UID)。

嵌入到SiP中每个小芯片中的物理不可克隆功能(PUF)将汇集基于小芯片设计的碎片化特性,并支持四个中央安全功能。

身份验证:通过识别每个小芯片,PUF将确保每个小芯片都真正来自合法供应商。

配置:在验证每个小芯片是真实的后,中央安全服务器可能会将其打开,以防止假冒或被篡改的小芯片通过未经授权的渠道进入供应链。配置还可用于打开和关闭系统中的功能,针对特定市场或目标客户定制每个设计,同时为这些不同情况使用相同的基本SiP。

跟踪:当每个小芯片都有一个唯一的标识符时,在整个设计和组装过程中跟踪它们变得更加容易。对于安全漏洞可能造成灾难性后果的客户(例如汽车或航空市场)而言,通过SiP供应链留下清晰的审计跟踪尤为重要。

分析:当我们能够识别每个小芯片时,我们可以收到有关每个小芯片状态的反馈。这些数据可以安全地发回,用于实时分析、故障分析,甚至是无法承受停机时间的关键任务应用程序的连续状态监控。

当然,每个小芯片都可以通过外部密钥注入过程单独配置自己的ID,但考虑到将进入复杂设计的小芯片数量,通过嵌入能够进行内部密钥配置的PUF来自动执行此操作更有意义,而无需安全,干净的房间环境和生成唯一ID所需的相关安全硬件。

通过在HI设计中的每个小芯片上添加PUF,可以轻松实现对上述四个功能的支持。或者,如果其中一个小芯片专门用于安全,则可以使用基于PUF的小芯片硬件安全模块(CHSM)。在这种情况下,SiP将不再需要依赖外部安全服务器来提供服务,例如上述身份验证过程。

由于 CHSM 执行与信任根在 SoC 中执行的职责类似,因此 SiP 安全的总体基础可能来自 CHSM 本身。有了这样的基础,也可以在SiP中实现类似“安全启动”的过程。从理论上讲,这将从CHSM的身份验证开始,然后授权链中的下一个小芯片启用,然后启动链中下一个小芯片的授权过程,依此类推,直到整个SiP被启动。根据 CHSM 的配置方式,它还可以充当安全控制器来监视其他小芯片是否存在安全属性违规、硬件特洛伊木马和篡改。添加额外的传感器可以进一步检测物理篡改,例如通过激光、X 射线、电压/时钟毛刺等。捕获此类故障注入 (FI) 类型的攻击非常重要,因为它们通常会导致侧信道分析/攻击。

结论

无论围绕摩尔定律终点的争论如何,都明确需要横向创新来应对较小工艺节点的物理极限。小芯片架构可能会在这方面发挥至关重要的作用。然而,随着对设计制造过程的如此彻底的重新构想,当我们从SoC转向SiP时,将有一连串不可预测的安全问题需要考虑。

最有可能的情况是在每个 3D 封装中部署一个经过预认证和认证的基于 PUF 的安全元件 (SE) 小芯片。这将允许硬件信任根支持正在使用、传输中和静态数据的安全性。随着新一代芯片设计的推向市场,随着CPU迁移到最先进的工艺,可以继续部署相同经过验证和合格的基于PUF的SE小芯片,从而简化工艺。

想象同一个3D包中的每个小芯片部署基于PUF的保护的未来并不是一件容易的事。面对供应链安全风险以及安全组装、验证和更新 SiP 的需求,标准化 SiP 安全性似乎是不可避免的。

审核编辑:郭婷

-

红米NOTE电池保护板码片方案2015-09-24 3944

-

“5分钟快充”时代有效的芯片保护电路2017-07-21 2939

-

使用片上系统芯片怎么实现传感器模块的软硬件设计?2019-10-10 3142

-

基于片上系统芯片的传感器模块设计2010-07-15 424

-

ADSL收发器片上系统芯片的设计与实现2010-07-22 610

-

电池过流保护片基本知识介绍2009-11-27 4033

-

基于片上系统芯片的传感器模块软硬件设计2010-04-16 1161

-

一种特别适用于片上LDO系统的过流保护电路2017-01-07 1455

-

基于软硬件协同的数据动态保护机制2017-12-05 1046

-

电池过流保护片的工作原理2020-07-31 7106

-

微机保护硬件的构成2023-10-11 6200

-

控制多片PLL芯片时,串行控制线是否可以复用?2023-10-30 1074

-

片上系统代表芯片吗2024-03-28 1845

-

过流保护片的型号选择要考虑哪些参数2024-09-20 1461

-

超级AI芯片时代,电子元器件的进化方向2025-12-11 1120

全部0条评论

快来发表一下你的评论吧 !