Ti60 PLL的clkout4使用限制

描述

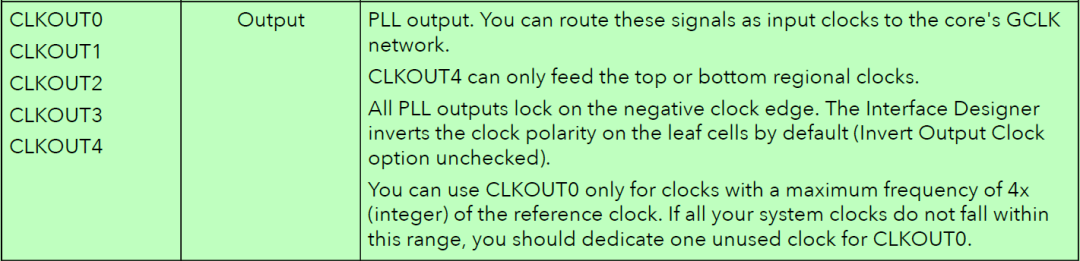

关于clkout4的说明其实不多,在PLL的说明中提到CLKOUT4只用于top和bottom的区域时钟,但是不能驱动Core逻辑。

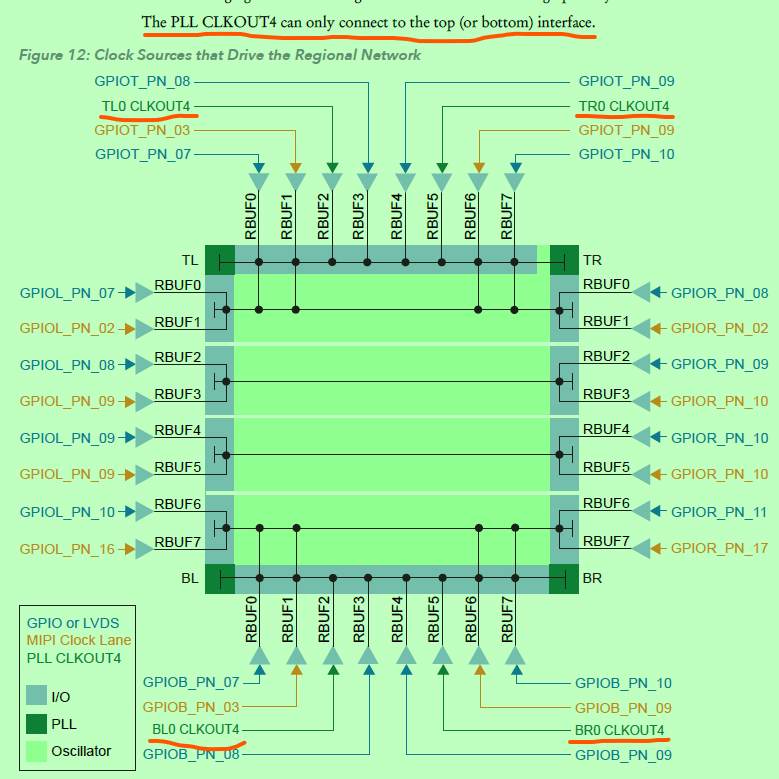

在区域时钟部分又提到CLKOUT4只用于连接top或者bottom的interface。我们对interface的理解就是interface designer。

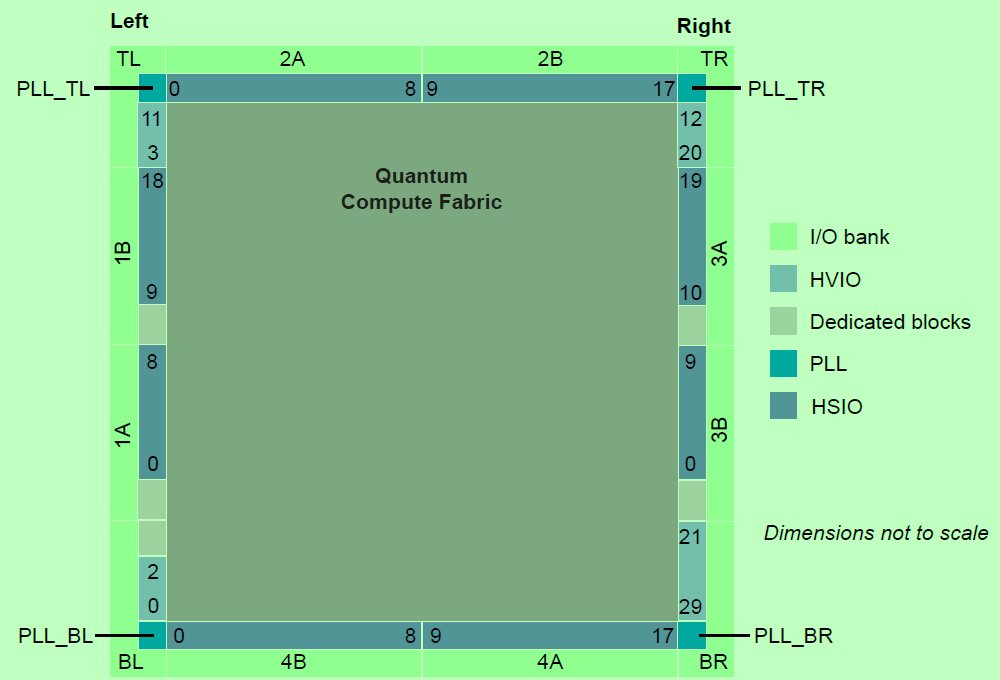

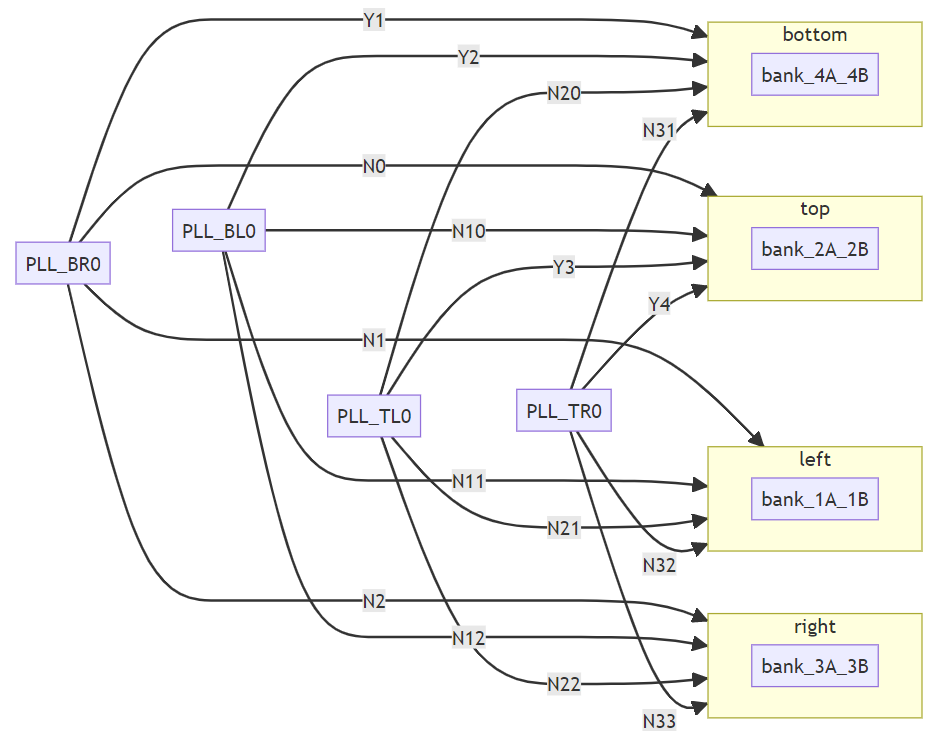

那这个top和bottom怎么理解呢?这里我们以Ti60F225为例。下图是我们截取的Ti60F225的管脚位置平面图。top我们认为就是bank 2A,2B,bottom我们认为是Bank 4B,4A. left就是bank 1A,1B,right就是Bank 3A,3B.

一、驱动IO测试

测试1:top和bottom驱动所在侧的IO

在2A,2B bank各找5个GPIO并把它们设置成clkout类型,它们分别由TL和TR PLL驱动。

在4B和4A bank中也各找了5个GPIO并设置成clkout类型,时钟由BR PLL的clkout4提供。

经过编译可以通过。

结论:TL和TR clkout4可以驱动BANK 2A和2B的IO.

BL和BR clkout4可以驱动BANK 4A 4B的IO

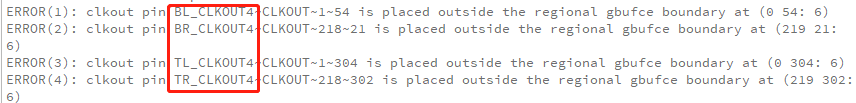

测试2 :Top PLL clkout4驱动左侧GPIO

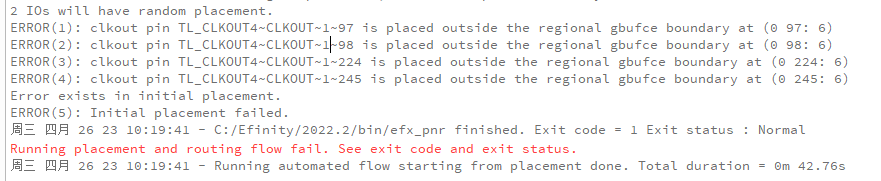

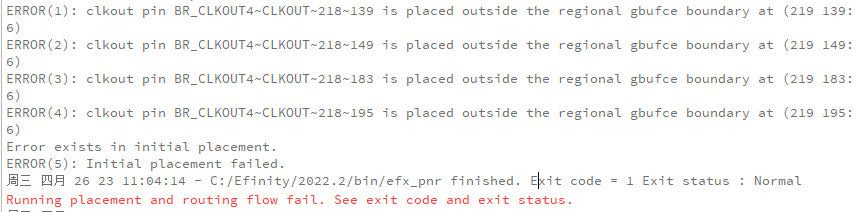

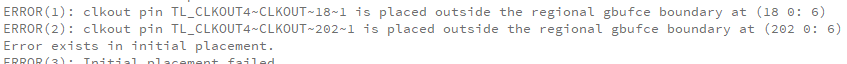

在测试1的基础上,我们在bank 1A和1B上各找了两个GPIO,设置成clkout类型,时钟由TL PLL的clkout4来驱动或者BL PLL的clkout4来驱动都会报以下错误。

测试3 :bottom PLL clkout4驱动右侧GPIO

在测试1的基础上,我们在bank 3A和3B上各添加了2个GPIO,由BR clkout4和TR clkout4来驱动 。

结论:由测试2和测试3可以得出clkout4不能驱动左右两侧的IO。

另外我们还测试top PLL的clkout4驱动bottom 的IO,结论依然是不能驱动 ,反之亦然。于是我们有了下面的图。图中Y表示Yes,N表示N,后面的数字是编号,总之YX表示可以驱动,NX表示不可以驱动。

二、级联测试

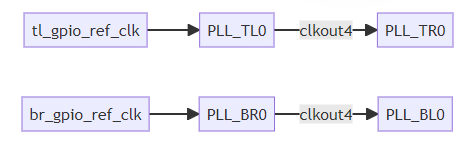

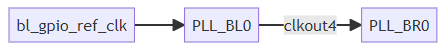

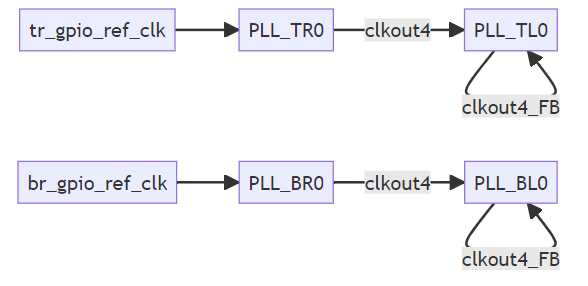

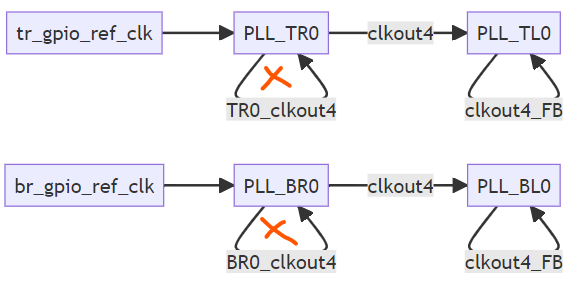

测试4:top或bottom的两个PLL级联,但是clkout4不作为反馈

经过测试可以编译通过。

结论:clkout4可以在top或者bottom内部实现两个PLL级联

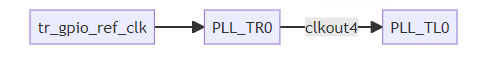

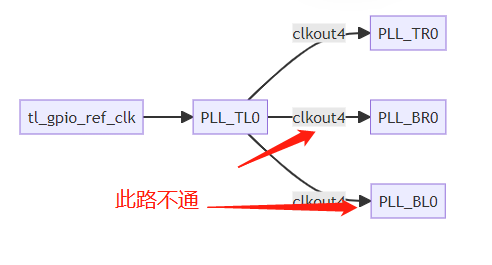

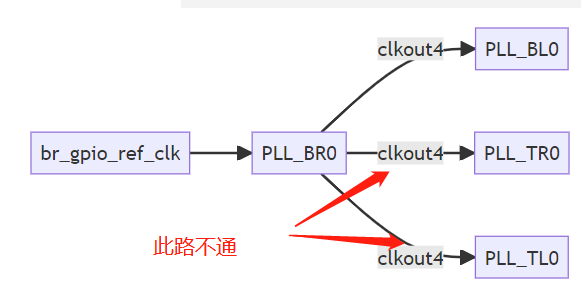

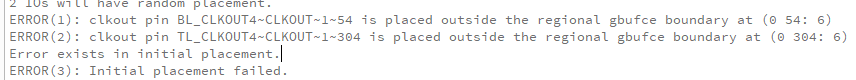

测试5:top与bottom的两个PLL级联

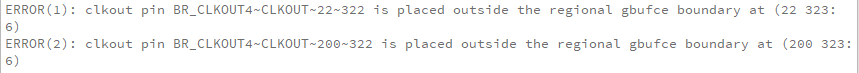

如果把TL0的clkout4作为BR0,BL0的参考时会报出两个路径出错。

如果把BR0的clkout4作为TR0,TL0的参考时会报出两个路径出错。

结论:top与bottom之间的PLL无法实现级联 。

三、反馈测试

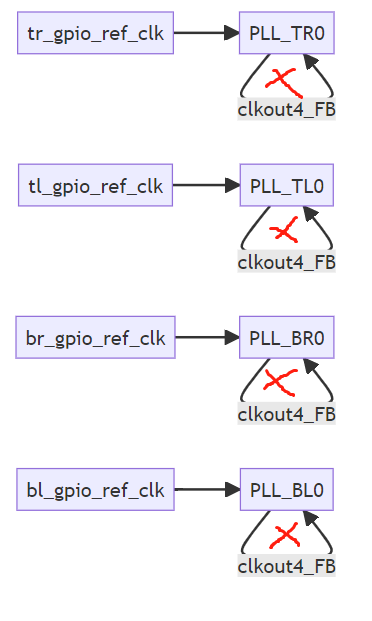

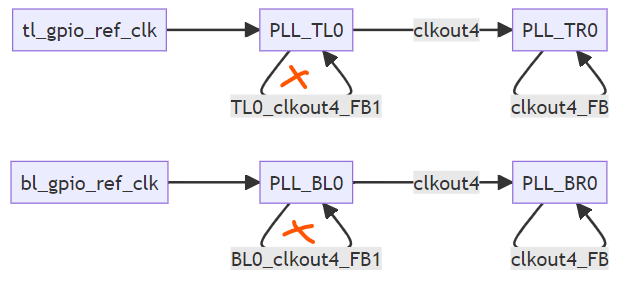

测试6:clkout4用作反馈

当PLL的参考时钟为external时,用clkout4作为反馈时钟,发现4个PLL都不能用作反馈。

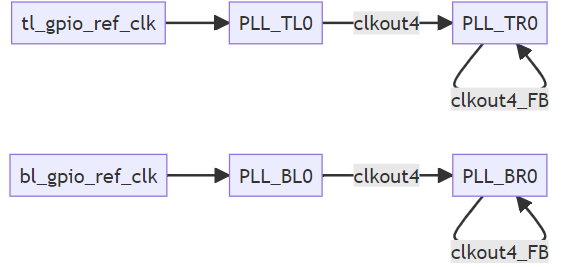

测试7:级联反馈

如果级联后,第一级的clkout4反馈也打开编译也会出错。经过测试有以下结论。

结论:如果用clkout4用于级联,第二级的clkout4可以用作反馈。

综上:

(1)top的PLL可以驱动top的IO,但不能驱动left,right和bottom的IO;同样bottom的PLL可以驱动bottom的IO;但是不能驱动 top,left和right的IO.

(2)PLL可以通过clkout4实现级联,便是限制于(BL0,BR0)和(TL0,TR0)两组内部。

(3)PLL的clkout4也可以用作反馈,但是限制于级联的两个PLL的第二级。

审核编辑:汤梓红

-

lmk04208 clkout0输出不正常是什么原因导致的?2024-11-12 448

-

如何使PLL_BASE组件可配置?2019-06-20 2484

-

PLL和FIFO的受约束问题2019-07-15 1705

-

请问我能从PLL,DCM或级联PLL DCM获得多大的输出频率限制?2019-08-02 1973

-

怎么查看ClkOut的延迟?2019-08-19 1557

-

为什么dm8127的CLKOUT0未输出时钟信号?2019-08-23 1030

-

请问PLL_ADV中CLKOUT2的输出频率是多少?2019-10-31 1891

-

摄像机链接失败切换限制约束2020-04-10 644

-

PLL属性更改后时序失败怎么办?2020-06-01 1550

-

Virtex-6有专用的clkout(PLL输出)引脚吗?2020-06-12 2272

-

xc7k70t PLL最大输出是多少?2020-07-27 2883

-

【正点原子DFPGL22G开发板体验】内置IP核使用体验-PLL之呼吸灯2023-02-09 935

-

LPC43xx PLL相位是否同步?2023-05-06 625

-

TI IWR6843单片60- 64-GHzmmWave传感器解决方案2020-03-09 8756

全部0条评论

快来发表一下你的评论吧 !