深度分析AMBA总线工作原理3

电子说

描述

2.4 AHB总线

2.4.1 AHB总线简介

AHB是一种高性能、高时钟频率的AMBA总线协议。主要用于连接RAM、DMA、Bridge等高速设备。主要支持如下特性:burst传输、Split事务处理、单周期master移交、流水线操作、支持多个总线主设备。

AHB总线的强大之处在于它可以将微控制器CPU、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等连接起来,构成一个独立的完成SOC系统。不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完成的SOC芯片的骨架

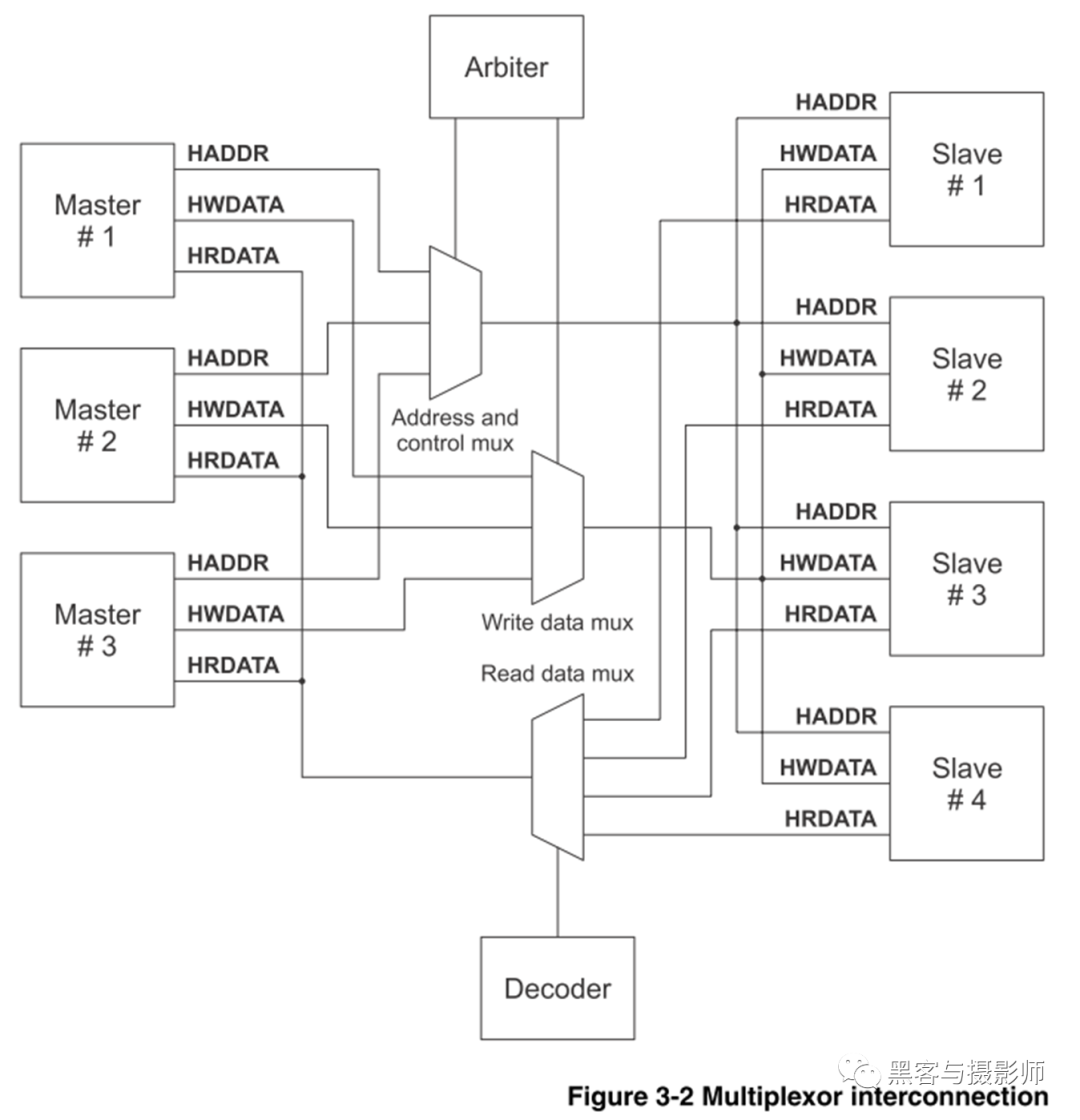

2.4.2 AHB的组成

完整的AHB总线由四个部分构成:

- AHB主设备Master:总线主设备能够通过提供地址和信息发起读写操作,任何时候,只允许一个总线主设备处于有效状态,并使用总线。

- AHB从设备Slave:从设备在给定的地址空间范围内响应读写操作,总线从设备将成功、失败或者等待数据传输的信号返回给有效的主设备。

- AHB仲裁器Arbiter:总线仲裁器确保每次只有一个总线主机被允许发起数据传输。即使仲裁协议已经固定,任何一种仲裁算法,比如最高优先级或者公平访问都能根据应用要求而得到执行。AHB必须只包含一个仲裁器,尽管在单总线主设备系统中这显得并不重要。

- AHB译码器Decoder:AHB译码器用来对每次传输进行地址译码,并且在传输中包含一个从设备选择信号。

每个AHB都需要一个仲裁器和一个解码器,并且分别有且只有一个。

总线可分为三组: - 写数据总线(HWDATA)

- 读数据总线(HRDATA)

- 地址控制总线(HADDR)

2.4.3 AHB总线操作

主设备通过驱动地址和控制信号开始一次传输。这些信号提供了地址、方向、传输的位宽,如果传输的类型是猝发,那么会指示出传输的类型。传输的类型可以是:

- 单次传输(Single)。

- 递增猝发(Incrementing burst),即在地址边界处不进行包装(地址不进行回绕)。

- 包装猝发(Warpping burst),及到达地址边界处重新包装下一次传输的地址(地址回绕)。

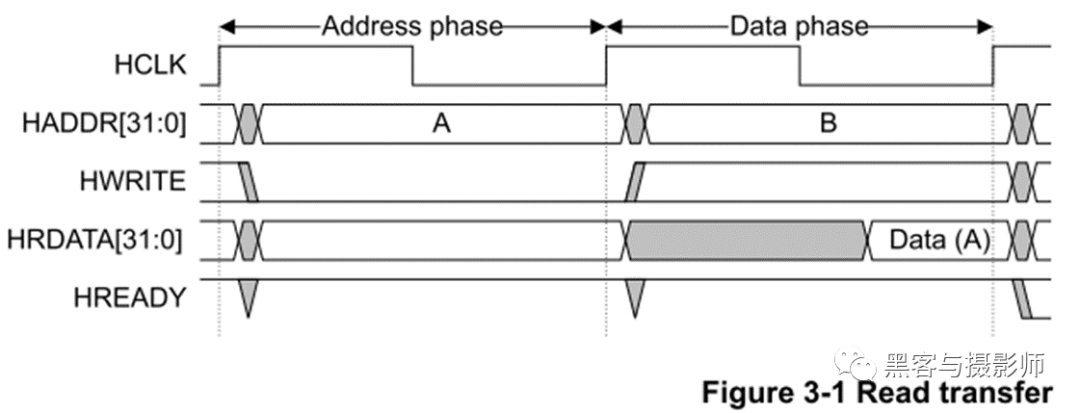

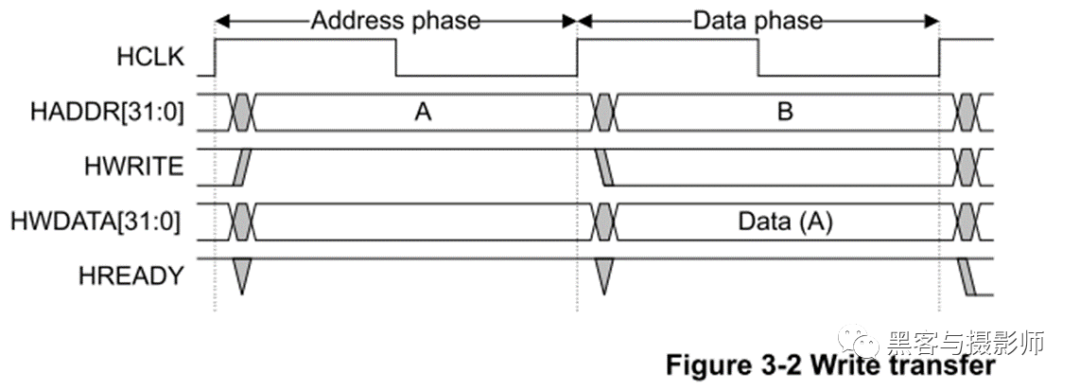

写操作数据由主设备到从设备,读数据数据由从设备到主设备。每次传输都包含两个阶段: - 地址阶段(Address phase),地址和控制周期。

- 数据阶段(Data phase),数据周期是一个或多个周期。

从设备不能请求Address phase进行延长,所以所有的从设备必须具备在Address phase周期采样地址的能力。但是从设备可以请求主设备延长Data phase,通过控制HREADY。HREADY信号为低时,从设备可以在传输中插入等待状态,使得从设备具有额外的时间提供和采样数据。最后从设备使用HRESP表明传输的成功/失败。

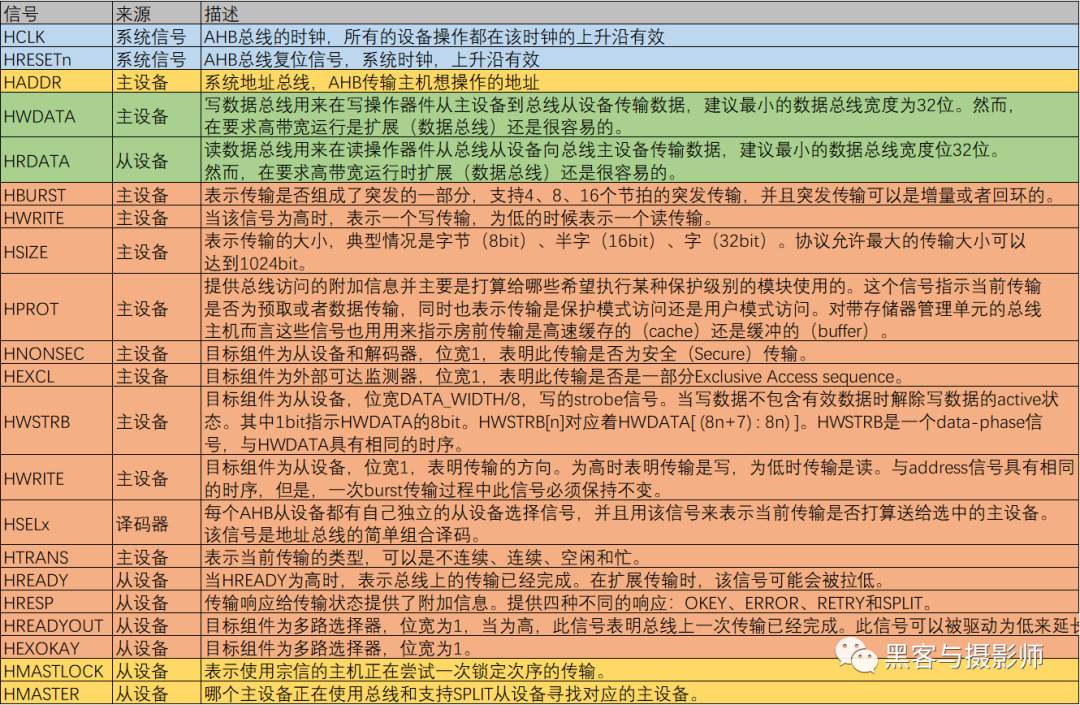

2.4.4 AHB信号

从上面的表可以看出,为了克服APB的缺点,从而支持多主机模式。提升效率操作,在总线接口数量上做了增加,并且位宽也做了提升。

2.4.5 AHB传输

1)AHB传输过程

AHB传输分为以下几个部分:

- 主模块获取总线使用权:主模块向仲裁器发送总线请求信号,仲裁器发送应答后主模块可以开始传输。

- 数据传输:主模块向从模块传输数据,分为如下两个部分:

- 发送地址和控制信号:包括地址、位宽、突发类型(增量突发和回卷突发)等控制新高,仅一个时钟周期。

- 数据传输:进行数据交换,一个或多个时钟周期。

- 从模块应答:从模块通过HRESP和HREADY 标记完成状态,对于HRESP,有以下状态:

- OKAY:标记传输完成,当HRESP为该状态且HREADY拉高时,传输完成。

- ERROR:标记传输出错

- RETRY和SPLIT:标记传输未完成,主模块仍需要占用总线。

前面已介绍一个基本的传输包括两个阶段: - 地址:持续一个系统时钟HCLK周期,除非被上一个传输延长

- 数据:可能需要数个系统时钟HCLK周期,使用HREADY信号来控制完成一次传输所需要的时钟周期。

HWRITE:控制数据的方向。当为高时,表明进行一次写传输,数据由主模块端发送,从模块端接收。当为低时,表明进行一次读传输,从模块端产生读数据,主模块端接收读数据。

2)无等待状态

上图是没有等待状态的简单传输的时序图,所以此传输包含一个地址周期和一个数据周期。3.1为读传输,3.2为写传输。在这个没有等待状态的传输中:

- 主模块端在第一个时钟HCLK上升沿将地址和控制信号到总线。

- 从模块端在接下来的一个时钟HCLK上升沿进行地址和控制信号采样。

- 在从模块端对地址和控制信号采样结束后,从模块端可以驱动HEADYOUT信号及数据作为回应。该信号及数据由主模块端在传输的第三个时钟HCLK上升沿进行采样。

这个例子说明了地址和数据阶段在不同的时钟周期是如何传输的。任意一次传输的地址阶段发生在上一次传输的数据阶段(重合,即当前传输的地址阶段和前一次传输的数据阶段重合)。address与data的重合是进行总线流水线处理的基础,此特性允许总线高性能操作,同时也为从模块端发送反馈信息提供了充足的时间。

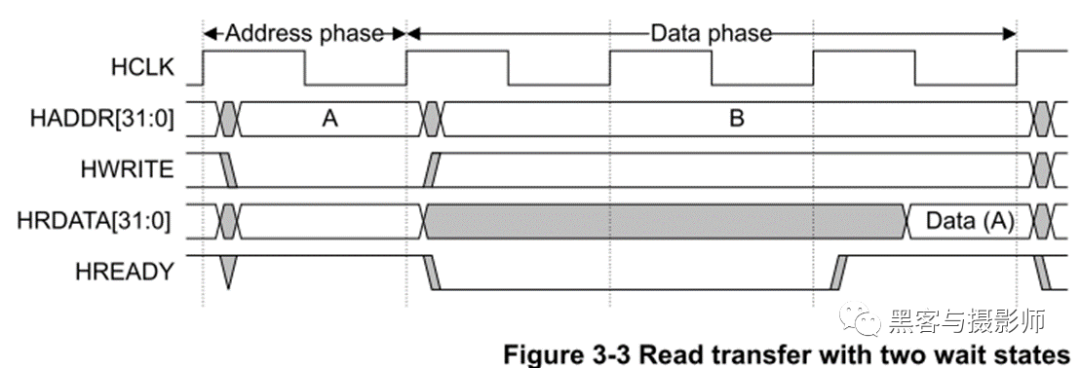

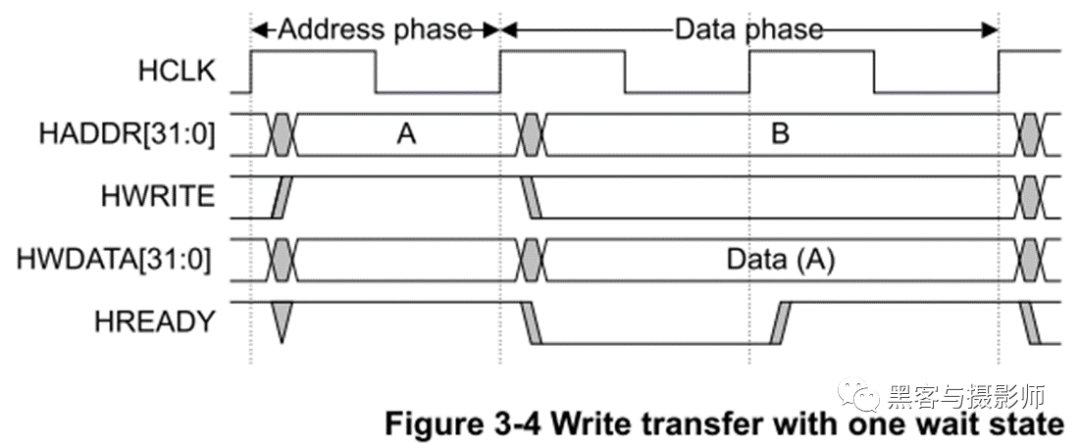

2)有等待状态传输

从模块端可以插入等待阶段到任意一个传输中从而延长完成传输的时间。每个从模块端具有一个HREADYOUT信号,该信号为从模块端在data phase阶段驱动。互联结构需要将每个从模块端的HREADYOUT信号联合起来产生一个HREADY信号,HREADY信号用来控制上述延长传输完成时间的过程。

如上图是具有等待阶段的时序图。3.3是带有两个等待周期的读传输,3.4是带有一个等待周期的写传输。有等待传输下,数据传输阶段可以扩展,即在HREADY拉高之前,数据传输阶段不结束。要求写数据在HREADY拉高前保持稳定,主模块在HRAEADY拉高后采样读数据。对于写操作,在HREADY为低的等待阶段内,主模块端需要将写数据DATA保持不变,直到写操作完成。对于读操作,从模块端只需要在HREADY为高的周期内提供有效数据即可。

当传输由具有等待阶段通过延长address阶段进行延长时,那么对接下来的传输具有副作用。3.5是包含地址不相关的3次传输,A,B和带有一个等待周期的C传输。

在上述时序图中:

- 传输A和传输C是0等待传输。

- 传输B具有一个等待周期的address phase。

- 延长传输B的数据phase对下一次传输C的address phase会相应的拉长。

2.4.6 传输类型

1)传输类型

传输类型使用端口HTRANS标记,有以下取值:

- IDLE(0b00):标志主模块占有AHB总线,但是没有数据传输发生。从模块需要使用OKAY状态回应该类型

- BUSY(0b 01):标志主模块占有AHB总线并在进行突发传输,但下一个传输不能立刻发生。从模块需要使用OKAY状态回应

- NONSEQ(0b 10):标志主模块当前发送的地址和控制信号与上一次传输无关(单次传输就是该状态)

- SEQ(0b 11):标记主模块处于突发传输的中间部分,即当前发送的地址和控制信号与上一次地址和控制信号有关

2)突发类型

突发传输分为两类:

- 增量突发:传输过程中传输地址递增。下一次传输的地址是上一次地址加上一个增量。

- 回卷突发:猝发的地址范围被限制在一个固定范围之内,传输地址递增,若是超出则回到地址范围的开始的地址。例如从0x34进行增量为4,范围为16的回卷突发,地址顺序为0x34、0x38、0x3c,0x30

突发类型使用字段HBURST标记,含义如下表所示:

注意一次突发传输不能跨越1kB的地址区间,且传输的起始地址必须与数据类型对应,例如传输字数据的二进制起始地址必须满足后两位为00。

3)突发终止

从机通过监控HTRANS发现突发传输的终止:

- 若下一个HTRANS标记为BUSY或SEQ:突发传输未终止

- 若下一个HTRANS标记为NONSEQ或IDLE:上一次突发传输已经终止

若突发传输是提前终止的,如总线控制权被剥夺,那么主机需要在可以进行传输时重建突发传输。例如一个4拍传输仅发送了一拍就终止,主机需要使用INCR类型的突发构建3拍传输以重建。

4)传输的例子

- T0~T1:由非连续序列性的传输启动的4拍读。

- T1~T2:主模块端不能进行传输,在第二个周期,所以插入了一个BUSY传输来延时第二次传输。此周期从模块端返回第一个周期主模块端发送读地址的读数据。

- T2~T3:主模块端准备好进行第二次传输,发送一个SEQ传输。主模块端此周期将会忽略读数据总线上由任何从模块端返回的读数据(因前一个周期为BUSY传输)。

- T3~T4:主模块端进行了第三次传输。发送了一个SEQ传输,此时读数据返回主模块端发起的第二次SEQ读读数据。

- T4~T5:主模块端进行最后一次传输。此时在第一个周期内HREADY信号为低,从模块不能将前一次SEQ读的数据返回,所以将延迟上一次SEQ传输的DATA Phase,也就是当前传输的ADDRESS phase。

- T5~T6:从模块端返回第T3、T4周期发送的SEQ读数据。

- T6~T7:无传输命令,返回T4、T6发送的读数据。

-

AMBA总线协议AHB、APB、AXI对比分析2023-06-05 4477

-

深度分析AMBA总线工作原理12023-05-04 2322

-

AMBA AHB总线与APB总线资料合集2022-04-07 5259

-

介绍AMBA2.0总线2021-09-06 4130

-

深度解读AMBA、AHB、APB、AXI总线介绍及对比2021-06-25 12807

-

基于AMBA总线介绍2021-05-19 2922

-

AMBA 3.0 AXI总线接口协议的研究与应用2021-04-12 1235

-

AMBA3.0 AXI总线接口协议的研究与应用2021-03-29 1187

-

ARM体系的特点与ARM的技术的简介及AMBA总线的分析2019-11-20 1466

-

AMBA AXI总线学习笔记2015-11-11 1329

-

AMBA总线IP核的设计2011-07-25 1322

全部0条评论

快来发表一下你的评论吧 !