半导体存储器和可编程逻辑器件简介

可编程逻辑

描述

大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

半导体存储器和可编程逻辑器件简介

半导体存储器是一种能存储大量二值信息的半导体器件。在电子计算机以及其他一些数字系统的工作过程中,都需要对大量的数据进行存储。因此,存储器也就成为了数字系统不可缺少的组成部分。

由于计算机处理的数据量越来越大,运算速度越来越快,这就要求存储器具有更大的存储容量和更快的存取速度。通常把存储量和存取速度作为衡量存储器性能的重要指标。因为半导体存储器的存储单元数目及其庞大而器件的引脚数目有限,所以在电路结构上就不可能像寄存器那样把每个存储单元的输入和输出直接引出。为了解决这个矛盾,在存储器中给每个存储单元编了一个地址,只有被输入地址代码指定的那些存储单元才能与公共的输入/输出引脚接通,进行数据的读出或写入。

半导体存储器的种类很多,首先从存、取功能上可以分为只读存储器(read only memory 简称ROM)和随机存储器(random access memory 简称RAM)两大类。

ROM:只读存储器(Read-Only Memory)是一种只能读取资料的存储器。在制造过程中,将资料以一特制光罩(mask)烧录于线路中,其资料内容在写入后就不能更改,所以有时又称为“光罩式只读内存”(mask ROM)。此内存的制造成本较低,常用于电脑中的开机启动如启动光盘,在系统装好的电脑上时,计算机将C盘目录下的操作系统文件读取至内存,然后通过cpu调用各种配件进行工作这时系统存放存储器为RAM。

PROM:可编程只读存储器(Programmable ROM,PROM)之内部有行列式的熔丝,是需要利用电流将其烧断,写入所需的资料,但仅能写录一次。PROM在出厂时,存储的内容全为1,用户可以根据需要将其中的某些单元写入数据0。部分的PROM在出厂时数据全为0,则用 户可以将其中的部分单元写入1, 以实现对其“编程”的目的。PROM的典型产品是“双极性熔丝结构”,如果我们想改写某些单元,则可以给这些单元通以足够大的电流,并维持一定的时间,原 先的熔丝即可熔断,这样就达到了改写某些位的效果。另外一类经典的PROM为使用“肖特基二极管”的PROM,出厂时,其中的二极管处于反向截止状态,还 是用大电流的方法将反相电压加在“肖特基二极管”,造成其永久性击穿即可。

EPROM:可抹除可编程只读存储器(Erasable Programmable Read Only Memory,EPROM)可利用高电压将资料编程写入,抹除时将线路曝光于紫外线下,则资料可被清空,并且可重复使用。通常在封装外壳上会预留一个石英透明窗以方便曝光。

OTPROM :一次编程只读存储器(One time Programmable Read Only Memory,OTPROM)之写入原理同EPROM,但是为了节省成本,编程写入之后就不再抹除,因此不设置透明窗。

EEPROM :电子式可抹除可编程只读存储器(Electrically Erasable Programmable Read Only Memory,EEPROM)之运作原理类似EPROM,但是抹除的方式是使用高电场来完成,因此不需要透明窗。

FLASH :快闪存储器(Flash memory)的每一个记忆胞都具有一个“控制闸”与“浮动闸”,利用高电场改变浮动闸的临限电压即可进行编程动作。

随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。

RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,即一旦断电所存储的数据将随之丢失。RAM在计算机和数字系统中用来暂时存储程序、数据和中间结果。

SRAM :静态随机存储器(SRAM)是在静态触发器的基础上附加门控管而构成的。因此,它是靠触发器的自保功能存储数据的。SRAM存放的信息在不停电的情况下能长时间保留,状态稳定,不需外加刷新电路,从而简化了外部电路设计。但由于SRAM的基本存储电路中所含晶体管较多,故集成度较低,且功耗较大。

DRAM :动态随机存储器(DRAM)利用电容存储电荷的原理保存信息,电路简单,集成度高。由于任何电容都存在漏电,因此,当电容存储有电荷时,过一段时间由于电容放电会导致电荷流失,使保存信息丢失。解决的办法是每隔一定时间须对DRAM进行刷新,使原处于逻辑电平“l”的电容上所泄放的电荷又得到补充,原处于电平“0”的电容仍保持“0”,这个过程叫DRAM的刷新。

上述简单介绍了各类存储器,内部结构和驱动原理不在介绍,有兴趣的读者可以自己查阅资料。

集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。它在电路中用字母“IC”表示。集成电路发明者为杰克·基尔比(基于锗(Ge)的集成电路)和罗伯特·诺伊思(基于硅(Si)的集成电路)。当今半导体工业大多数应用的是基于硅的集成电路。

集成电路是20世纪50年代后期一60年代发展起来的一种新型半导体器件。它是经过氧化、光刻、扩散、外延、蒸铝等半导体制造工艺,把构成具有一定功能的电路所需的半导体、电阻、电容等元件及它们之间的连接导线全部集成在一小块硅片上,然后焊接封装在一个管壳内的电子器件。其封装外壳有圆壳式、扁平式或双列直插式等多种形式。集成电路技术包括芯片制造技术与设计技术,主要体现在加工设备,加工工艺,封装测试,批量生产及设计创新的能力上。

ASIC即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

在设计一个复杂的数字系统后,在用量不大的情况下,设计和制造这样的专用集成电路不仅成本很高,而且设计、制造的周期很长。可编程逻辑器件(programmable logic device 简称PLD)的研制成功为解决这个问题提供了理想途径。

PLD是做为一种通用集成电路产生的,他的逻辑功能按照用户对器件编程来确定。一般的PLD的集成度很高,足以满足设计一般的数字系统的需要。这样就可以由设计人员自行编程而把一个数字系统“集成”在一片PLD上,而不必去请芯片制造厂商设计和制作专用的集成电路芯片了。

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存配置数据。这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。

下面我们介绍两种常用的PLD器件:CPLD和FPGA;

CPLD:复杂可编程逻辑器件,CPLD主要由逻辑块、可编程互连通道和I/O块三部分构成。CPLD中的逻辑块类似于一个小规模PLD,通常一个逻辑块包含4~20个宏单元,每个宏单元一般由乘积项阵列、乘积项分配和可编程寄存器构成。每个宏单元有多种配置方式,各宏单元也可级联使用, 因此可实现较复杂组合逻辑和时序逻辑功能。对集成度较高的CPLD,通常还提供了带片内RAM/ROM的嵌入阵列块。可编程互连通道主要提供逻辑块、宏单元、输入/输出引脚间的互连网络。输入/输出块(I/O块)提供内部逻辑到器件I/O引脚之间的接口。

FPGA :FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA 器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。

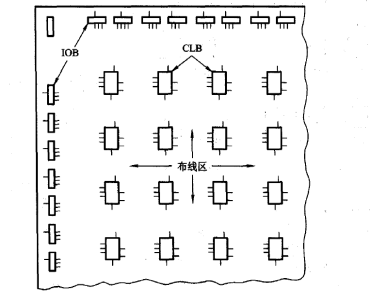

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

图1 :FPGA的基本结构图

FPGA在安防,工业等领域有着比较广泛的应用,比如安防领域的视频编码解码等协议在前端数据采集和逻辑控制的过程中可以利用FPGA处理。工业领域主要采用规模较小的FPGA,满足灵活性的需求。另外,由于 FPGA具有比较高的可靠性,因此在军工以及航天领域也有比较广泛的应用。未来,随着技术的不断完善,相关工艺将会完成升级改造,在诸多新型行业比如大数据等,FPGA将会有更为广泛的应用前景。伴随5G网络的建设,会大量应用FPGA,人工智能等新型的领域也会更多的用到FPGA。

目前用CPLD(复杂可编程逻辑器件)和 FPGA(现场可编程逻辑阵列)来进行ASIC设计是最为流行的方式之一,它们的共性是都具有用户现场可编程特性,都支持边界扫描技术,但两者在集成度、速度以及编程方式上具有各自的特点。

编辑:黄飞

-

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介2024-03-28 1783

-

什么是可编程逻辑2009-05-29 3799

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 17685

-

可编程逻辑器件2014-04-15 3676

-

PLD可编程逻辑器件2021-07-22 2321

-

FPGA零基础学习:半导体存储器和可编程逻辑器件简介2023-02-23 1245

-

可编程逻辑器件设计2006-03-25 1179

-

可编程逻辑器件基础及应用实验指导书2010-03-24 785

-

基于单片机的复杂可编程逻辑器件快速配置方法2009-03-28 1157

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1163

-

第二讲 可编程逻辑器件简介2016-04-26 940

-

半导体存储器和可编程逻辑器_PPT讲解2016-09-01 1196

-

可编程逻辑器件(书皮)2022-07-10 786

-

现场可编程门阵列简介2021-04-07 1550

全部0条评论

快来发表一下你的评论吧 !