深入剖析AXI的协议与架构(上)

电子说

1.4w人已加入

描述

本篇文章为大家介绍AXI的协议与架构。

内容概括

这次为大家讲述的内容包括:

关于AXI协议

AXI架构

0****1

AXI协议

AMBA AXI协议支持用于主从模块之间通信的高性能、高频率系统设计。

AXI****协议的定位:

•适用于高带宽、低时延设计

•不需要复杂的桥就可以满足高频时钟的要求

•满足大多数模块的接口需求

•适用于初始延迟较高的存储器控制

•在总线互联架构上提供更大的灵活性

•后向兼容AHB和APB接口

**AXI **协议的主要特征:

•地址/控制操作与数据操作分离

•使用byte strobes(字节选通)信号实现非对齐数据传输

•使用burst传输(突发传输)时只需要发送首地址,便可以发送一段数据

•读数据和写数据通道独立,从而支持DMA (low-cost Direct Memory Access)

•支持outstanding功能,可以发送多个地址进行读写

02

AXI架构

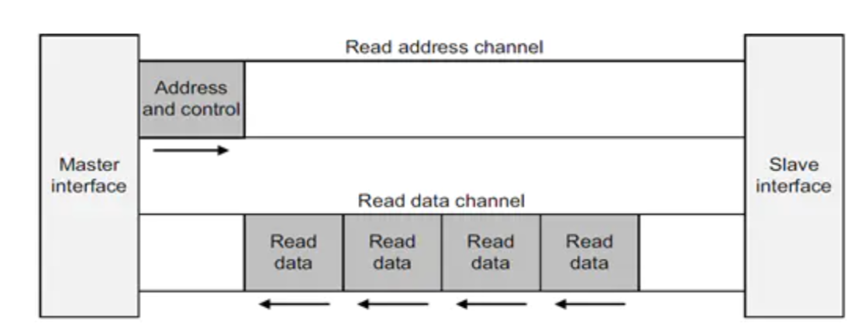

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

a

读架构

地址通道携带控制消息,用于描述被传输的数据属性;数据传输使用写通道来实现master到slave的传输,slave使用写响应通道来完成一次写传输;读通道用来实现数据从slave到master的传输。

相关信号:

读地址通道信号:

| 信号名 | 来源 | 描述 |

|---|---|---|

| ARID | master | 读地址ID |

| ARADDR | master | 读地址 |

| ARLEN | master | 突发长度 |

| ARSIZE | master | 突发尺寸(每次突发传输的byte数) |

| ARBURST | master | 突发类型(FIXED,INCR,WRAP) |

| ARCACHE | master | 存储类型 |

| ARPROT | master | 保护类型 |

| ARQOS | master | QoS标识符 |

| ARREGION | master | 区域标识符 |

| ARUSER | master | 用户自定义 |

| ARVALID | master | 读地址有效(有效时表示ARADDR上地址有效) |

| ARREADY | slave | 写有效信号(有效时表示从机准备好接收读地址) |

读数据通道信号:

| 信号名 | 来源 | 描述 |

|---|---|---|

| RID | slave | 读ID标签 |

| RDATA | slave | 读数据 |

| RRESP | slave | 读响应 |

| RLAST | slave | 有效时表示为突发传输的最后一个 |

| RUSER | slave | 用户自定义 |

| RVALID | slave | 读数据有效信号 |

| RREADY | master | 主机就绪信号(有效时表示) |

b

写架构

AXI使用基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

- 读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

- 读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024 bit)和指示读传输完成的读响应信号。

- 写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,master无需等待slave对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16...1024 bit)和字节线(用于指示8 bit 数据信号的有效性)。

- 写响应通道:slave使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

写地址通道信号:

| 信号名 | 来源 | 描述 |

|---|---|---|

| AWID | master | 写地址ID(用于区分该地址属于哪个写地址组) |

| AWADDR | master | 写地址 |

| AWLEN | master | 突发长度 |

| AWSIZE | master | 突发尺寸(每次突发传输的最长byte数) |

| AWBURST | master | 突发方式(FIXED,INCR,WRAP) |

| AWCACHE | master | 存储类型(标记系统需要的传输类型) |

| AWPROT | master | 保护模式 |

| AWQOS | master | QoS标识符 |

| AWREGION | master | region标识符(当slave有多种逻辑接口时标识使用的逻辑接口) |

| AWUSER | master | 用户自定义信号 |

| AWVALID | master | 写地址有效信号(有效时表示AWADDR上地址有效) |

| AWREADY | master | 写从机就绪信号(有效时表示从机准备好接收地址) |

写数据通道信号:

| 信号名 | 来源 | 描述 |

|---|---|---|

| WDATA | master | 写数据 |

| WSTRB | master | 数据段有效(标记写数据中哪几个8位字段有效) |

| WLAST | master | last信号(有效时表示当前为突发传输最后一个数据) |

| WUSER | master | 用户自定义信号 |

| WVALID | master | 写有效信号(有效时表示WDATA上数据有效) |

| WREADY | slave | 写ready信号(有效时表示从机准备好接收数据) |

写响应通道信号:

| 信号名 | 来源 | 描述 |

|---|---|---|

| BID | slave | 响应ID |

| BRESP | slave | 写响应 |

| BUSER | slave | 用户自定义信号 |

| BVALID | slave | 写响应信号有效 |

| BREADY | master | 写响应ready(主机准备好接受写响应信号) |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析RabbitMQ高可用架构设计2025-08-18 1091

-

学习架构-AMBA AXI简介2023-08-09 1039

-

AMBA AXI协议指南2023-08-02 721

-

深入剖析AXI的协议与架构(下)2023-05-04 3350

-

AXI总线协议:AHB、APB、AXI对比分析2023-04-14 5026

-

使用SpinalHDL实现一个支持AXI协议的互联架构2022-06-29 1786

-

AXI接口协议详解2022-04-08 6022

-

深入 AXI4总线 (四):RAM 读取实战2022-02-07 1034

-

AMBA 3.0 AXI总线接口协议的研究与应用2021-04-12 1205

-

深入AXI4总线一握手机制2021-03-17 1269

-

AXI总线协议的几种时序介绍2019-05-12 11882

-

最深入最经典的电容剖析2012-08-02 13154

全部0条评论

快来发表一下你的评论吧 !