AMBA总线知识之AHB(上)

电子说

描述

AMBA总线阵营的强大超乎多数人的想象。AMBA总线是一个在SoC领域使用的事实上的标准。AMBA总线的最大优点是开放的架构,和因此带来的免费。开放的总线标准使AMBA总线迅速普及,而且更易吸收整个半导体界的成果。

AMBA总线标准提供的AXI,AHB,ASB,APB和ATB总线,不仅使用在ARM处理器系统中,MIPS和PowerPC处理器也开始使用AMBA总线。在接下来的文章中我们重点为大家介绍AHB, AXI总线协议。

内容概括

这次为大家讲述的内容包括:

AHB介绍

总线互联

AHB信号描述

基本传输

0****1

AHB介绍

AMBA是为提高性能综合设计的要求而产生的新一代AMBA总线它是支持总线主机和提供高带宽的高性能总线。AHB实现了高性能,高时钟频率系统的以下特征要求:突发传输;分块处理;单周期总线主机移交;单时钟沿操作;非三态执行;

AHB 的设计可能包含一个或者多个主机,一个典型的系统将至少包含处理器和测试接口。然而,将直接数据存取(DMA)或者数字信号处理器(DSP)包含作总线主机也很普遍。

典型的 AMBA AHB 系统设计包含以下的成分:

AHB 主机 :总线主机能够通过提供地址和控制信息发起读写操作。任何时候只允许一个总线主机处于有效状态并能使用总线。

AHB 从机 :总线从机在给定的地址空间范围内响应读写操作。总线从机将成功、失败或者等待数据传输的信号返回给有效的主机。

AHB 仲裁器 :总线仲裁器确保每次只有一个总线主机被允许发起数据传输。即使仲裁协议已经固定,任何一种仲裁算法,比如最高优先级或者公平访问都能够根据应用要求而得到执行。AHB 必须只包含一个伸裁器,尽管在单总线主机系统中这显得并不重要。

AHB 译码器: AHB 译码器用来对每次传输进行地址译码并且在传输中包含一个从机选择信号。所有 AHB 执行都必须仅要求有一个中央译码器。

02

总线互联

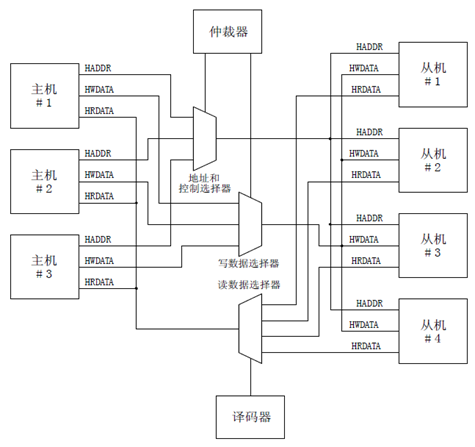

AHB总线协议设计使用一个中央多路选择器互联方案。使用该方案所有总线主机设备输出地址和控制信号来指示它们想执行的传输,同时仲裁器决定哪一个主机能够将它的地址和控制信号连通到所有的从机。当然也需要—个译码器来控制读数据和响应多路信号选择器,多路信号选择器选中米自传输中所包含从机的适当信号。图 1表示了实现包含三个主机和四个从机的AHB设计的结构要求。

图1 多路选择器互联

0****3

AHB信号描述

| 名称 | 来源 | 描述 |

|---|---|---|

| HCLK总线时钟 | 时钟源 | 时钟为所有总线传输提供时基。所有信号时序都和HCLK的上升沿相关。 |

| HRESETn复位 | 复位控制器 | 总线复位信号,低电平有效,用来复位系统和总线。这是唯一低电平有效的信号。 |

| HADDR[31:0]地址总线 | 主机 | 32位地址总线 |

| HTRANS[1:0]传输类型 | 主机 | 表示当前传输的类型,可以是连续,不连续,空闲和忙 |

| HWRITE传输方向 | 主机 | 该信号为高表示一个写传输,为低表示一个读传输 |

| HSIZE[2:0]传输大小 | 主机 | 表示传输的大小,三位表示0…7,分别对应8bits(byte), 16bits(halfword),32bits(word),64bits, 128bits,256bits, 512bits,1024bits |

| HBURST[2:0]突发类型 | 主机 | 表示传输是否组成了突发的一部分。支持4个,8个,16个节拍的突发传输,突发传输可以使增量或回环。 |

| HPROT[3:0]保护控制 | 主机 | 提供总线访问的附加信息,主要是给那些希望执行某种保护级别的模块使用的。这个信号指示当前传输是否为预取指令或者数据传输,同时也表示传输是保护模式访问还是用户模式访问。对带存储器管理单元的总线主机而言这些信号也用来指示当前传输是高速缓存的(cache)还是缓冲的(buffer)。 |

| HWDATA[31:0]写总线数据 | 主机 | 写数据总线用来在写操作期间从主机到总线从机传输数据。建议最小的数据总线宽度为 32 位。在要求高带宽运行时扩展(数据总线)还是很容易的。 |

| HSELx从机选择 | 译码器 | 每个 AHB 从机都有自己独立的从机选择信号并且用该信号来表示当前传输是否是打算送给选中的从机。该信号是地址总线的简单组合译码。 |

| HRDATA[31:0]读数据总线 | 从机 | 读数据总线用来在读操作期间从总线从机向总线主机传输数据。建议最小的数据总线宽度为 32 位。在要求高带宽运行时扩展(数据总线)还是很容易的。 |

| HREDAY传输完成 | 从机 | 当 HREADY 为高时表示总线上的传输已经完成。在扩展传输时该信号可能会被拉低。注意:总线上的从机要求 HREADY 作为输入输出信号。 |

| HRESP[1:0]传输响应 | 从机 | 传输响应给传输状态提供了附加信息。提供四种不同的响应:OKEY、 ERROR、 RETRY 和 SPLIT。 |

0****4

基本传输

一笔传输由如下两部分组成:

地址阶段 :一个周期

数据阶段 :一个或多个周期,由HBURST信号决定需要几个有效周期,可以由HREADY发出请求延长一个周期。

01

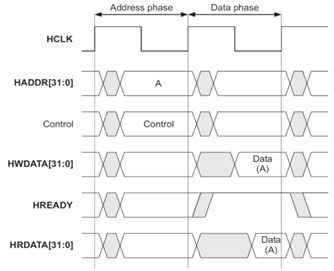

没有等待状态的single transfer

-

第一个周期的上升沿,主机将地址信息和控制信息发送到总线上;

-

第二个周期的上升沿,从机采样地址和控制信号,并将HREADY拉高;如果是写操作,主机会在第二个周期的上升沿过后传输要写入的数据;如果是读操作,从机会在HREADY信号拉高后将读取的数据写入总线;

-

第三个周期的上升沿,如果是写操作,主机获取HREADY高信号,表明从机已成功接收数据,操作成功;如果是读操作,主机获取HREADY高信号,表明此时的读数据有效并且接收下来,操作成功。需要注意,HREADY信号在数据有效期间必须为高,并且延续到第三个周期的上升沿之后,确保主机的正确采样。

02

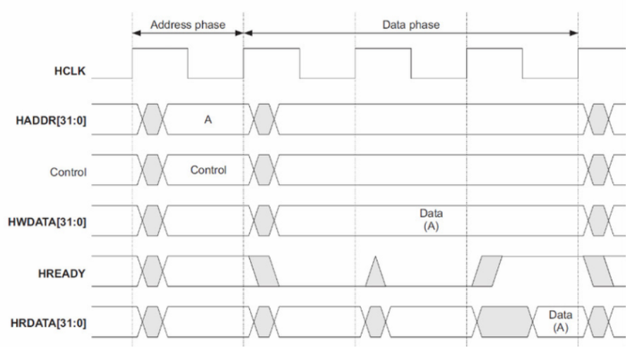

slave插入等待状态的single transfer

从机可以及时处理主机请求,但也可能存在从机太慢不能立即处理的情况。这时需要让主机稍微等一等,需要从机插入一些等待的状态。如下图所示,HREADY信号在第二和第三周期拉低,意在告诉主机,从机不能立即处理,需要主机等待2个周期。在这里需要注意2点:

如果是写操作,主机要在等待期间保持写数据不变,直到本次传输完成;如果是读操作,从机不需要一开始就给出数据,仅当HREADY拉高后才给出有效数据。

03

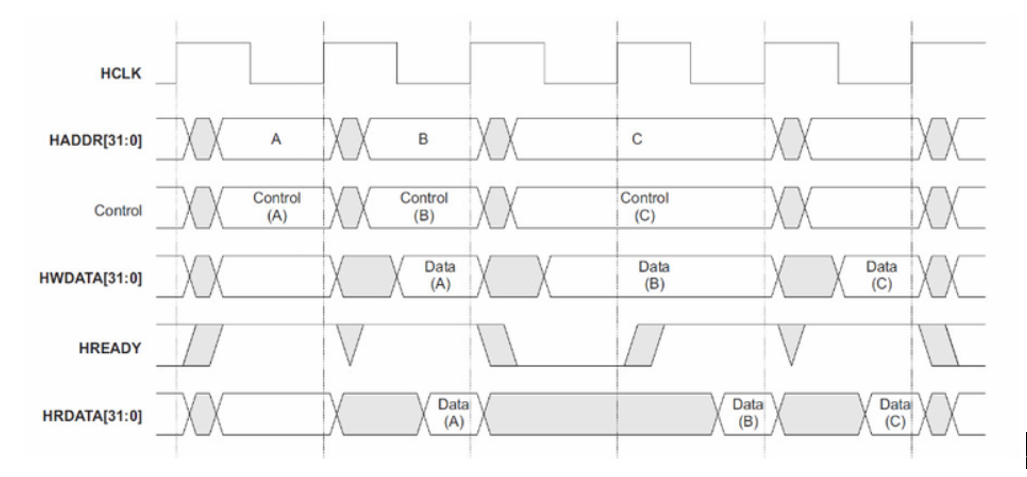

多个single transfer的pipeline操作

扩展数据周期的一个负效应是必需延长相应的下一笔传输的地址周期。A和C为零等待传输,B加入了一个等待周期,因此相应的C地址周期要进行扩展。

- 第一个周期,主机发起一个操作A,并驱动地址和控制信号;

- 第二个周期,从机收到了来自总线的请求,将HREADY信号拉高;

- 第二个周期上升沿后,主机发现有操作B需要执行,并且检查到上一周期的HREADY为高,则发起第二个操作B;

- 第三个周期,主机获取HREADY信号为高,表示操作A已经完成;

- 第三个周期上升沿后,主机发现有操作C需要执行,并且检查到上一周期的HREADY为高,则发起第三个操作C;

- 第三个周期上升沿后,从机由于繁忙插入了一个等待状态,将HREADY拉低;

- 第四个周期,主机获取HREADY信号为低,知道从机希望等待,于是主机保持和上一拍一样的信号;

- 第四个周期,从机处理完了事务,将HREADY信号拉高,表示可以继续处理;

- 第五个周期,主机获取HREADY信号为高,知道从机已经可以处理B操作;

- 第五个周期上升沿后,B操作完成;

- 第六个周期上升沿后,C操作完成。

需要注意几点:

HREADY在一定程度上表示了从机的pipeline能力,在AHB中是2个pipe,也就是总线上最多存在2个未处理完的transfer。只有当总线上未完成的transfer少于2个时,主机才能发起操作。

-

AMBA总线—ahb简介2023-06-05 7133

-

AMBA协议之AHB介绍2023-05-04 5123

-

AMBA中的AHB总线协议详解2022-06-07 5248

-

AMBA AHB总线与APB总线资料合集2022-04-07 5221

-

AMBA、APB、AHB简介2022-02-17 2444

-

ARM总线协议AMBA中AHB、APB的区别与联系2022-02-09 2479

-

STM32菜鸟学习手册——AMBA、APB、AHB简介2021-12-22 1188

-

数字IC验证:ARM总线协议AMBA中AHB、APB的简介、区别与联系2021-12-05 2299

-

总线概述之AMBA总线2017-11-16 39587

-

AHB总线应用教程2017-11-15 22760

-

基于AMBA-AHB总线的SDRAM控制器设计方案2014-01-02 5293

-

基于AMBA片上总线的片上系统2010-09-01 2426

-

AHB片上系统总线的建模与验证2009-11-30 1030

全部0条评论

快来发表一下你的评论吧 !