数字电路基础知识分享3

电子说

描述

我们在上节主要学习了逻辑表达,以及卡诺图化简方法。前面都还没有谈及电路和器件的内容,我们可以理解为,前面讲的都是数学逻辑层面的一些内容。

本节开始我们将开启电路与器件的内容,主要是看如何通过电路与器件来实现前面的逻辑关系。本小节主要会聚焦在MOS管特性,由MOS管搭建的简单逻辑器件,以及D触发器器件。

内容概括

这次为大家讲述的内容包括:

MOS管特性

MOS逻辑门

D触发器

0****1

MOS管特性

mos管是金属(metal)、氧化物(oxide)、半导体(semiconductor)的场效应晶体管,或者是金属-绝缘体(insulator)、半导体。MOS管的源漏可以颠倒,都是形成在P型背栅中的N型区。大多数情况下,这两个区域是相同的,即使两端颠倒,也不会影响器件的性能。这种设备被认为是对称的。

场效应晶体管 (FET) 将输入电压的变化转换为输出电流的变化。FET 的增益等于其跨导,定义为输出电流变化与输入电压变化之比。市场上常见的有N沟道和P沟道。FET 通过在绝缘层上投射电场来影响流过晶体管的电流。事实上,没有电流流过这个绝缘体,因此 FET 的栅极电流非常小。最常见的 FET 使用一层薄薄的二氧化硅作为 GATE 下方的绝缘体。这种晶体管称为金属氧化物半导体 (MOS) 晶体管或金属氧化物半导体场效应晶体管 (MOSFET)。由于 MOS 管有以下重要特性因此在很多应用中已经取代了双极晶体管。

- 导通特性

导通的意义是作为开关,相当于开关闭合。Vgs满足一定条件就会导通。

- 损失特性

导通后均有导通电阻存在,电流就会被电阻消耗能量,这部分叫做导通损耗;小功率的管子导通电阻一般几毫欧几十毫欧,Vgs电压不一样电阻也不一样。管子在导通和截止时,两端电压有个降落过程,电流有个上升过程,在这段时间内管子的损失是电压和电流的乘积,称之为开关损失;通常开关损失比导通损失大很多,频率越快,损失越大。缩短开关时间,降低开关频率均能减小开关损失。

- 寄生电容驱动特性

栅极和源/漏级之间存在寄生电容,MOS管的驱动理论上是对电容的充放电;对电容的充电需要一个电流,由于电容充电瞬间可以看成短路,所以瞬间电流会比较大,所以选型时需要注意抗冲击电流大小。

- 寄生二极管

漏极源极之间有个寄生二极管也叫做体二极管,在感性负载(马达继电器)应用中,主要用来保护回路。不过体二极管只在单个MOS管中,集成芯片中是没有的。

- ** 转移特性**

场效应管的转移特性是指漏源电压固定时,栅源电压Vgs对漏极电流Id的控制特性;

02

MOS逻辑门

01

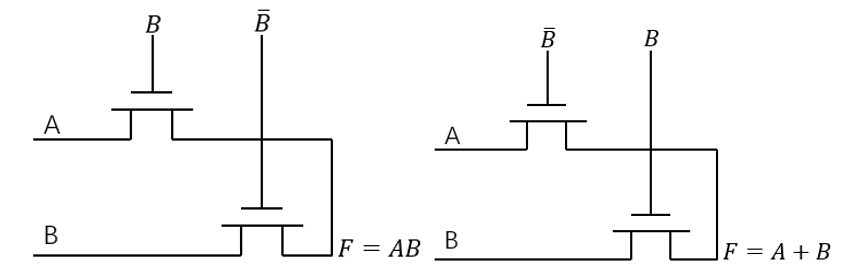

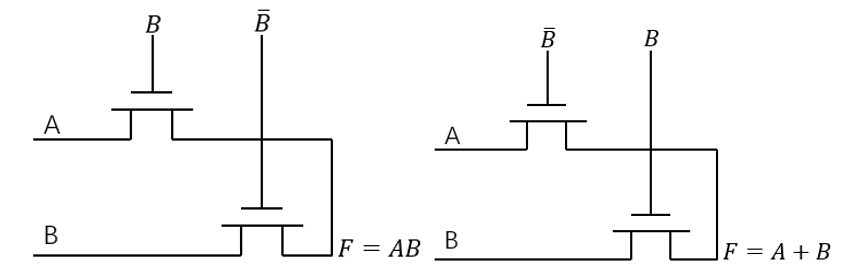

**CMOS互补门

**

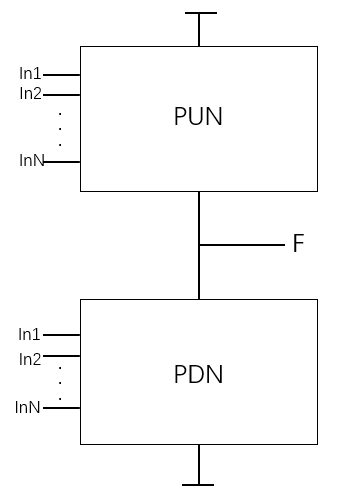

静态CMOS 门是上拉网络(PUN)和下拉网络(PDN)的组合,如图1 所示。图中显示了一****个通用的N个输人的逻辑门,它的所有输人都同时分配到上拉和下拉网络。PUN的作用是每当逻辑门的输出意味着逻辑1时(取决于输入)它将提供一条在输出和 VDD之间的通路。同样,PDN的作用是当逻辑门的输出意味着逻辑0时把输出连至 VSS。PUN 和PDN 网络是以相互排斥的方式构成的,即在稳定状态时两个网络中有且只有一个导通。这样,一旦瞬态过程完成,总有一条路径存在于 VDD和输出端F之间(即高电平输出“1”)或存在于 VSS和输出端下之间(即低电平输出〝0”)。这就是说,在稳定状态时输出节点总是一个低阻节点。

** 图1 PUN和PDN组成的互补CMOS门**

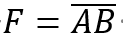

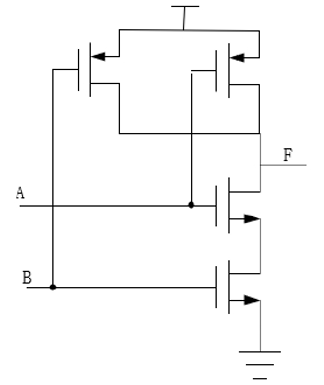

**我们以与非门为例子图2 为一个二输入与非门。PDN网络由俩个串联的NMOS器件构成,在A和B均为高时导通。PUN是它的对偶网络,由俩个并联的PMOS构成。这意味着,如果A=0或者B=0则F为1,这相当于  。同理在图3中我们为大家画出了或非门的电路。**

。同理在图3中我们为大家画出了或非门的电路。**

与非门:上并下串(上为PMOS,下为NMOS)

图2

或非门:上串下并

图3

CMOS互补门主要是用来实现一种反逻辑,我们也可以在与非门/或者门之后增加一个反向逻辑(非门)来实现与门/或门的功能,反向器的电路在下面的图中给大家画出。

当然上面说的方法实现与/或门会使MOS管的数量增大很多,这里也为大家介绍一种使用较少MOS管实现与/或门的方法。

03

D触发器

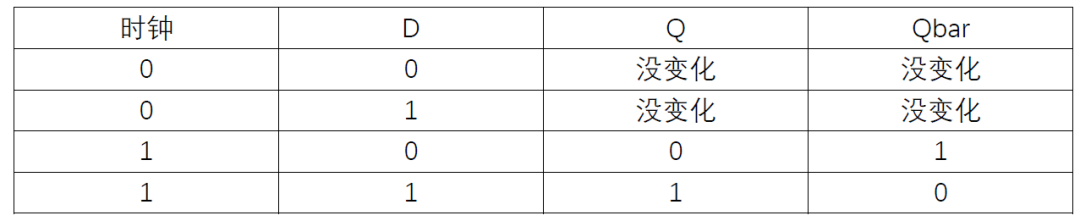

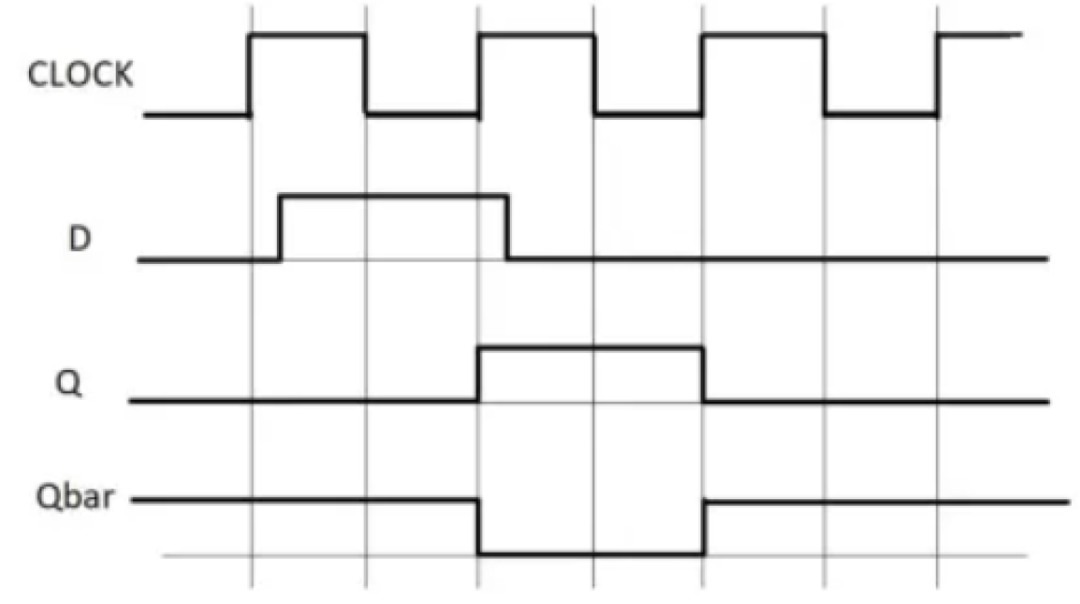

D 触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。因此,D 触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和 "1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

**D 触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CLK(时钟脉冲)=1时即可触发,后者多在CLK的边沿(正跳变 0→1)触发。D 触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置 0、置 1 两种功能。对于边沿 D 触发器,由于在 CLK=1 期间电路具有维持阻塞作用,所以在 CLK=1 期间,D 端的 数据状态变化,不会影响触发器的输出状态。D 触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等等。**

D触发器真值表:

D触发器时序图:

-

电路基础知识总结2023-08-30 6166

-

电路基础知识讲解 电路基本元件知识与电路元件的伏安特性和功率特性2023-07-31 6285

-

数字电路基础知识分享12023-05-04 2086

-

17个图解数字电路基础知识2023-01-14 18238

-

数字电路基础2022-03-21 2101

-

电路基础知识分享2022-03-10 2170

-

数字电路基础知识相关资料下载2021-12-01 2617

-

直流电路基础知识2021-09-15 1821

-

数字电路基础知识与要点2017-09-19 1772

-

磁路和电路基础知识2017-04-07 2528

-

数字电路基础知识2011-04-01 5287

-

模拟电路基础知识教程2009-12-04 42588

-

电子电路基础知识2008-01-15 249819

全部0条评论

快来发表一下你的评论吧 !