了解ADC参数如何以及为何变化的四个影响因素

描述

在我们的 例子 中, 客户 将 12 位 分辨 ADC 与 MCU 集成 用于 其 测试 系统, 他们认为 该 ADC 将 提供 满足 系统 要求 所需 的 性能。集成是功能的最佳朋友。集成允许向设备添加更多功能,从而减小系统尺寸和成本。但集成的敌人是性能。在客户选择的MCU中,MCU集成了30多种功能,ADC就是其中之一。必须在单芯片中容纳如此多的功能意味着要管理性能方面的妥协。

集成如何影响性能?让我们来看看导致ADC性能下降的四个因素:集成本身、测试能力、温度变化和工艺技术。

集成

影响ADC性能的第一个挑战是集成。MCU将紧挨着设计完美的ADC。快速开关MCU会将开关噪声和接地反弹引入ADC电路。向任何有经验的模拟设计师询问影响板级模拟性能的电路布局问题,他会告诉你任何莎士比亚戏剧相媲美的悲剧故事。现在想象一下,电路板尺寸减小到IC的面积,问题变得难以解决。时钟同步和管理技术可用于将这些影响降至最低,但外设和异步事件的相互作用仍会影响ADC性能。

测试能力

第二个挑战是测试能力。微控制器(MCU)是数字设备,因此,它们使用数字测试向量在数字测试平台上进行测试。数字测试解决方案针对最短的测试时间进行了优化,可在最短的时间内通过测试获得最多的单元。这些 测试 平台 通常 具有 有限 的 低 性能 模拟 测试 能力。这就是为什么微控制器上的模拟外设规格要么“通过设计保证”,要么“通过表征保证”。这些测试仪通常只能测试模拟功能或模拟功能,他们没有测试模拟性能的能力 - 模拟性能如何执行其功能。此外,测试仪的性能限制限制了ADC的性能规格。如果测试仪仅具有 1 kSPS 12 位功能,则无法测试指定为 100 MSPS 8 位 ADC 性能的器件。此外, 将 模拟 测试 功能 添加 到 数字 测试 平台 上 需要 测试 成本 增加 一个 数量 级, 从而 相应 增加 设备 成本。

温度变化

第三个挑战是模拟性能的最大敌人之一——温度。在一个完美的世界里,室外温度总是72°F,电子设备总是在25°C下工作,但两者都不会发生。随着电子设备靠近传感器,电子设备的工作温度会发生变化,在某些情况下变化超过100°C。 这种温度变化会对电子电路产生负面影响,尤其是模拟电路。想象一下,如果您设计了完美的ADC,然后在它旁边添加一个温度源。现在想象一下,温度源是变化的,有时是热的,有时是暖的。这会严重破坏您的ADC性能。这正是ADC旁边的MCU正在做的事情。从高速有功功率(热)到待机、睡眠或休眠(不太热),为了在这种环境中获得可预测的性能,需要添加温度补偿电路。这将增加尺寸和成本,而与MCU集成的ADC通常不会沉迷于这种奢侈。

工艺技术

第四个挑战是工艺技术。由于集成ADC的器件的主要功能是MCU,因此所使用的工艺技术是MCU友好的工艺是有道理的。毕竟,客户需要为MCU付费,而ADC只是一个外设,因此仅针对设备上的外设选择优化的工艺是没有意义的。

MCU通常采用较小的几何形状工艺设计,可提供良好的数字密度和高速晶体管。对ADC的好处是,使用这样的过程将减小ADC的尺寸。小几何尺寸工艺可能会减小ADC的尺寸,但由于工艺成本大幅增加,ADC的总成本实际上可能会增加。然而,较高的芯片成本被较低的测试成本所抵消。

此外,通过限制工艺中可用元件的尺寸,ADC噪声会增加,特别是热噪声或kT/C噪声。ADC设计中使用较大的电容来降低热噪声,这是较小几何形状工艺的重要设计约束。事实上,在更小的几何尺寸上实现模拟性能所需的组件在几何上更具挑战性。此外,较小几何形状的电容器会引入泄漏、非线性和匹配问题,这些问题不像在较大几何形状过程中那样受到控制。晶体管也是如此。这种缺乏控制最终将导致制造过程变化,这将表现为ADC性能的参数变化。

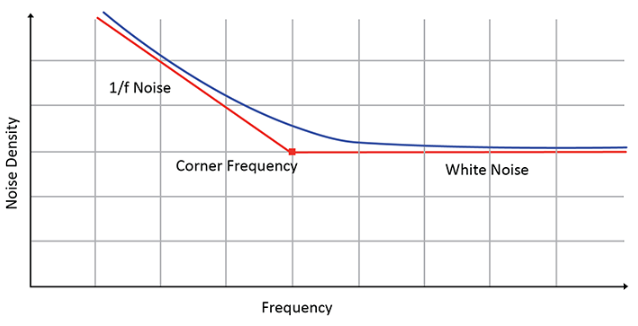

较小几何工艺的另一个挑战是1/f噪声。1/f 噪声在低频时占主导地位,与直流相比大约降低 1/SQRT(频率)。在较高频率下,白噪声开始主导1/f噪声,称为转折频率,如图1所示。(剧透预警!如果要通过使用数字补偿技术(如平均或过采样)来提高性能,则需要确保仅对包含白噪声而不是 1/f 噪声的值进行采样。较小的几何工艺与较大的几何工艺相比,拐角频率偏移更高 – 明显更高。这正是数字滤波技术(如平均或过采样)不能提高具有高1/f转折频率的系统性能的原因,事实上,在某些情况下,数字滤波技术会降低系统性能。从本质上讲,无论ADC设计有多好,过程的局限性最终将决定ADC可实现的性能。

这些影响因素如何影响ADC性能并最终影响系统性能?

审核编辑:郭婷

-

使用AD9219-65M ADC四个通道输出不正确2018-09-07 2209

-

请问温度的四个参数分别代表什么意思?2019-03-15 6623

-

华为副总裁杨涛:数字经济有四个特征会产生三大变化2018-10-01 3404

-

简述:影响电缆绝缘电阻的四个因素2020-05-08 6784

-

从四个方面解读PCB射频电路基础特性及重要因素2020-08-07 1253

-

LTM9012:采用集成驱动程序的四个14位125 Msps ADC产品手册2021-04-25 655

-

AD7264:1 MSPS,14位,带PGA和四个比较器的同步采样SAR ADC数据表2021-05-08 726

-

AD7262:1 MSPS,12位,带PGA和四个比较器的同步采样SAR ADC数据表2021-05-14 683

-

UG-046:使用PLL 192 kHz、24位编解码器评估AD1974四个ADC2021-05-20 737

-

示波器经常说“四个部分”是哪四个部分?2022-10-19 2562

-

了解何时以及为何系统可靠性很重要2023-01-05 994

-

vlookup函数的四个参数含义2023-12-01 9383

-

IGBT的四个主要参数2024-07-25 9516

-

如何以及为何要在EtherCAT®应用中使用DP838262024-08-27 345

-

模数转换电路的四个过程2025-02-03 2416

全部0条评论

快来发表一下你的评论吧 !