全网最实用的Verdi教程2

电子说

描述

20 查询模块实例化位置

① 在设计结构中双击实例化模块的名字 ->源代码窗口高亮了设计部分的模块名。② 再双击高亮的模块名->看到在上层模块中的哪一行被调用了

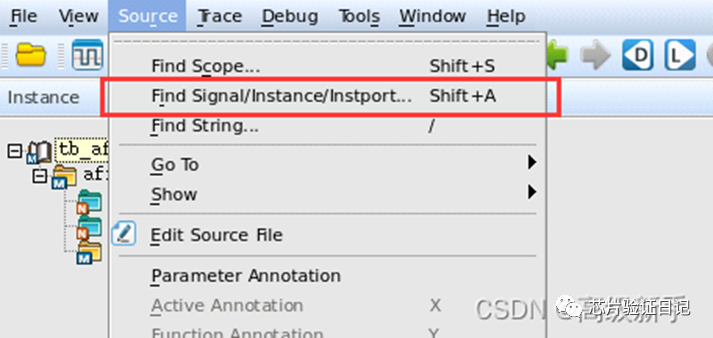

21 在nTrace中如何查找模块和信号

或Shift+A:

搜索通配符 *** **

22查找位于不同层次的驱动信号【跨层次查看信号,看最终驱动谁,或者看最终被谁驱动】

23 如何查看设计有哪些信号

通过最右下方signal_list来查看,可以选择查看输入/输出等端口类型。

24 如何打开原理图

选中设计-> new schematic

25 如何查看nShema Window中符号对应的源代码

双击对应的功能单元电路图,即可跳转到描述该单元的源代码

26 使用 Fan-In Cone追踪某个信号的驱动逻辑

首先要用上面的办法来查找信号,高亮选中;调用该工具:

这样就可以看到某个信号是如何生成的(可以通过View选项来显示信号名)

27 如何产生 partial hierarchy schematic

用来查看与选择特定信号有关的逻辑/模块

①选择需要查看的信号(可以通过shift键来选择多个信号)

②:

选择查看与wclk和wrst_n有关的信号/模块/逻辑:

28 如何移动原理图中的器件

鼠标左键选中,按住右键进行拖拽。

29 状态机相关操作

[1] 打开原理图

[2] 双击相应状态机视图后,呈现状态机图

[3] 查看状态的执行和跳转

[4] 查看状态以及节点的相关源代码

选择状态,然后使用鼠标中键拖拽状态到nTrace中的源代码视图中即可

[5] 查看在什么时候状态机转移到某个状态?《与tb有关》

① 要依靠tb②打开nstate后,要导入波形③

[6] 查看某一种状态转移【状态循环】情况是否会发生

[7] 如何查看某个状态被执行了多少次(与TB有关)

[8] 如何查看某个状态转移到另一个状态的转移次数(与TB有关)

(五) Verd波形(含emulation)加载

1 打开波形

打开常规波形:

verdi -dbdir ./simv.dair -ssf debug.fsdb

打开emulation的波形:

verdi -dbdir ./simv.dair -ssf debug.zwd

打开emulation转换前的波形:

verdi -emulation --zebu-work zebu.work --timescale 1ns --input debug.ztdb

打开fsdb波形和编译文件

verdi -elab com_path -ssf fsdb_path

com_path:编译产生的临时文件存放的路径;例:*.daidir/kdb.elab++;

fsdb_path:编译产生的fsdb的路径;

2 打开 source code

如果没有kdb文件,可以通过flist打开source code

verdi -f tb_top.flist

3 加载设计

veidi加载设计的脚本命令

verdi -sv -f tb_top_filelist.f -top tb_top &

告知软件支持SystemVerilog,加载设计的文件列表,设置设计顶层,后台执行

4 重新加载设计和波形

选中波形或设计文件L(shift + i) 重新加载波形或设计文件,在新一次仿真完成之后Roload即可。

5 波形文件保存*.rc

使用verdi保存已经拉出来的信号方便下次使用,按键shift+S可以将波形保存为xxx.rc格式文件,使用波形文件时,按快捷键r打开界面,选择波形。可以避免下次打开重新添加信号。

(六) Verdi常用快捷键总结

ctrl+w:将鼠标指向需要添加到波形上的信号名,通过该快捷键将该信号添加到波形上;

shift+l:当鼠标指向波形区时刷新波形,当鼠标指向代码区(src1)时刷新代码;

z:缩小波形,显示更长时间的波形;

Z:放大波形,显示更短时间内的波形;

f:显示全局的波形;

shift+s:将当前存在于到波形区的信号保存为.rc后缀的信号列表;

shift+m:波形区快捷添加标记时刻;

ctrl+d:删除所有信号列表;

x:在代码区快捷查看所有信号的当前状态;

在波形区域固定curson(鼠标左键)和marker(鼠标中键)的距离;

h:在波形区快捷查看信号的全路径;

c:自定义信号的颜色和粗细;

t:按一次切换一次信号颜色;

m:将信号移动到黄线位置;

y:移至中央并保持居中,再按取消固定居中;

n:指针跳到信号的下一个跳变沿;

N:指针跳到信号的上一个跳变沿;

-

Verdi连续波激光器-Coherent2023-06-30 1243

-

Verdi环境配置、生成波形的方法2023-05-29 9343

-

全网最实用的Verdi教程12023-05-05 22929

-

Verdi使用技巧(三)2023-04-25 7899

-

分享《verdi用法小结》的pdf2023-02-18 2119

-

VCS+Verdi如何安装?怎么破解?2021-06-21 7679

-

如何通过自动化脚本实现Questasim和Verdi的联合仿真2021-06-13 6813

-

vcs和verdi的调试及联合仿真案例2020-09-22 10091

-

Verdi使用技巧 连续有效信号量测方法2019-05-15 11225

-

verdi-SP2软件下载2018-04-19 993

-

请教VCS和verdi怎么联合使用2015-01-22 8234

-

Verdi 54v7 LINUX2006-03-25 1706

全部0条评论

快来发表一下你的评论吧 !