全网最实用的Verdi教程3

电子说

描述

10、使用 Verdi 分析 NBA Delay 的问题

NBA 就是 NonBlocking Assignment,非阻塞赋值 的缩写。它通常用来描述一个用时钟沿触发的寄存器。在 Verilog 普及早期,人们通常会在 NBA(Nonblocking Assignments) 的<= 之后加个单位延时#1来解决早期仿真器行为不一致的问题。

所谓习惯成自然,NBA Unit Delay 在某些设计中一直沿用下来,那么如何去理解这个延时的作用呢?SNUG 上的知名作者 Clifford E. Cummings 在 2002 年有篇文章阐述的挺详细(Verilog Nonblocking Assignments With Delays, Myths & Mysteries)下面给出一些代码片断,同样感兴趣的朋友可以自己完善并用 VCS 仿真生成波形,然后用 Verdi 打开。

首先创建三个时钟,注意两个二分频时钟的创建方式不同。

always #(10/2) clk = ~clk;

always #(20/2) clk_div2_direct = ~clk_div2_direct;

always @ ( posedge clk or negedge rst_n ) begin

if ( ~ rst_n ) begin

clk_div2 <= 1'b0;

end

else begin

clk_div2 <= ~clk_div2;

end

end

然后用 clk 触发一个不停翻转的寄存器 d1,再分别用两个二分频时钟去采样,保存在 d5 和 d6 中。

always @ ( posedge clk or negedge rst_n ) begin

if ( ~ rst_n ) begin

d1 <= 1'b0;

end

else begin

d1 <= ~d1;

end

end

always @ ( posedge clk_div2 or negedge rst_n ) begin

if ( ~ rst_n ) begin

d5 <= 1'b0;

end

else begin

d5 <= d1;

end

end

always @ ( posedge clk_div2_direct or negedge rst_n ) begin

if ( ~ rst_n ) begin

d6 <= 1'b0;

end

else begin

d6 <= d1;

end

end

用 VCS 仿真的时候,加上编译时选项+fsdb+region和运行时选项+fsdb+delta。

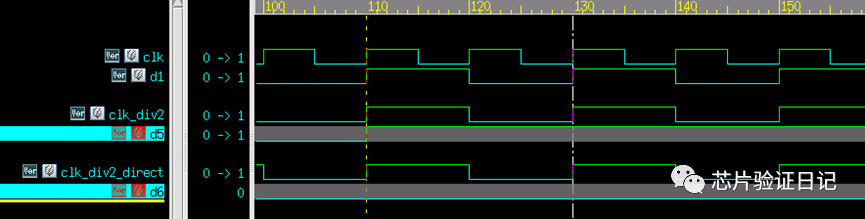

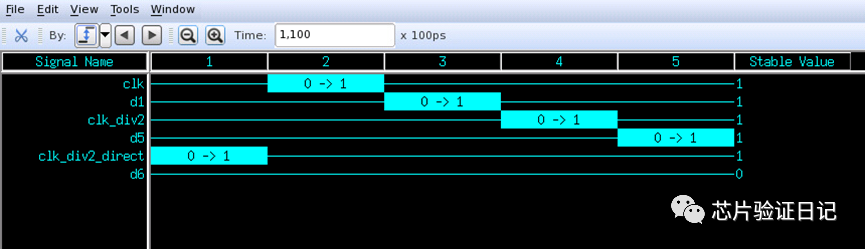

然后用 Verdi 打开生成的 fsdb 波形。正常的话,可以看到 d5 和 d6 的波形是完全不同的,一个是常0,一个是常1。

只从上图分析的话,两个二分频时钟的波形是完全一致的,被采样的数据是同一个,那么采到的数据也应该是相同的。但我们知道这两个二分频时钟的生成方式是不同的,那么不同在什么地方呢?

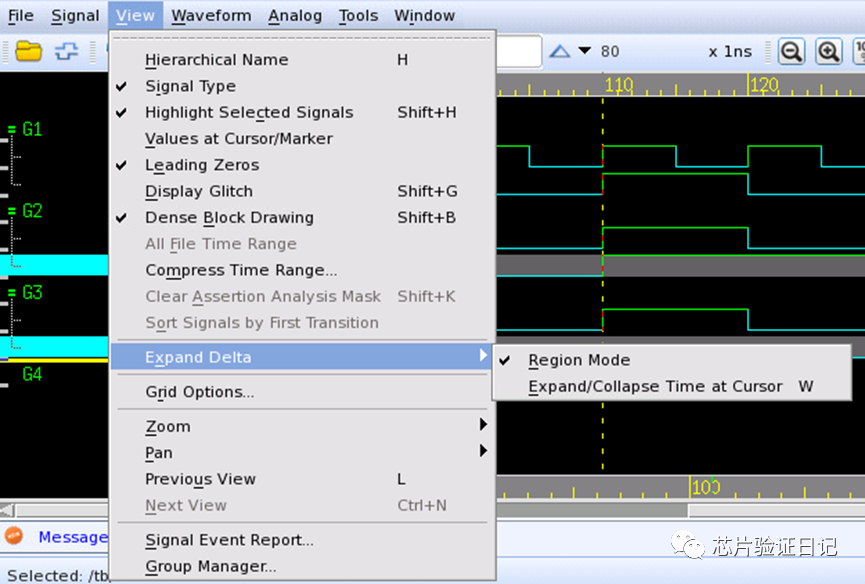

在 Verdi 的 nWave 窗口中选中 View - Expand Delta - Region Mode,把 Cursor 移动到二分频时钟的上升沿,然后点击Expand/Collapse Time at Cursor,简单点的话直接按 w 键。

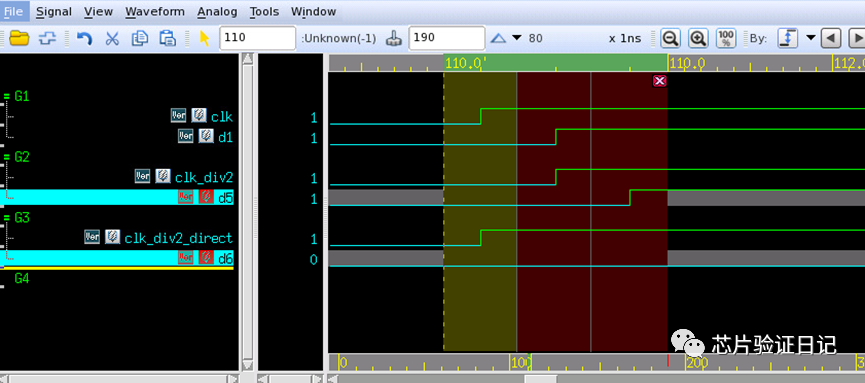

然后就可以看到这个仿真时刻的 Simulation Region,里面展示了各个 Event 和 Region 的关系。

这个例子中,只存在绿色的Active Region 和 红色的 NBA Region。在某些glitch debug的例子中,还能看到Re-Active Region和Re-NBA Region。

Region的展示可以帮助我们很好的理解Verilog 规范中的定义的信号调度。

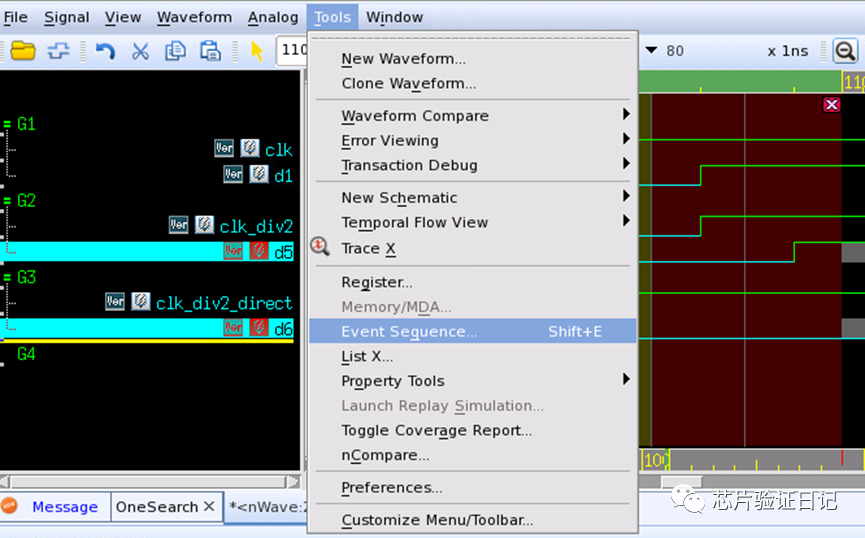

此外,Verdi还可以通过点击Tools - Event Sequence来显示图形化的Event序列。

11、数字信号的模拟化呈现

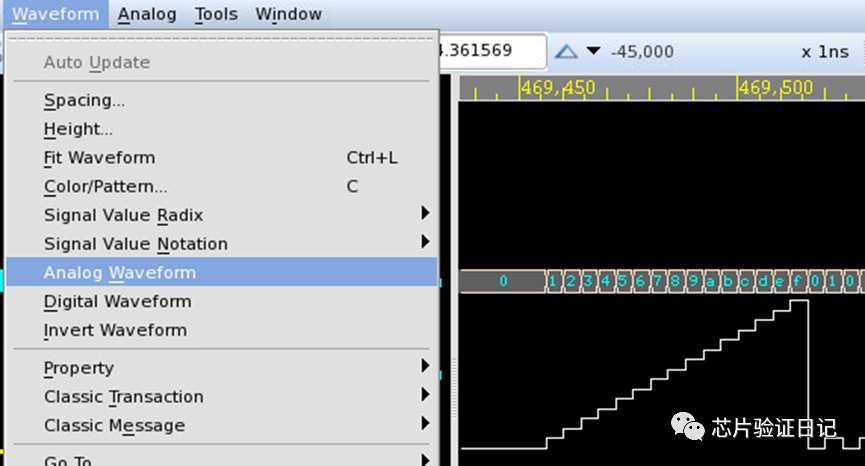

Verdi 提供了既简单又直观的操作,去绘制数字信号的模拟变化趋势。尤其是在观察周期性计数的数字信号时,例如调制频率的变化,还有 FIFO 读写地址的变化,这种方式基本是可以做到一目了然的。

操作方式:nWave 窗口菜单 - Waveform - Analog Waveform

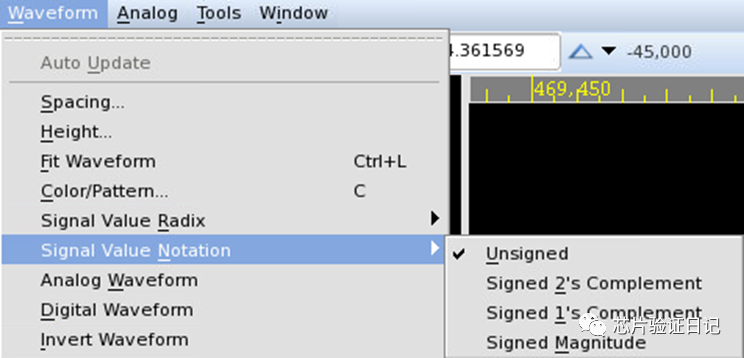

对于 Verdi 这个工具来说,它对于数字信号本身的含义目前还没有智能到可以自动识别。所以我们需要指定特定数字信号的表示方式(Notation),是无符号、二补码还是补码等等。

操作方式:nWave 窗口菜单 - Waveform - Set Notation

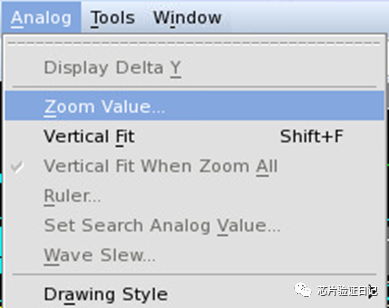

12、手动调节模拟波形的显示范围

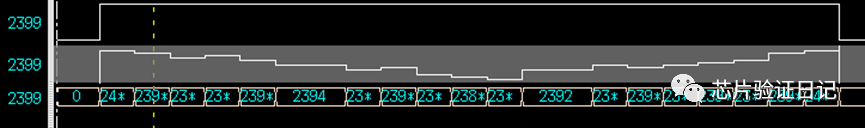

还有一个可能遇到的局限性就是模拟波形的显示范围,Verdi 在绘制数字信号的模拟波形时,默认会按照整个波形的动态范围来绘图。如果一个数字信号的初始值和工作时实际的动态范围差别很大,那么观察实际工作时的模拟波形时,波形变化的幅度相比整个动态范围就会太小,无法明了的看到小动态范围的变化趋势。

还好Verdi提供了手动调节显示范围的功能。

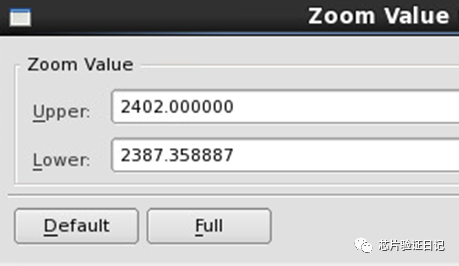

操作方式:nWave 窗口菜单 - Analog - Zoom Value...

根据需要调节上限和下限,调节过程中波形是实时更新的。

对比效果如下图,第一个信号是默认范围的,动态变化缩成一条直线了,没有观察价值。第二个信号是调整了范围的,可以清楚的看到变化趋势。第三个是原始的数字信号。

13、自动调节:切换 FSDB 文件

还有一个比较笨的解决方法是,写出FSDB 文件时,根据特定信号,从数字信号开始动态变化的时候,做一个文件切换。这样就把数字信号初始化部分的波形分离出去。当我们着重分析动态变化的部分时,就不需要加载初始化部分的波形。Verdi在绘制模拟波形的时候,只会看到小动态范围的数值,绘制出来的变化趋势就足够清楚了。

$fsdbDumpfile("tb_000.fsdb");

$fsdbDumpvars(0, tb);

@(posedge some_trigger_signal);

$fsdbSwitchDumpfile("tb_001.fsdb");

14、自动调节:加载特定时间范围

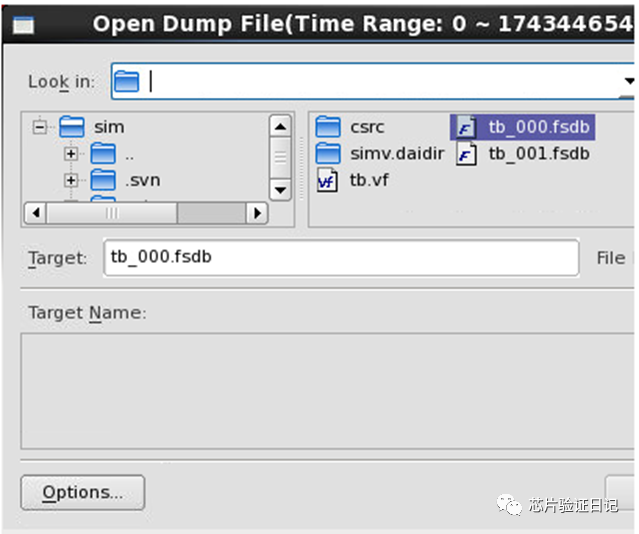

当然作为团队项目的螺丝钉,有时候不方便控制FSDB 文件的产生方式,那么在加载FSDB 文件的时候,可以选择指定一个时间范围。感谢读者 @Erik Li 提供的这个技巧。

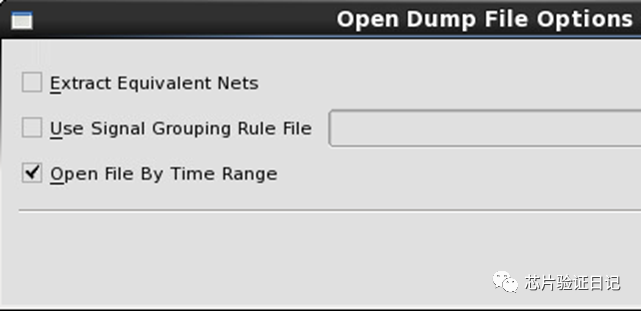

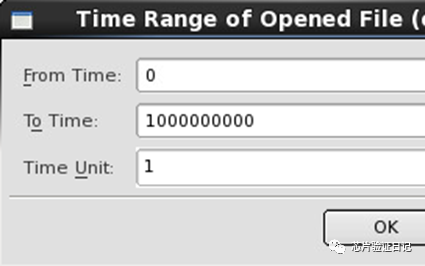

操作方式:nWave窗口菜单 - Open,选择 FSDB 文件到 Target Name 后,点击左下方的 Options... 按钮。

在弹出的对话框中选中 Open File By Time Range,然后点击 OK 按钮。

再点击 OK 按钮,在弹出的对话框中就可以选择感兴趣的时间起止范围了。

再分享一个最近才发现的 Verdi 调用参数。

verdi -preTitle "some text"

螺丝钉做久了,需要同时打开的 Verdi 窗口数量与日俱增。怎么从密密麻麻的任务栏图标中找到要找的那个,是个麻烦但不紧急的问题。除了贯彻断舍离、及时关闭短期内不需要的窗口之外,用上面的选项为每一个 Verdi 窗口做个简洁唯一的命名,也是一个不那么有效的解决之道。

15、跳转到指定行号

其实日常的频繁、快速地查看 Verilog 源代码,一般是在独立的文本编辑器中完成的。比如,VCS 编译产生的 log 文件中,对应的 Warning、Error 的后面会跟着相关源文件的路径、行号。如果用的编辑器是版本比较新的 Vim,那么简单的 gF 指令就可以迅速的从 log 文件跳转到对应源文件,而且光标会体贴的定位在出错行。如果是仍未默认支持的旧版 Vim,那么自己可以添加一个函数,可以参考这篇文章。

这种方式在门级仿真的场景中会不太灵光。因为门级网表通常都非常巨大,用 Vim 类的编辑器打开一次会非常缓慢,频繁跳转造成的等待就更难以接受了。

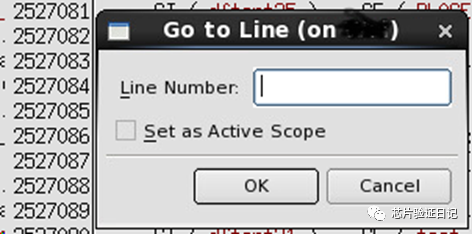

浏览门级网表诸如此类的超大文件,用 Verdi 是个不错的选择。在 Verdi 的 Source 窗口中,如何快速跳转到指定的行呢?

用鼠标拖动当然是种办法。但更快捷的是,在 Source 窗口下,按 g 键。会弹出一个小窗口,输入行号,点击确定即可。

16、源文件之间或不同逻辑层次的切换

有时候在 Verdi 中需要频繁的在两个 Verilog module 之间做切换,做一些对比的工作。如果这两个 module 所处的层次距离比较远,那么快捷的切换就显得特别重要了。这里介绍两个小技巧。

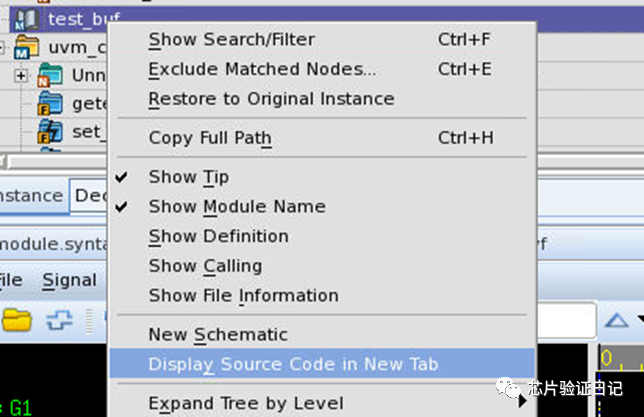

第一个是利用 Verdi 支持多 Source Tab 的功能。在两个不同的 Source Tab 中分别打开不同的 module,通过鼠标切换 Source Tab 来实现源文件或者逻辑层次的切换。

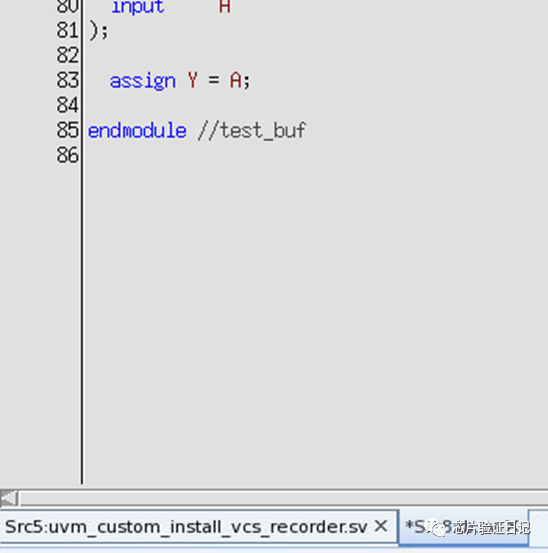

打开新的 Source Tab 的比较方便的方法是,在感兴趣的 Instance 上点击右键,然后在右键菜单上点击 Display Source Code in New Tab.

效果类似下图:

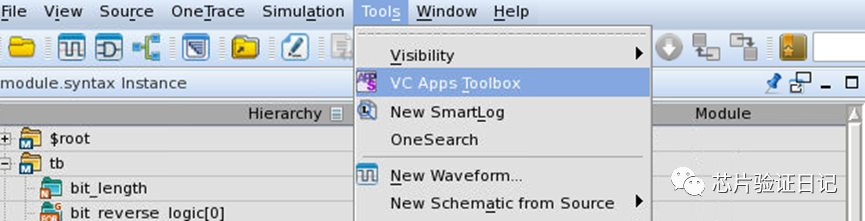

第二个技巧是利用 VC Apps 中的Find Instance with Module Def Name。

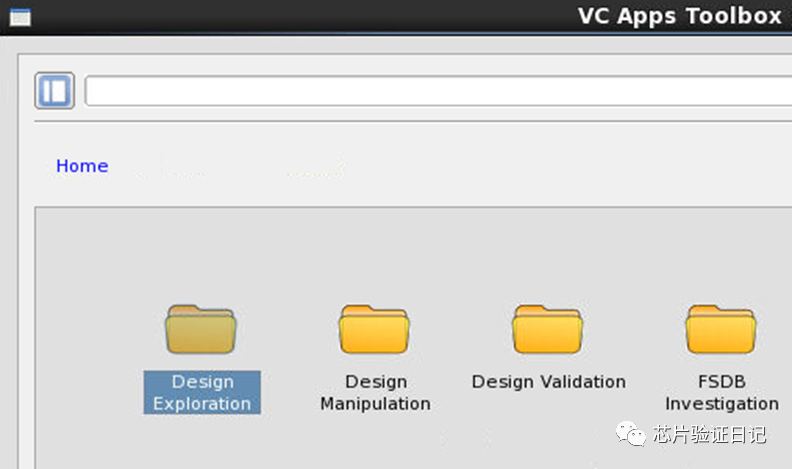

首先打开 Tools 菜单中的 VC Apps Toolbox。

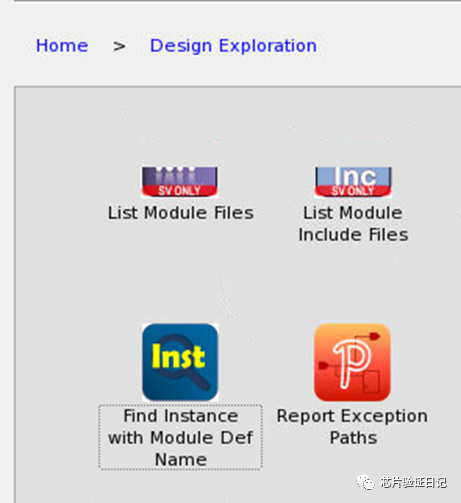

在 Design Exploration 目录中找到上述名字的 App,然后双击执行。

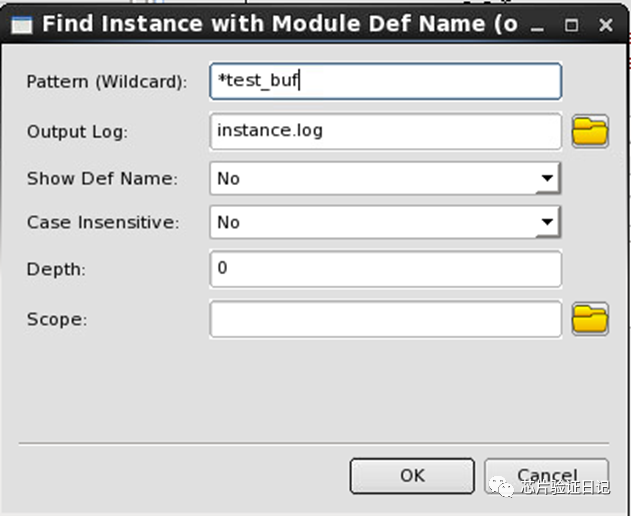

在出现的对话框中输入感兴趣的 module 名字,支持通配符。然后点击确定。

在 Verdi 下部的调试窗口中会出现一个新的大概叫做 SmartLog 的页面,其中列出了按照 module 名字搜索出来的所有 Instance。单击某个 Instance,Source 页面就会跳转到对应的地方。

重复执行上述过程,但搜索不同的 module name,会形成独立的 SmartLog 页面。这样通过切换 SmartLog 页面,也可以很方便的在多个设计中切换。

17、计数

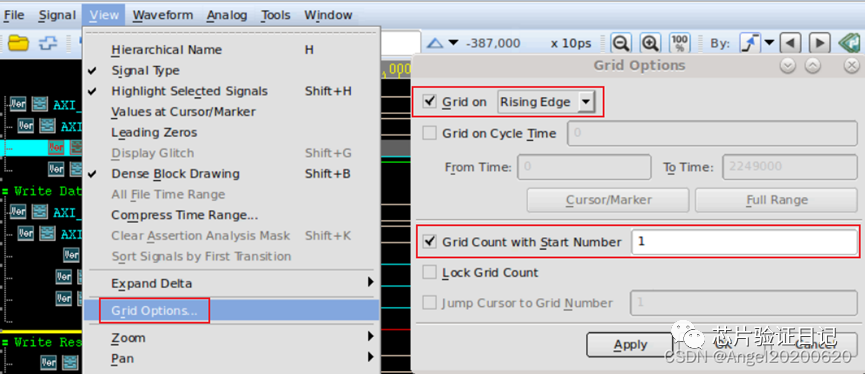

[1] Grid Options网格计数

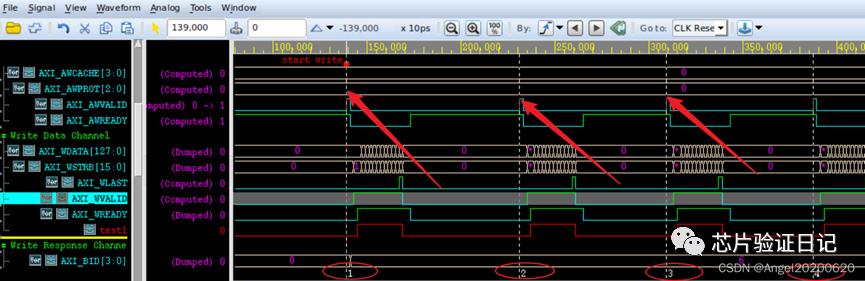

可以指定在波形窗中绘制网格线。选项包括Rising Edge, Falling Edge和 Both Edges。View -> Grid Options 选中Grid on勾选 Grid Count with Start Number,默认是0,也可以按需设置

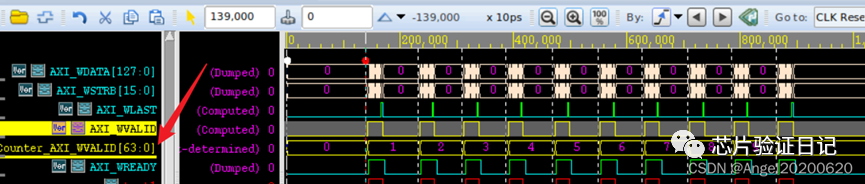

如图,以AXI_AWVALID上升沿为例,网格线下方出现了计数,用于统计上升沿个数。

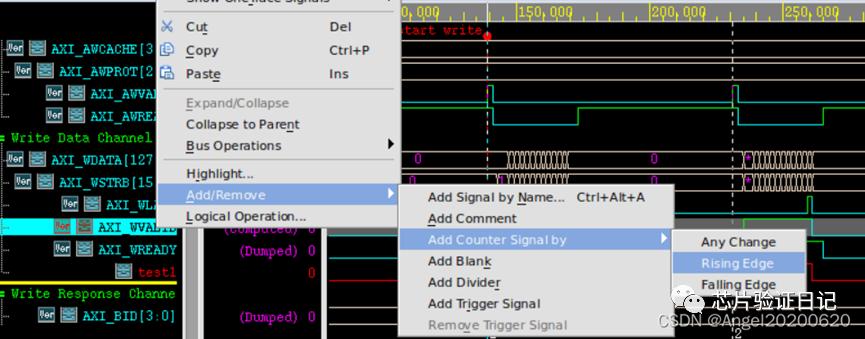

[2] 自动计数

右击AXI_WVALID信号,选择Add Counter Signal by,选择上升沿、下降沿、任意沿中的一个。

选择AXI_WVALID信号的上升沿为例子,波形中自动添加一个counter用于统计。

[3] 还有个fsdb转文本的功能:fsdbreport

18 用verdi打开覆盖率文件查看覆盖率

打开一个verdi——>tools——>coverage;在新打开的界面中选择——>file——>open/add database——>选择相应的.vdb文件——>more options——打开cov.hier文件

注:覆盖率文件为.vdb文件;.hier文件为对应工程目录的层级结构文件,对整理覆盖率有帮助

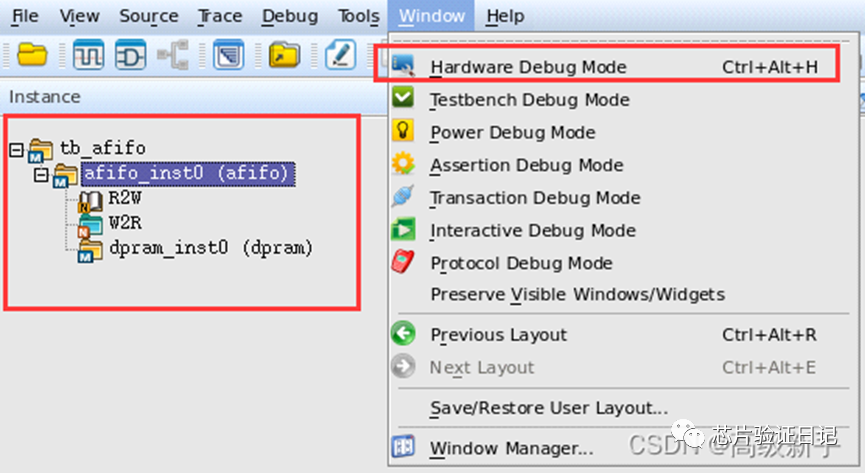

19 查看包含的设计架构

-

Verdi连续波激光器-Coherent2023-06-30 1242

-

Verdi环境配置、生成波形的方法2023-05-29 9342

-

全网最实用的Verdi教程12023-05-05 22927

-

Verdi使用技巧(三)2023-04-25 7897

-

分享《verdi用法小结》的pdf2023-02-18 2119

-

VCS+Verdi如何安装?怎么破解?2021-06-21 7679

-

如何通过自动化脚本实现Questasim和Verdi的联合仿真2021-06-13 6813

-

vcs和verdi的调试及联合仿真案例2020-09-22 10091

-

Verdi使用技巧 连续有效信号量测方法2019-05-15 11225

-

verdi-SP2软件下载2018-04-19 993

-

请教VCS和verdi怎么联合使用2015-01-22 8233

-

Verdi 54v7 LINUX2006-03-25 1706

全部0条评论

快来发表一下你的评论吧 !