解析什么是DFT友好的功能ECO?

电子说

描述

DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。DFT不友好的ECO会对芯片的测试和调试带来很大的困难,可能导致芯片测试效率降低甚至无法测试。

因此,在进行功能性ECO时,需要特别注意DFT功能的保护。一般来说,可以将DFT逻辑设置为非活动模式,以防止任何功能性更改对其产生影响。但是,在进行ECO时需要特别注意,涉及DFT路径的ECO是否会对DFT逻辑产生影响。如果ECO涉及DFT路径,可能需要重新评估ECO的影响,以确保DFT逻辑不受影响。

此外,DFT友好的ECO应确保扫描链完整,时钟和复位信号可控。这是为了确保芯片在测试和调试过程中可以正确地工作。因此,在进行ECO时,需要注意这些方面的设计和实现。如果一个功能ECO破坏了DFT功能或降低了DFT覆盖率,则称其为DFT不友好的ECO。而DFT友好的ECO应确保DFT功能不受影响,扫描链完整,时钟和复位信号可控。

一、在相邻寄存器中插入ECO

其中一个例子是在部分扫描链中在相邻寄存器上执行ECO插入,例如从A_REG到D_REG所示的链路,其中B_REG和C_REG形成相邻路径。在这种情况下,ECO之前, C_REG可以是非扫描寄存器, 而DFT是完好的。

如果ECO在从A_REG到D_REG的扫描链中的B_REG和C_REG之间插入组合逻辑,并且C_REG是非扫描寄存器,则扫描链将被打破,如图 2 所示。Conformal ECO会通过在此类ECO中直接插入后续路径中的逻辑,而不考虑保持扫描链的需要,从而破坏DFT。

图2

为了解决ECO引起的扫描链断裂问题,GOF的解决方案涉及将C_REG的类型从非扫描寄存器更改为扫描寄存器,并根据图 3 所示的方式正确连接扫描链。

图3

图3

二、选择适合的DFT信号

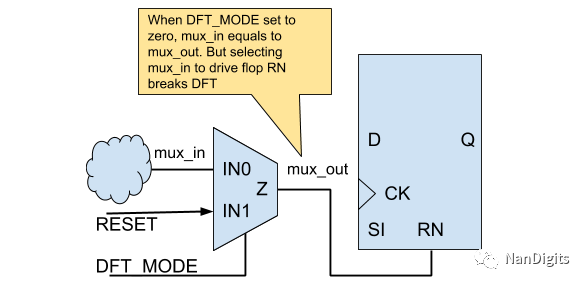

为确保在功能ECO期间DFT逻辑保持不活动状态,需要将DFT_MODE信号设置为零。然而,有些信号可能是等效的,但不适合用于DFT,这可能会导致DFT失效。例如,在图 4 中,一个ECO必须选择mux_in或mux_out信号来驱动寄存器的复位引脚。虽然这两个信号是等效的,但是Conformal ECO选择了mux_in,这破坏了DFT。相比之下,GOF可以识别MUX并选择mux_out作为复位引脚的正确信号,从而保持DFT逻辑的完整性。

图4

三、可重置和可设置型寄存器交换

在执行功能性网表 ECO 时,常常需要在可重置和可设置型寄存器之间进行交换。这个操作被认为是一种简单和直接的方式,只需交换相同的寄存器实例。然而,在图 5 中,Cadence Conformal 引入了一种冗余的方法,使用了一个新的可设置型寄存器 reg1_1,而不是直接将原始的寄存器转换为可设置型。新的寄存器 reg1_1 驱动原始的功能电路,而旧的寄存器 reg1 驱动扫描链扇出 reg2。这种方法存在两个主要问题。首先,新的寄存器 reg1_1 没有包含在扫描链中。在存在许多这样的重置/设置型寄存器交换的情况下(约占所有寄存器数量的 0.2%),将会导致 ATPG at-speed覆盖率约 0.2% 的损失。其次,Conformal LEC 未将新的寄存器 reg1_1 视为寄存器 reg1 的等效关键点,在 ECO 后的等效性报告中会出现大量的非等效点。

图5

图 6 所示的ECO中,GOF采用了一种直接的方法,将寄存器类型从可复位更改为可设置,从而保留了扫描链并确保DFT覆盖率不受影响。

图6

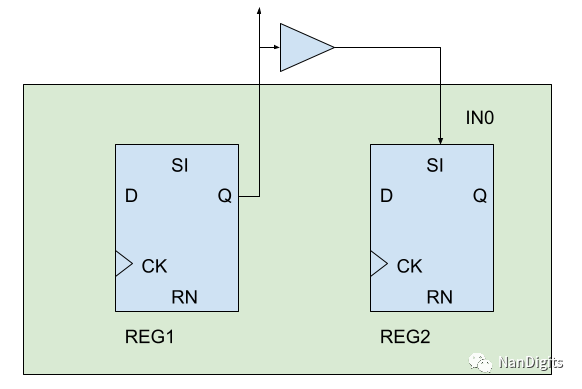

Cadence Conformal ECO中常见的一个错误是 "Error: Duplicate fanout branch # for net 'IN#'"。

这个问题通常出现在一个场景中,其中一个寄存器(REG1)的Q输出连接到父级,而相同的输出也连接到另一个寄存器(REG2)的扫描输入(SI)引脚。当对REG1执行ECO(例如将其类型更改为可设置寄存器)时,可能会导致Conformal ECO出现错误,从而可能导致工具停止操作。

图7

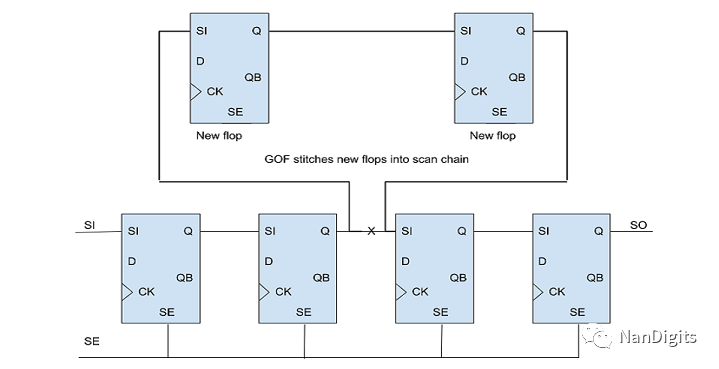

四、将新的寄存器插入扫描链中

ECO中插入的新寄存器应该被缝合到现有的扫描链中,以避免DFT覆盖率的损失。从工业数据来看,在具有100K个寄存器的设计中,100个新的非扫描寄存器可能会导致超过0.1%的DFT覆盖率损失。对于像汽车IC这样的高可靠性芯片,DFT覆盖率的损失是不可接受的。因此,如果在功能ECO中有新的寄存器,则应重新设计扫描链以包括新的寄存器。

图8

GOF提供了几种将新寄存器插入扫描链的方法。可以使用API "stitch_scan_chain" 自动缝合扫描链来插入新寄存器。还可以通过使用多个网表处理API来手动执行。

4.1 自动模式将寄存器插入本地模块的扫描链中

可以使用自动方法将寄存器集成到本地模块的扫描链中。在以下示例脚本中,假设'fix_design'命令添加了名为'state_new_reg_0'到'state_new_reg_7'的8个新寄存器。要将这些寄存器集成到本地模块的扫描链中,请执行以下步骤:

# API stitch_scan_chain without any argument to insert new flops in the local modules

stitch_scan_chain();

4.2 自动模式在一个寄存器之前插入新的寄存器

GOF提供了一种自动方法,可以在指定寄存器实例之前插入新的寄存器。用户可以标识一个寄存器实例的名称,然后GOF将在该实例之前将所有新寄存器插入到扫描链中。

例如,假设需要将所有新寄存器插入到名称为'u_pixel_ctrl/pulse_reg'的寄存器实例之前,请执行以下步骤:

# API stitch_scan_chain with -to option

stitch_scan_chain('-to', 'u_pixel_ctrl/pulse_reg');

4.3 手动模式连接所有新寄存器

扫描链可以通过ECO APIs手动重新连接,并且可以创建新的扫描输入/输出端口。

# GofCall ECO script, run_manual_stitch_scan_chain_example.pl

use strict;

undo_eco; # Discard previous ECO operations

setup_eco("eco_manual_stitch_scan_chain_example");# Setup ECO name

read_library("art.5nm.lib"); # 读lib库

read_svf("-ref", "reference.svf.txt"); # 可选读入svf

read_svf("-imp", "implementation.svf.txt"); # 可选读入svf

read_design("-ref", "reference.gv"); # 读参考网表

read_design("-imp", "implementation.gv"); # 读实现网表,ECO目标

set_top("topmod"); # 设置顶层名字

set_ignore_output("scan_out*");

set_pin_constant("scan_enable", 0);

set_pin_constant("scan_mode", 0);

fix_design;

save_session("current_eco_name"); # Save a session for future restoration

set_error_out(0); # Don't exit if finds error

my @flops = get_cells("-hier", "-nonscan"); # Find all new flops that are not in scan chain yet

# @flops can be defined by reading a list file

if(scalar(@flops)){ # If there are new flops, start the work

new_port("so1", "-output"); # New a scan out port so1

new_port("si1", "-input"); # New a scan in port si1

my $cnt = 0;

my $now_si;

foreach my $flop (@flops){

$cnt++;

if(is_scan_flop($flop)==0){

my $flop_name = get_ref($flop);

my $scanflop = get_scan_flop($flop_name); # If the flop is not scan type, change to scan type flop

change_gate($flop, $scanflop);

}

if($cnt==1){

change_port("so1", "$flop/Q"); # The first flop drives the new scan out port

}else{

change_pin($now_si, "$flop/Q");

}

$now_si = "$flop/SI";

change_pin("$flop/SE", "te"); # All scan enable pin is connected to scan enable signal

}

change_pin($now_si, "si1"); # The last flop has the new scan in port driving SI pin

}

write_verilog("eco_verilog.v");# Write out ECO result in Verilog

exit;

五、结论

总之,DFT友好的ECO是电子设计自动化(EDA)流程中非常理想的解决方案,因为它比传统方法提供了多种好处。其中最显著的优点之一是能够确保生成的设计是DFT友好的,这简化了测试和验证过程。在现代复杂集成电路的时代,确保DFT兼容性对于有效和可靠的测试至关重要。

DFT友好的ECO的一个关键特征是它能够在优化改变设计功能的情况下不影响可测试性。这是通过考虑设计的特定DFT要求的先进算法和方法实现的。相比之下,传统的EDA流程可能不会为DFT进行优化,从而导致测试和验证方面的重大挑战。

此外,使用DFT友好的ECO可以在市场上提供竞争优势。这是因为它可以实现更快的上市时间,减少设计迭代,并提高整体产品质量。相比之下,没有使用DFT友好方法的竞争对手可能难以实现类似的结果,导致延迟、成本增加和产品竞争力降低。

总的来说,DFT友好的ECO是现代EDA流程的一种非常有效的解决方案,比传统方法提供了重要的优势。它优化设计以实现DFT兼容性,可以实现更快的上市时间、减少设计迭代并提高产品质量,从而在市场上提供竞争优势。

-

DFT在信号处理中的应用 DFT与FFT的区别2024-12-20 4761

-

时序(Timing)对功能ECO有多重要2023-07-05 2874

-

Lightelligence使用Cadence Xcelium多核加速DFT仿真2023-04-20 2788

-

一种快速DFT DRC检查的功能介绍2023-03-06 3041

-

NanDigits GOF提供一种快速DFT DRC检查的功能2023-02-22 1586

-

一个典型设计的DFT组件2022-11-30 1711

-

详解Xilinx FPGA的ECO功能2022-08-02 5401

-

请问DFT是什么原理?2021-06-17 1671

-

DFT基本原理解析2020-07-06 10706

-

如何在Vivado中执行工程变更命令 (ECO)2018-11-21 5912

-

V6 FPGA可以ECO功能吗?2018-11-13 1970

-

汽车eco模式使用技巧_eco模式真能省油吗2017-12-14 30264

-

什么是DFT,DFT是什么意思2010-06-07 31688

全部0条评论

快来发表一下你的评论吧 !