AMBA4 SystemVerilog Asseration验证

描述

ARM所推出的AMBA4总线相对来讲还是应用广泛的。无论是芯片设计里还是FPGA设计里,时常能见到AMBA4总线的身影。在验证领域,SystemVerilog Asseration还是一个很常见的验证手段。在Xilinx Vivado中有提供AMBA总线相关的Checker VIP,其内部也是采用的SystemVerilog Asseration来实现。今天给大家推荐下ARM自家所推出的BP063 AMBA4 SVA组件。

》使用

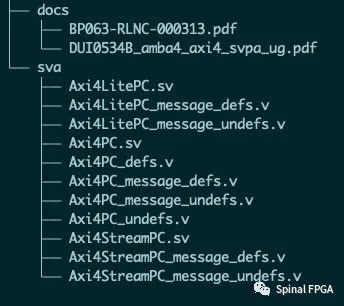

下载下来后文件夹里包含了sva文件和docs资料:

详细的使用教程可以参照文件夹里面的BP063-RLNC-000313.pdf,这里就不在照本宣科的给从头到尾讲了,文档中已详细说明了如何使用及各种参数的配置。

》One More Thing

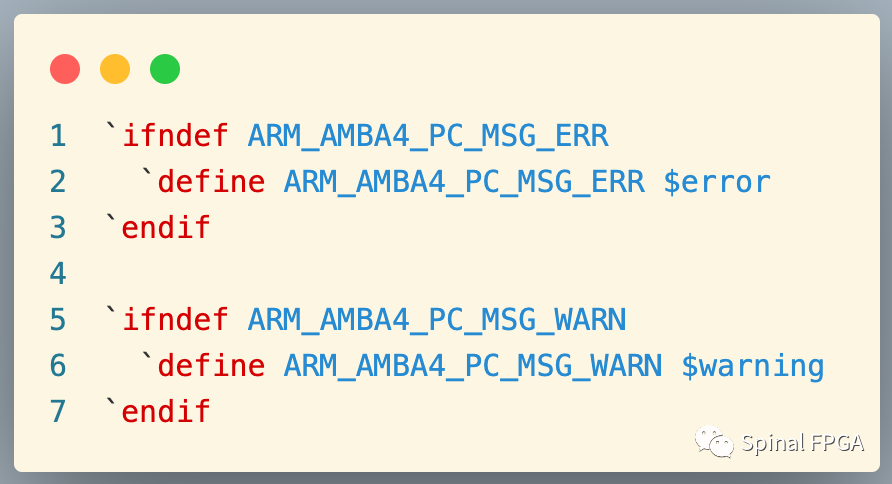

参照文档基本可以保证能够正常使用。对于SVA而言,其本质无非是通过各种规则进行检查,若不符合情况则根据错误等级进行报错。在ARM AMBA4 SVA里面,出错后的错误等级分为了$error和$warning两种:

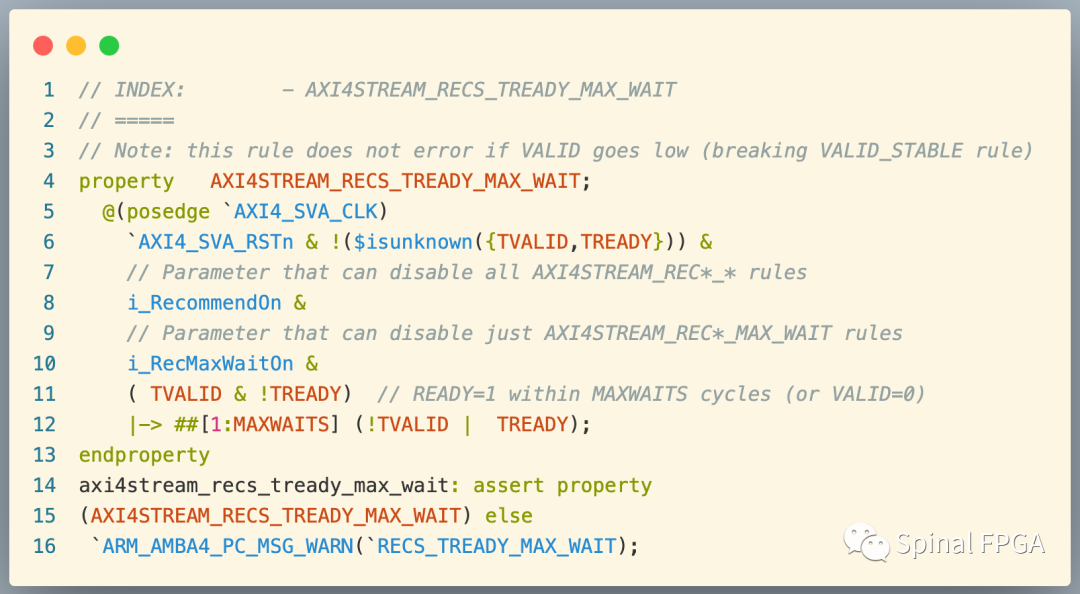

在仿真器执行时,对于$warning其只是打印信息,并不会影响仿真器继续向下执行。如果对于一些规则检测,如果你觉得使用$warning并不符合需要,则可以手动对源代码进行修改。例如下面对于ready超时的检测:

这里当仿真时不符合设计预期时会通过`ARM_AMBA4_PC_MSG_WARN来进行$warning报警,如果需要出错时仿真立即停下来那么则可以将其替换更改为`ARM_AMBA4_PC_MSG_ERR。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SystemVerilog 的VMM验证方法学教程教材2012-01-11 59847

-

什么是AMBA APB4与AMBA3 AHB-Lite1.0协议2021-04-02 2301

-

在Arm AMBA协议集中AHB-lite可否使用2022-09-08 3381

-

AMBA 4 ACE和ACE Lite协议校验器用户指南2023-08-10 814

-

分层验证法在基于AMBA系统中的应用2009-03-28 1101

-

基于SystemVerilog语言的验证方法学介绍2011-05-09 1105

-

Cadence验证IP为ARM AMBA 4协议大幅缩短验证周转时间2012-11-07 1445

-

SystemVerilog的正式验证和混合验证2021-03-29 954

-

4-AMBA VIP 编程接口2021-12-08 973

-

利用Systemverilog+UVM搭建soc验证环境2022-08-08 1280

-

IEEE SystemVerilog标准:统一的硬件设计规范和验证语言2022-08-25 790

-

验证必备:AMBA4 SystemVerilog Asseration2023-05-24 1244

-

如何验证AMBA系统级环境2023-05-29 1677

-

AMBA4—无聊的Narrow transfers介绍2023-06-11 2034

-

AMBA4—“无聊的”Narrow transfers2023-06-30 1385

全部0条评论

快来发表一下你的评论吧 !