圆片级芯片尺寸封装工艺流程与技术

制造/封装

描述

圆片级芯片尺寸封装(WLCSP)是指在圆片状态下完成再布线,凸点下金属和焊锡球的制备,以及圆片级的探针测试,然后再将圆片进行背面研磨减薄,最终切割形成单颗芯片的一种封装形式。该种封装的最终的封装尺寸与芯片的尺寸相同,通过芯片表面的焊锡球凸点与 PCB 形成连接。

圆片级芯片尺寸封装源自于倒装芯片技术。20世纪60年代,美国 IBM 公司首先研发了可控塌陷芯片连接(C4)技术;20世纪90年代,-些拥有圆片凸块技术的公司研发了圆片级芯片尺寸封装技术。

圆片级芯片尺寸封装的主要优势是轻、薄、短、小,主要用于手机等便携产品中,包括电源管理器件(PMIC)、集成无源组件(ID)、电可擦可编程只读存储器(EEPROM)、射频前端 (RF Front End) 等。

由于需要将 WICSP 直按组装到 PCB 上,受制于 PCB 技术及表面贴装工艺能力,目前 WLCSP 的焊球节距较大,通常为 0. 5mm 或 0.4mom。由于硅芯片与PCB 的热膨胩系数不同,较大的芯片尺寸会因存在较大的热应力而导致焊锡球的热疲劳失效,所以 WICSP 的封装尺寸通常都小于 6mmx6mm。

按照芯片10端子铝垫位置与焊锡球相对位置的差异,WLCSP 可分为 BoP-WICSP ( Bump on Pad- WLCSP)和 RDL-WICSP ( Redistribution Laver- WICSP)两类。如果芯片表面的I/0端子已经按照最终封装焊球的位置进行阵列排布,这样可以直接在铝垫的上方生长 UBM (Under Bump Metalization)并放置焊球;如果芯片上的I/0 端子铝垫不是阵列分布,或者其位置与最终焊球的位置不同,需要通过再布线对I/0端子的位置进行再分布。

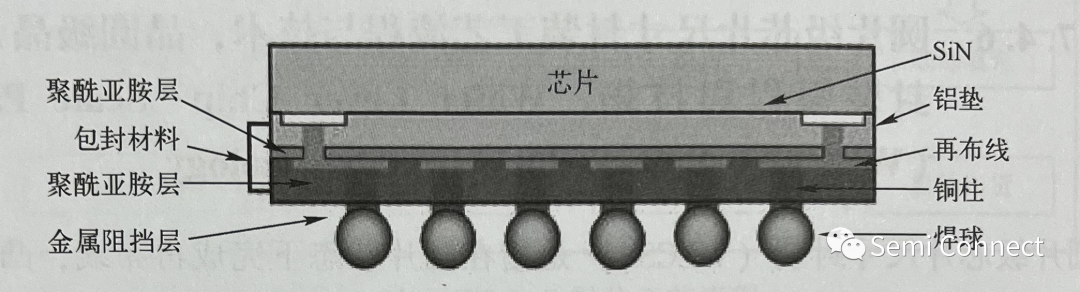

市场上也有一种特殊的 WLCSP 结构,其商业名称为 Super CSP。与上述WICSP 不同,其凸点下金属层为厚的铜柱 (Cu Metal Post),且铜柱被包封材料包覆,如下图所示。

在 BOP-WICSP 和 RDL-WLCSP 中,为了缓解焊球凸点和再布线层对芯片产生的应力,会在芯片表面和再布线层表面涂覆一层高分子薄膜材料,该层高分子薄膜材料层称为再钝化层(Repassivation Layer)。目前,业界主要使用的再钝化层材料有聚酰亚胺(Polymide, FI)、聚苯并咪唑 (Polybenzoxazole, PBO)和苯并环丁烯 (Benzocyclobutene, BCB)。

目前再布线层主要采用两种材料,一种是采用腐蚀方法加工的铝再布线层,另一种是采用电镀方式形成的铜再布线层。通常,铝再布线层的金属厚度为1~4um;采用电镀铜工艺的再布线层厚度可以达到 10um,其对电流的承载能力强于铝再布线层,因此对于需要承载大电流的电源管理类器件,通常会选用电镀铜再布线工艺。

凸点下金属层是连接焊锡凸点与芯片最终金属层(铝垫或再布线层)的中间层,需要在芯片与凸点之间形成良好的电气连接。凸点下金属层需要包含界面扩散阻挡层和与焊锡凸点的反 应润湿层。凸点下金属层通常采用溅射或溅射加电镀的方式来制备,材料组合有 Ti(SP) /Cu(SP)/Cu (PL)、TW (SP)/Cu(SP)/Cu(PL)、Ti(SP)/Cu (SP)/Ni(PL) 、Ti( SP)/NiV ( SP)、CI ( SP )/NiY(SP)等(说明:括号内标示usp,代表溅射,“PL”代表电镀)。在某些产品中,也会采用化学镀镍金作为凸点下金属层。

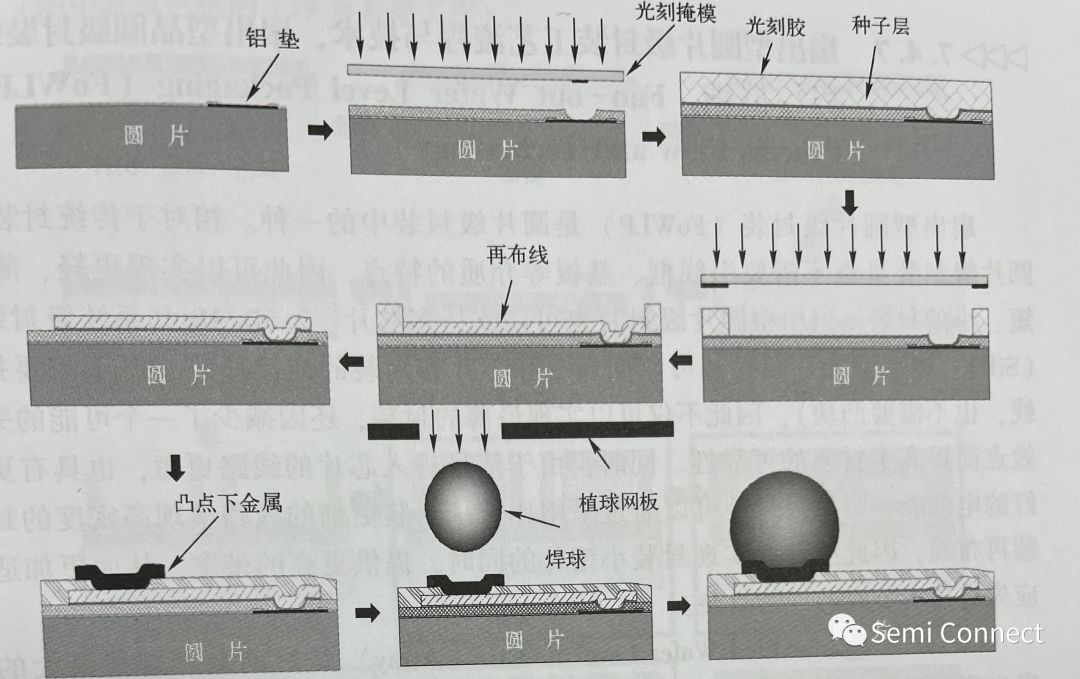

下图所示为典型的 RDL-WICSP 前道凸点工艺流程。

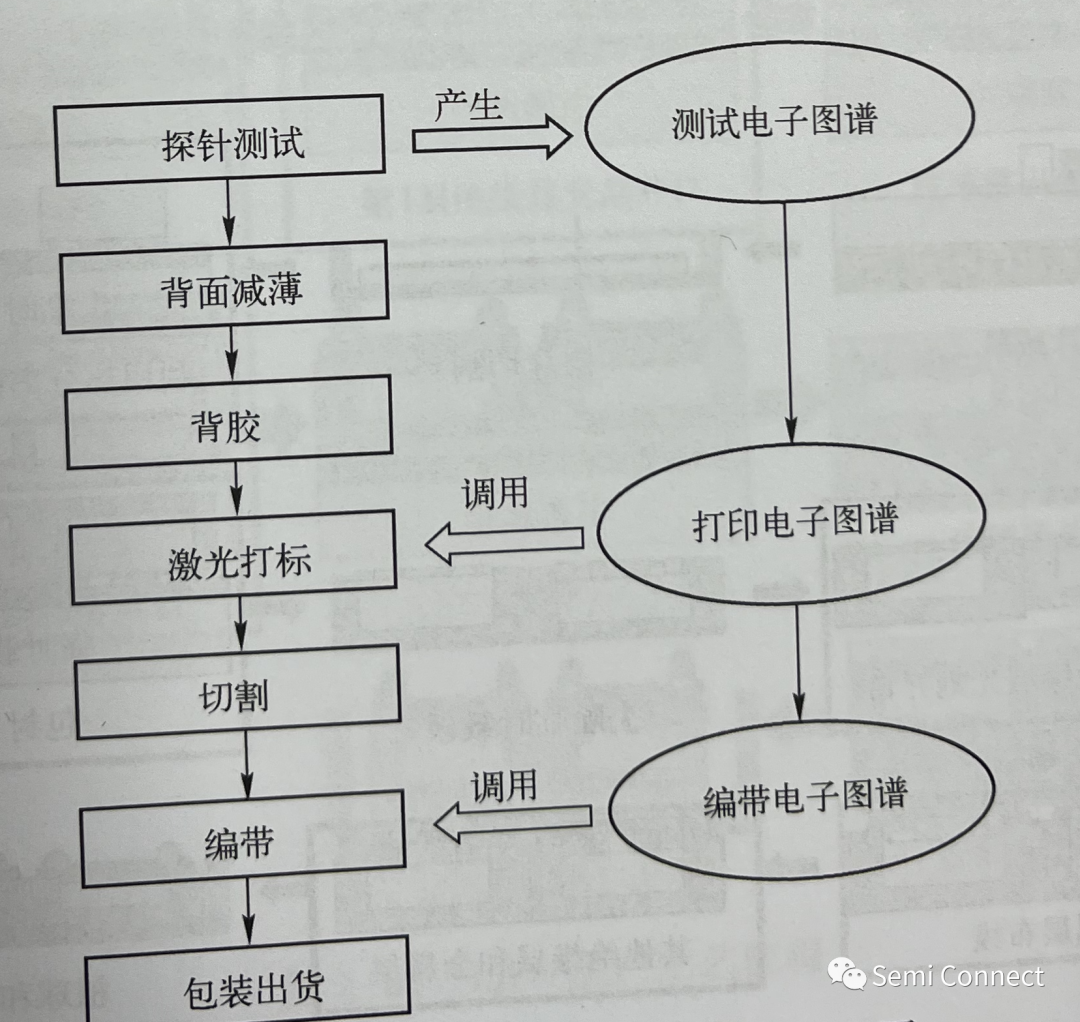

完成凸点工艺后,还要进行后段封装工艺,主要包合圆片探针测试、圆片减薄、切割和编带等,如下图所示。

审核编辑:刘清

-

ic封装工艺流程2010-07-18 3599

-

扇出型晶圆级封装技术的工艺流程2025-05-14 3100

-

扇出型圆片级封装工艺流程与技术2023-05-08 3601

-

【转帖】一文读懂BGA封装技术的特点和工艺2018-09-18 2520

-

倒装晶片的组装工艺流程2018-11-23 4929

-

晶圆级芯片封装有什么优点?2019-09-18 5708

-

倒装芯片的特点和工艺流程2020-07-06 14377

-

晶圆封装有哪些优缺点?2021-02-23 6774

-

芯片封装工艺流程-芯片封装工艺流程图2008-05-26 8622

-

集成电路芯片封装工艺流程2021-07-28 14216

-

芯片封装工艺流程是什么2021-08-09 73397

-

芯片封装工艺流程讲解2022-10-31 13000

-

封装工艺流程--芯片互连技术2022-12-05 2482

-

晶圆级芯片尺寸封装-AN104392023-03-03 574

-

详解不同晶圆级封装的工艺流程2024-08-21 4960

全部0条评论

快来发表一下你的评论吧 !