简述集成电路的工作原理

电子说

描述

什么是集成电路

集成电路,英文为IntegratedCircuit,缩写为IC;顾名思义,就是把一定数量的常用电子元件,如电阻、电容、晶体管等,以及这些元件之间的连线,通过半导体工艺集成在一起的具有特定功能的电路。

集成电路的分类

功能结构

集成电路,又称为IC,按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/模混合集成电路三大类。

模拟集成电路又称线性电路,用来产生、放大和处理各种模拟信号(指幅度随时间变化的信号。例如半导体收音机的音频信号、录放机的磁带信号等),其输入信号和输出信号成比例关系。

而数字集成电路用来产生、放大和处理各种数字信号(指在时间上和幅度上离散取值的信号。例如3G手机、数码相机、电脑CPU、数字电视的逻辑控制和重放的音频信号和视频信号)。

制作工艺

集成电路按制作工艺可分为半导体集成电路和膜集成电路。

膜集成电路又分类厚膜集成电路和薄膜集成电路。

集成度高低

集成电路按集成度高低的不同可分为:

- SSIC小规模集成电路(SmallScaleIntegratedcircuits)

- MSIC中规模集成电路(MediumScaleIntegratedcircuits)

- LSIC大规模集成电路(LargeScaleIntegratedcircuits)

- VLSIC超大规模集成电路(VeryLargeScaleIntegratedcircuits)

- ULSIC特大规模集成电路(UltraLargeScaleIntegratedcircuits)

- GSIC巨大规模集成电路也被称作极大规模集成电路或超特大规模集成电路(GigaScaleIntegration)。

导电类型不同

集成电路按导电类型可分为双极型集成电路和单极型集成电路,他们都是数字集成电路。

双极型集成电路的制作工艺复杂,功耗较大,代表集成电路有TTL、ECL、HTL、LST-TL、STTL等类型。单极型集成电路的制作工艺简单,功耗也较低,易于制成大规模集成电路,代表集成电路有CMOS、NMOS、PMOS等类型。

按用途

集成电路按用途可分为电视机用集成电路、音响用集成电路、影碟机用集成电路、录像机用集成电路、电脑(微机)用集成电路、电子琴用集成电路、通信用集成电路、照相机用集成电路、遥控集成电路、语言集成电路、报警器用集成电路及各种专用集成电路。

按应用领域

集成电路按应用领域可分为标准通用集成电路和专用集成电路。

按外形

集成电路按外形可分为圆形(金属外壳晶体管封装型,一般适合用于大功率)、扁平型(稳定性好,体积小)和双列直插型。

集成电路的结构和组成

集成电路(integratedcircuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。

一般的,我们用由上而下的层级来认识集成电路,这样便于理解,也更有条理些。

系统级

以手机为例,整个手机是一个复杂的电路系统,它可以打电话、可以玩游戏、可以听音乐、可以...... 它由多个芯片以及电阻、电感、电容相互连接而成,称为系统级。(当然,随着技术的发展,将一整个系统做在一个芯片上的技术也已经出现多年——SoC技术)

模块级

在整个系统中分为很多功能模块各司其职。有的管理电源,有的负责通信,有的负责显示,有的负责发声,有的负责统领全局的计算,等等。我们称为模块级。这里面每一个模块都是一个宏大的领域,都聚集着无数人类智慧的结晶,也养活了很多公司。

寄存器传输级(RTL)

那么每个模块都是由什么组成的呢?以占整个系统较大比例的数字电路模块(它专门负责进行逻辑运算,处理的电信号都是离散的0和1)为例。它是由寄存器和组合逻辑电路组成的。所谓寄存器就是一个能够暂时存储逻辑值的电路结构,它需要一个时钟信号来控制逻辑值存储的时间长短。

现实中,我们需要时钟来衡量时间长短,电路中也需要时钟信号来统筹安排。时钟信号是一个周期稳定的矩形波。现实中秒钟动一下是我们的一个基本时间尺度,电路中矩形波震荡一个周期是它们世界的一个时间尺度。电路元件们根据这个时间尺度相应地做出动作,履行义务。

组合逻辑呢,就是由很多“与(AND)、或(OR)、非(NOT)”逻辑门构成的组合。比如两个串联的灯泡,各带一个开关,只有两个开关都打开,灯才会亮,这叫做与逻辑。

一个复杂的功能模块正是由这许许多多的寄存器和组合逻辑组成的。把这一层级叫做寄存器传输级。

图中的三角形加一个圆圈是一个非门,旁边的器件是一个寄存器,D是输入,Q是输出,clk端输入时钟信号。

门级

寄存器传输级中的寄存器其实也是由与或非逻辑构成的,把它再细分为与、或、非逻辑,便到达了门级(它们就像一扇扇门一样,阻挡/允许电信号的进出,因而得名)。

晶体管级

无论是数字电路还是模拟电路,到最底层都是晶体管级了。所有的逻辑门(与、或、非、与非、或非、异或、同或等等)都是由一个个晶体管构成的。因此集成电路从宏观到微观,达到最底层,满眼望去其实全是晶体管以及连接它们的导线。

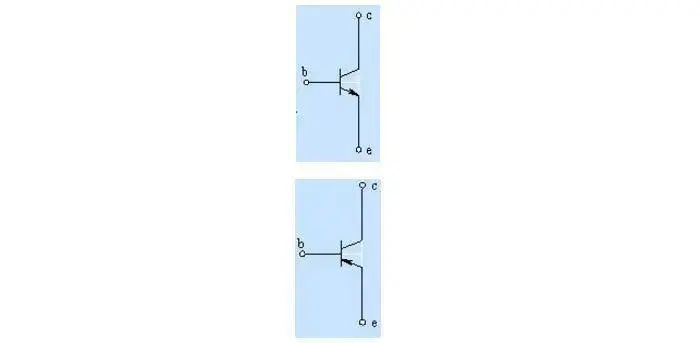

早期的时候双极性晶体管(BJT)用的比较多,俗称三极管。它连上电阻、电源、电容,本身就具有放大信号的作用。像堆积木一样,可以用它构成各种各样的电路,比如开关、电压/电流源电路、上面提到的逻辑门电路、滤波器、比较器、加法器甚至积分器等等。由BJT构建的电路我们称为TTL(Transistor-TransistorLogic)电路。BJT的电路符号长这个样子:

后来金属-氧化物半导体场效应晶体管(MOSFET)的出现,以优良的电学特性、超低的功耗横扫IC领域。除了模拟电路中BJT还有身影外,基本上现在的集成电路都是由MOS管组成的了。同样的,由它也可以搭起来成千上万种电路。而且它本身也可以经过适当连接用来作电阻、电容等基本电路元件。MOSFET的电路符号如下:

如上所述,在实际工业生产中,芯片的制造,实际上就是成千上万个晶体管的制造过程。现实中制造芯片的层级顺序就要反过来了,从最底层的晶体管开始一层层向上搭建。基本上,按照“晶体管-》芯片-》电路板”的顺序,我们最终可以得到电子产品的核心部件 —— 电路板。

集成电路的制造

首先我们知道,光刻的大致流程是,一个晶圆(wafer)(通常直径为300mm)上涂一层光刻胶,然后光线经过一个已经刻有电路图案(pattern)的掩膜版(maskorreticle)照射到晶圆上,晶圆上的光刻胶部分感光(对应有图案的部分),接着做后续的溶解光刻胶、蚀刻晶圆等处理。然后再涂一层光刻胶,重复上述步骤几十次,以达到所需要求。

简化结构请看下图。掩膜版和晶圆各自安装在一个运动平台上(reticlestageandwaferstage)。光刻时,两者运动到规定的位置,光源打开。光线通过掩膜版后,经过透镜,该透镜能够将电路图案缩小至原来的四分之一,然后投射到晶圆上,使光刻胶部分感光。

一块晶圆上有很多die,每一个die上都刻有相同的电路图案,即一块晶圆可以出产很多芯片。一个die典型的尺寸是26×32mm。

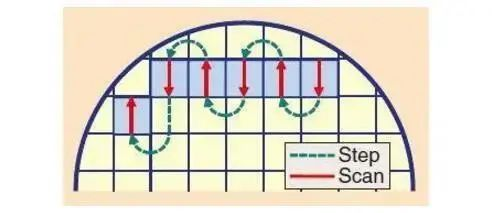

***主要有两种,一种叫做stepper,即掩膜版和晶圆上的某一个die运动到位后,光源开、闭,完成一次光刻,然后晶圆运动使得下一个die到位,再进行一次光刻,依此类推。

而另一种***叫做scanner,即光线被限制在一条缝的区域内,光刻时,掩膜版和晶圆同时运动,使光线以扫描的方式扫过一个die的区域,从而将电路图案刻在晶圆上(见下图(b))。

scanner比stepper的优势在于,可以提供更大的die的尺寸。其原因在于,对于一个固定尺寸的圆透镜,比如直径32mm的圆(指投射后的区域大小),其允许透过的光线的区域尺寸是受限的。

若采用stepper的step-and-expose方式进行光刻,一个die的区域必须能被包含在直径32mm的圆中,因此能获得的最大的die的尺寸为22×22mm;若采用scanner的step-and-scan方式,透镜能够提供的矩形区域长度可以到26mm(26×8mm)甚至更长,将光缝设置为这个尺寸,使用扫描的方式便可以获得26×Lmm的区域(L为扫描长度)。区域示意见下图(a)。同样的透镜在stepper下可以实现更大区域的意义在于,当你需要生产尺寸较大的芯片的时候,换一个更大的透镜的费用是昂贵的。

Scanner的step-and-scan过程的示意图如下:

为了使每层的电路相互之间不发生干涉,需要对上下平台进行精密运动控制。扫描时上下平台应处于匀速运动阶段。目前最小的层叠误差小于2nm(单个机器内)或3nm(不同机器间)。

光源的波长一般为365、248、193、157甚至13.5nm(EUV,ExtremeUltraviolet)。因为光刻过程受到衍射限制,光源波长越小,能够做出的芯片尺寸就越小。

在透镜和晶圆之间加入折射率大于1的液体(如水),可以减小光线波长,从而提高NA(数值孔径)和分辨率。这种***叫浸润式(immersion)***。

世界上做高端***的厂家主要有ASML、Nikon和Canon。佳能大概已经不行了。Nikon每年开个会叫做LithoVision。

集成电路的封装形式

SOP小外形封装

SOP,也可以叫做SOL和DFP,是一种很常见的元器件形式。同时也是表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L字形)。封装材料分塑料和陶瓷两种。始于70年代末期。

SOP封装的应用范围很广,除了用于存储器LSI外,还输入输出端子不超过10-40的领域里,SOP都是普及最广泛的表面贴装封装。后来,为了适应生产的需要,也逐渐派生出SOJ、SSOP、TSSOP、SOIC等一些小外形封装。

PGA插针网格阵列封装

PGA芯片封装形式常见于微处理器的封装,一般是将集成电路(IC)包装在瓷片内,瓷片的底部是排列成方形的插针,这些插针就可以插入或焊接到电路板上对应的插座中,非常适合于需要频繁插波的应用场合。对于同样管脚的芯片,PGA封装通常要比过去常见的双列直插封装需用面积更小。

PGA封装具有插拨操作更方便,可靠性高及可适应更高的频率的特点,早期的奔腾芯片、InTel系列CPU中的80486和Pentium、PentiumPro均采用这种封装形式。

BGA球栅阵列封装

BGA封装是从插PGA插针网格阵列改良而来,是一种将某个表面以格状排列的方式覆满引脚的封装法,在运作时即可将电子讯号从集成电路上传导至其所在的印刷电路板。在BGA封装下,在封装底部处引脚是由锡球所取代,这些锡球可以手动或透过自动化机器配置,并透过助焊剂将它们定位。

BGA封装能提供比其他如双列直插封装或四侧引脚扁平封装所容纳更多的接脚,整个装置的地步表面可作为接脚使用,比起周围限定的封装类型还能具有更短的平均导线长度,以具备更加的高速效能。

DIP双列直插式封装

所谓DIP双列直插式封装,是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路IC均采用这种封装形式,其引脚数一般不超过100个。采用DIP封装的CPU芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。

-

集成电路板的工作原理是什么2024-01-05 4434

-

浅析集成电路的工作原理2023-07-20 3507

-

集成电路的分类及工作原理讲解2021-12-08 8572

-

熟悉中规模集成电路数据选择器的工作原理和逻辑功能2021-07-29 4297

-

中国集成电路大全接口集成电路2020-12-10 1987

-

555集成电路的详细介绍和工作原理及的800例应用电子教材的详细概述2018-07-09 1949

-

一文解读集成电路的工作原理(集成电路的组成及封装形式)2018-03-04 51850

-

新编555集成电路机构与工作原理的应用800例2017-09-19 1539

-

CMOS集成电路的工作原理2016-08-16 1376

-

UCC3305集成电路工作原理与在HID灯中的应用2009-11-26 994

-

集成电路(IC)的检测常识2009-09-30 1426

-

音乐集成电路的结构及基本工作原理2009-09-19 8467

-

集成电路的检测常识2009-03-09 2095

-

555时基集成电路的工作原理与应用2006-04-16 4558

全部0条评论

快来发表一下你的评论吧 !