SPI通信总线简述

描述

Serial Peripheral Interface:是Motorola公司推出的三线同步接口,串行外围设备接口,是一种高速全双工的通信总线。它被广泛地使用在 ADC 等设备与 MCU 间,要求通讯速率较高的场合。

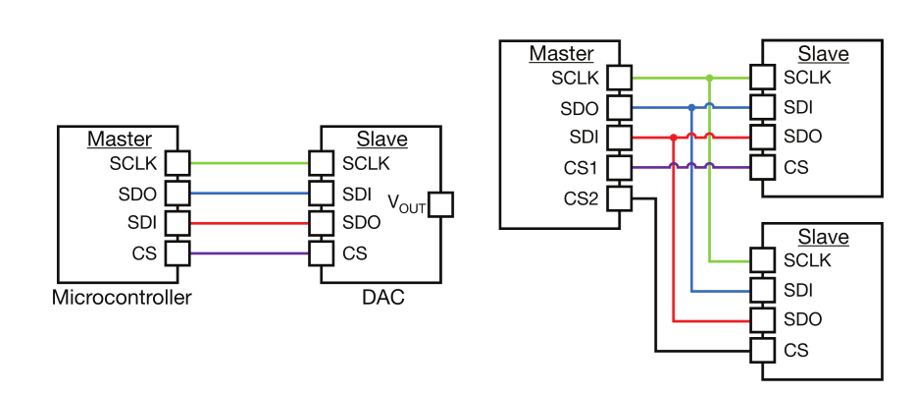

SPI 的硬件连接

1. 对于SPI主机总线上是可以挂1个或者多个从机设备。

2. 主机通过片选CS信号选择从机设备。

SPI的数据和控制线(CS 、SDO、SDI、SCLK)

1. CS(chip select)片选,又叫从选(slave select),用于选择从机设备,由主机来驱动,片选信号低,SPI开始通讯。

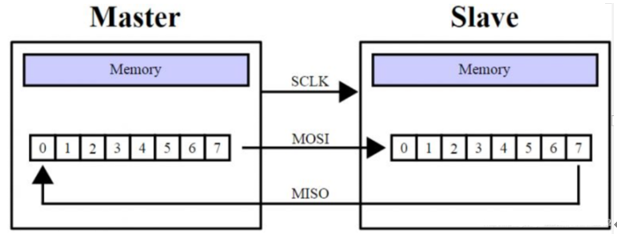

2. SDO/SDI(serial data out/serial data in),串行数据输入和串行数据输出数据线,用于传输数据。描述了主从系统之间的数据流关系的名称:MOSI(Master Out Slave In)=主输出从输入,对应SDI;MISO(Master In Slave Out .)=主输出从输出对应SDO。

3. SCLK (serial clock):串行时钟,由SPI主控驱动的方波。SPI总线上SDO和SDI上的数据相对于控制数据锁存的SCLK信号具有时序性。

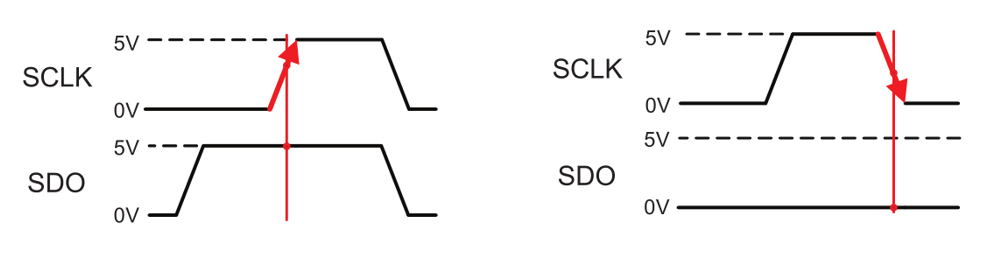

SPI数据锁存

1. SPI数据锁存于SCLK的上升沿或下降沿上。

2. 锁存于的边缘数据称为临界沿。

3. 下图说明了锁存逻辑1在上升沿上,逻辑0在下降沿上。

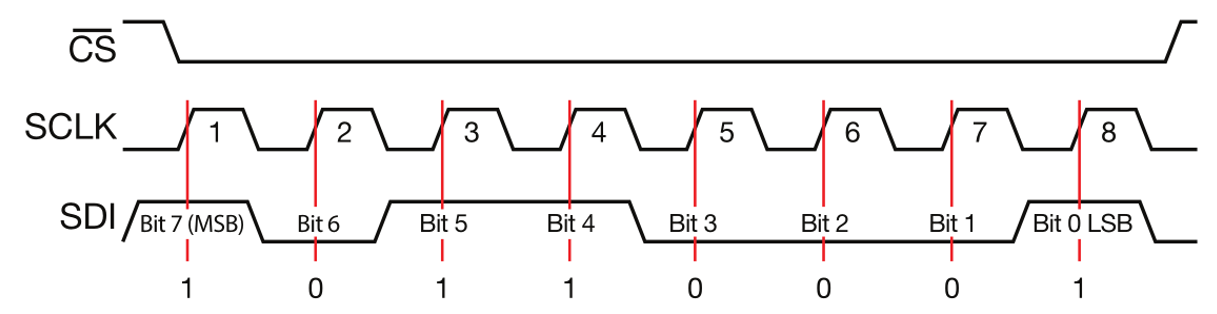

SPI读时序

1.上升沿锁存数据。

2.主机输出写入从设备(相对于从设备的SDI)。

3.主机拉低CS到0V,激活从设备SPI总线。

4.数据在SCLK的上升沿从MSB到LSB被锁存。

5.最终完成的SPI读取的数据是二进制1011001 。

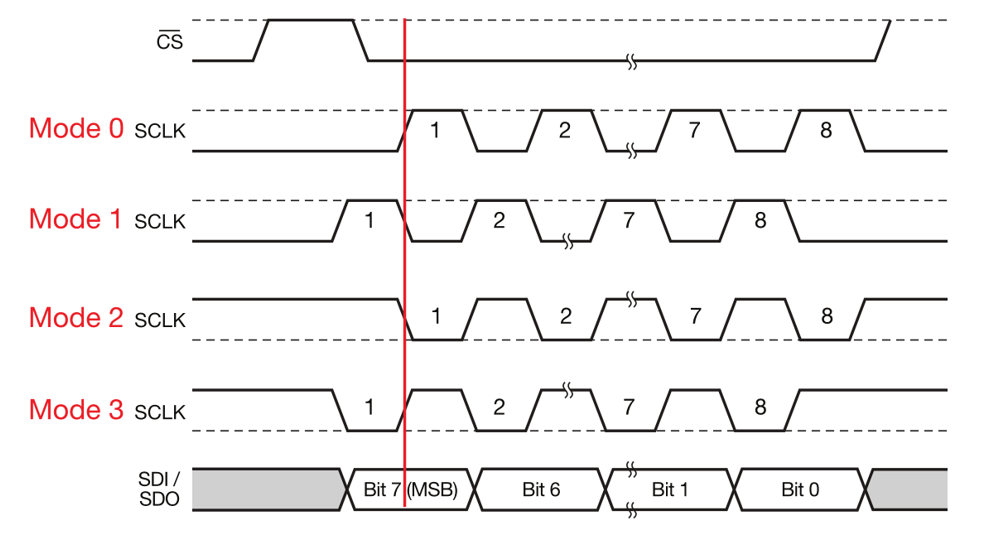

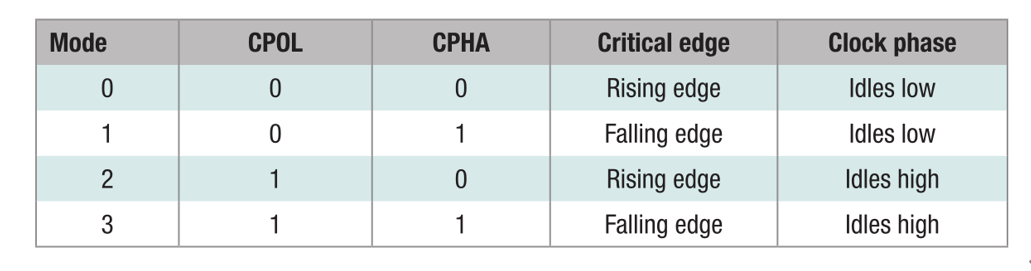

SPI模式

CPHA (clock phase)时钟相位:定义数据锁存在(SCLK)时钟的上升沿还是下降沿,0表示上升沿锁存,1表示下降沿锁存。

CPOL (clock polarity) 时钟极性:定义(SCLK)时钟在SPI帧之间是高空闲还是低空闲。CPOL = 0低空闲,CPOL = 1高空闲。

-

SPI通信总线概述和Verilog实现2025-02-07 2415

-

SPI总线的定义和特点2024-09-03 3192

-

SPI总线学习笔记2023-09-20 2098

-

浅谈SPI总线通信接口及其协议2023-03-22 3130

-

通信协议:SPI2021-12-22 1213

-

通俗理解STM32 SPI通信(主从双机SPI通信)2021-12-13 1466

-

SPI通信2021-11-24 1053

-

CAN总线简述2021-08-19 1902

-

基于SPI串行总线接口的Verilog实现2021-05-29 6200

-

IIC总线和SPI总线通信详解2020-12-23 4820

-

怎么使用FPGA实现SPI总线的通信接口?2019-08-09 4666

-

SPI通信总线的原理及工作过程简单分析2018-03-08 33123

-

简述spi与sci区别2017-11-08 13881

-

用SPI总线实现DSP和MCU之间的高速通信2009-11-27 1033

全部0条评论

快来发表一下你的评论吧 !