剖析振荡电路设计关键

电子说

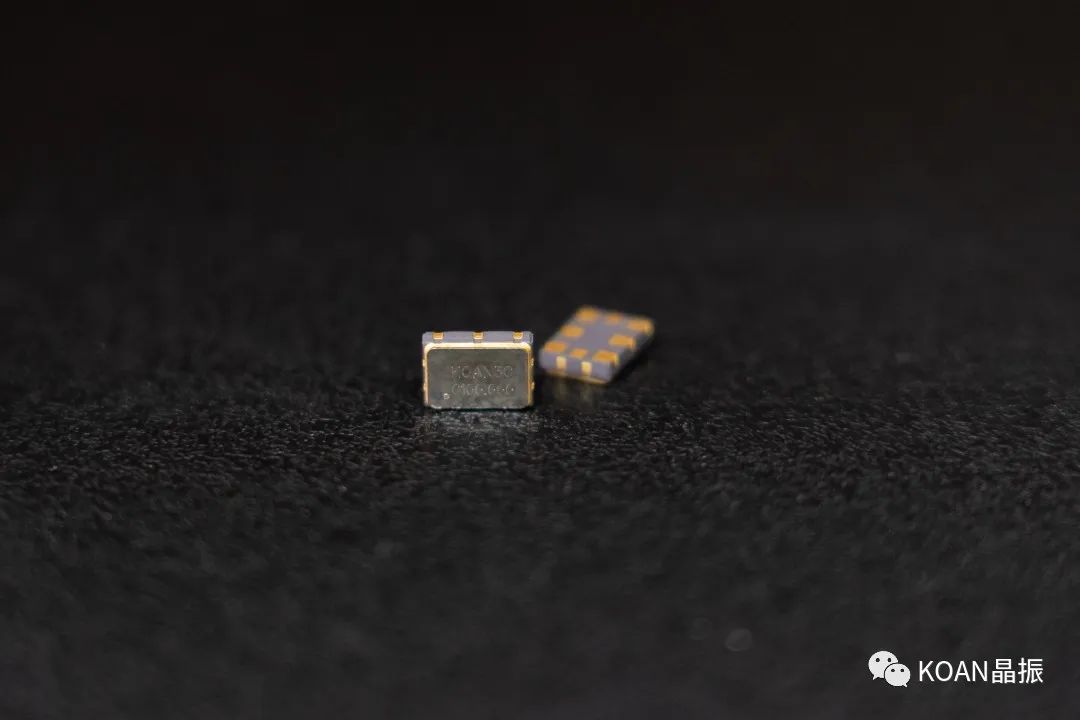

描述

1.选用公差和谐振阻抗较小的晶体

在采购不同批次晶体时,要保证频率公差和谐振阻抗的一致性。当晶体放入振荡电路中,电路的损耗会降低Q值。在线Q值高,可以改善振荡电路的近端相位噪声和抖动。往期文章:[《石英晶体的品质因数Q值]

2.选择合适的激励功率

随着晶体的小型化发展趋势,振荡的能量需求变小。如果激励功率过大可能破坏晶体的内部机理,引起振荡频率异常、稳定度下降、频率失真等现象,更为严重的导致电极受损。

在电路设计时,KOAN小妹建议您确认所使用的激励等级绝对不超过最大激励等级。

不同封装晶体的激励等级参考值:

- 49U/49S/SMD: 100uW (500Max)

- SMD贴片MHz: 10uW(100Max)

- 32.768kHz: 0.1uW(0.5Max)

如果产品设计有缺陷,造成激励功率不匹配,容易导致振荡频率可变范围变窄,电流异常增大,最后稳定性变差。

如果需要减小驱动功率,可采取以下措施:

- 增大限流电阻→反相放大器的输出幅度将会减小→减弱驱动功率

- 应保证振荡宽度超过RR的5倍

- 减小外部负载电容→振荡电路阻抗将会增加→实际驱动功率随之减小

- 负载电容减小,导致振荡频率增加。如果超出使用范围,可采购低负载晶体配合调整。

3.合适的匹配电容(满足相位条件)

晶体两端匹配电容愈接近晶体负载容量CL,目标频率愈精准。增加匹配电容,负载增大,频率下降,振荡宽度和振荡幅度会减小,

4.振荡宽限(满足振幅条件)

石英晶体振荡器的振幅条件是振荡起动及能正常持续振荡的条件,回路上的负性电阻绝对值│-R│。

负性电阻 |- R| = Rtest + Re

Rtest=与晶振串联连接纯电阻

Re=振荡时的有效电阻=R1(1+C0/CL)^2

建议振荡宽限为晶振等效串联电阻RR的5倍之上:│-R│≥ 5RR;电路进入正常振荡状态时│-R│变小:达到RR=│-R│。

5.选用合适的振荡IC

振荡IC制造商的不同,导致带来电路常数和电路配置的不同,从而对晶体的振荡产生影响。

振荡电路的工作频率如果不在晶体谐振器标称频率范围内,称为“不规则振荡”,我们可以调整阻尼电阻和外部电容来避免不规则振荡。

6.其它因素:电路,环境

KOAN晶振会根据客户端电子产品的特殊电路基础和环境需求,为您精选晶体,提高振荡电路的稳定性。

-

振荡电路的设计与应用 【日 稻叶保】2025-04-15 431

-

振荡电路的设计与应用 [日 稻叶保]2025-03-07 316

-

最实用的振荡电路设计资料2018-11-29 5099

-

最简单的RC振荡电路图大全(十款最简单的RC振荡电路设计原理图详解)2018-03-26 347360

-

《振荡电路的设计与应用》2017-11-24 2245

-

AN2867_ST处理器的振荡电路设计2016-12-12 1148

-

振荡电路设计与应用part22016-06-21 775

-

振荡电路设计与应用2016-05-05 3703

-

晶体振荡电路设计_CN2015-12-25 1056

-

剖析正弦波振荡电路2014-09-22 9802

-

振荡电路的原理及电路的剖析2012-12-24 28507

-

振荡电路设计大全2012-06-04 46918

-

振荡电路的设计与应用-实用电子电路设计丛书2010-03-02 1133

全部0条评论

快来发表一下你的评论吧 !