信号完整性之差分信号(一)

描述

1 什么是差分信号

差分信号是指利用两个输出驱动pin去驱动两根传输线。这两根传输线,一根传输信号,另一根传输它的互补信号。接收端看到的信号是这两条传输线上的信号压差。差分对就是用来传输一对差分信号,并且存在耦合关系的传输线。例如LVDS就是一种常见的低压差差分信号。

差分信号和单端信号比较,有如下特点:

(1)差分信号的总dI/dt比单端信号少,降低EMI噪声和轨道塌陷。

(2)差分信号在一对紧耦合差分传输线上传输,对返回路径的依赖没那么大。

(3)同样的,差分信号在通过连接器、接插件时,对返回路径要求也没那么高。(单端信号通过连接器、接插件时,受制于返回路径的影响,可以看上一篇文章)。

(4)使用差分线可以实现远距离差分信号的传输。

(5)差分信号的缺点是,如果设计不恰当,在差分信号线上有共模信号存在,会带来额外的EMI问题。

(6)传输同样的数据,差分信号需要2根信号线。这意味着电路连接更多、所需PCB面积更大。

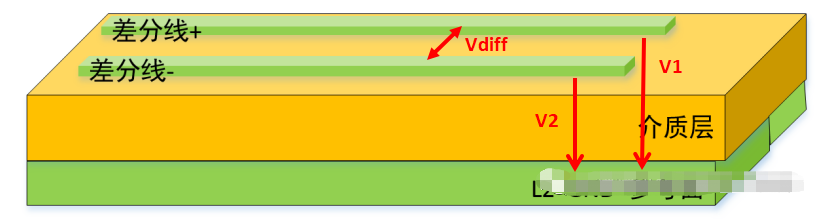

下图是一对差分信号。差分线+和GND之间信号电压是V1,差分线-和GND之间信号电压是V2。差分线之间的电压是Vdiff

差模信号:Vdiff=V1-V2

共模信号:Vcomm=1/2*(V1+V2)

V1=Vcomm+1/2*Vdiff

V2=Vcomm-1/2*diff

这些信号和公式可以用来描述任何一对传输线上的信号,即使它们本身不是同一组差分对信号。

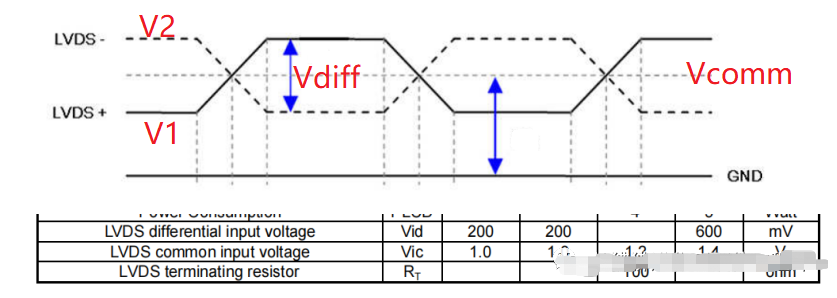

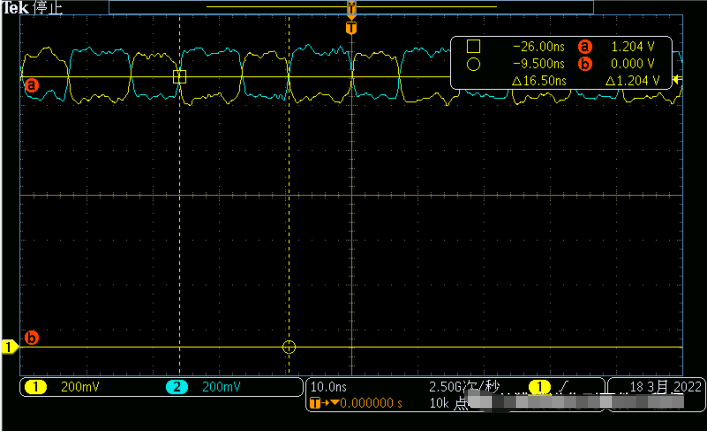

下图是某芯片的LVDS信号定义和其测试波形。

理论上共模信号是恒定的。但实际上,因为PCB设计、线缆的差异等,都会引起共模信号的改变,并且带来两个问题。

(1)当共模信号过高时,负载端差分接收器的输入放大器会饱和,使之不能准确读取差分信号电压值。

(2)当共模信号有变化时,会引起EMI问题。

2 差分对

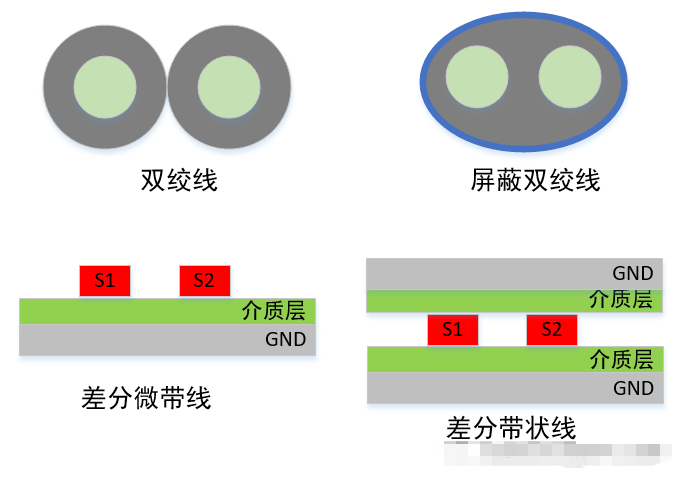

上面提到差分对就是用来传输一对差分信号,并且存在耦合关系的传输线。理论上说,任何两条传输线都可以构成一个差分对。下图是几种差分对。

虽然任何两条传输线都可以构成一个差分对,但是真正的差分信号,为了确保信号完整性,还是需要仔细设计:

(1)差分对的横截面积需要恒定不变,确保有恒定的阻抗。它们可以保证信号反射和失真最小。

(2)差分信号的长度要一致,目的是确保每根线上的时延相同。如果差分对的长度不同,会造成差分信号有时延和skew问题,进而导致共模噪声出现。

(3)差分对的两条线要完全对称。例如两条线的线宽、两条线到介质层的距离要完全相同。再例如果一条线上有测试焊盘,另一条线上没有测试焊盘,这种不对称就会带来共模信号。

(4)差分对的两条线可以不耦合(这并不常见)。没有耦合的差分线对抗噪声的能力会下降。差分线间的耦合程度越强,差分信号就越不容易受到干扰。

(5)差分对信号的最重要电气特性就是差分阻抗。

3 无耦合的差分对阻抗

(一)无耦合的差分对阻抗

差分信号的阻抗是差分信号电压和电流的比值。

什么样的差分对算是无耦合的差分对?为了使差分对的耦合降到最小,需要拉大差分对之间的距离,足够大的距离使差分对之间没有耦合。例如差分对的线间距至少是线宽的2倍,此时它们之间的耦合关系就不大了。

假设差分线中的每根单端线的单端阻抗Z0=50Ω,每根单端线和地平面(返回路径)之间的电压差是Vo,流过每根单端线和返回路径的电流是Io,它们之间的关系是

Io=Vo/Zo

因为差分线上的信号是反向的。针对差分线+,假设它的信号是从0V跳变到1V;同时差分线-上,它的信号是从1V跳变到0V。每根线都有一个电流。

流过差分线+的电流是Io=1V/50Ω=20mA。流过差分线-的电流也是20mA,只是电流方向和前者相反。差分线+和差分线-之间的差分信号压差是1V-(-1V)=2V。差分信号的阻抗是

Zdiff=Vdiff/Io=2V/20mA=100Ω=2*Zo

看起来差分阻抗是单独阻抗的2倍,当然这仅仅针对无耦合关系的差分对。

(二)无耦合的差分对端接

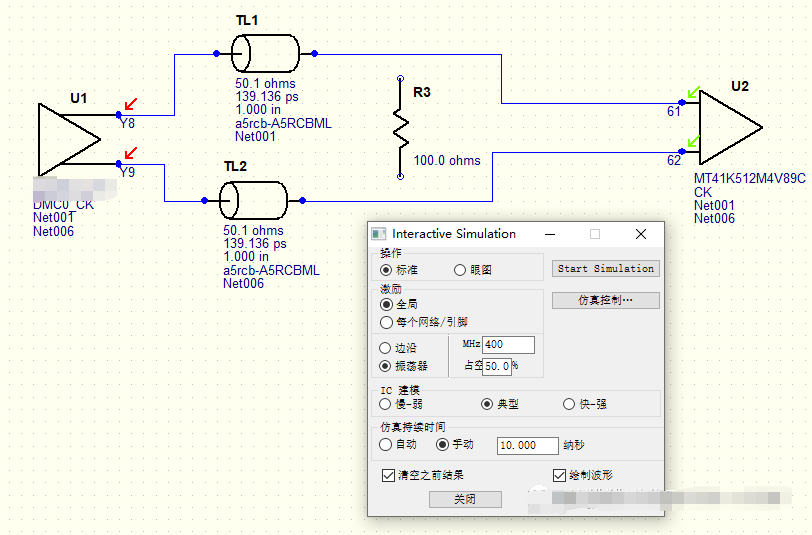

差分信号从源端传输到负载端,如果负载端阻抗很大。差分信号会反射回源端,多次反射就会带来振铃问题,影响信号质量。如下图中U1是一颗SOC,U2是一颗DDR。TL1和TL2是SOC和DDR之间的CLK+和CLK-传输线。

当R3不连接时,由于差分信号在差分传输线上来回反射,会造成信号有振铃。

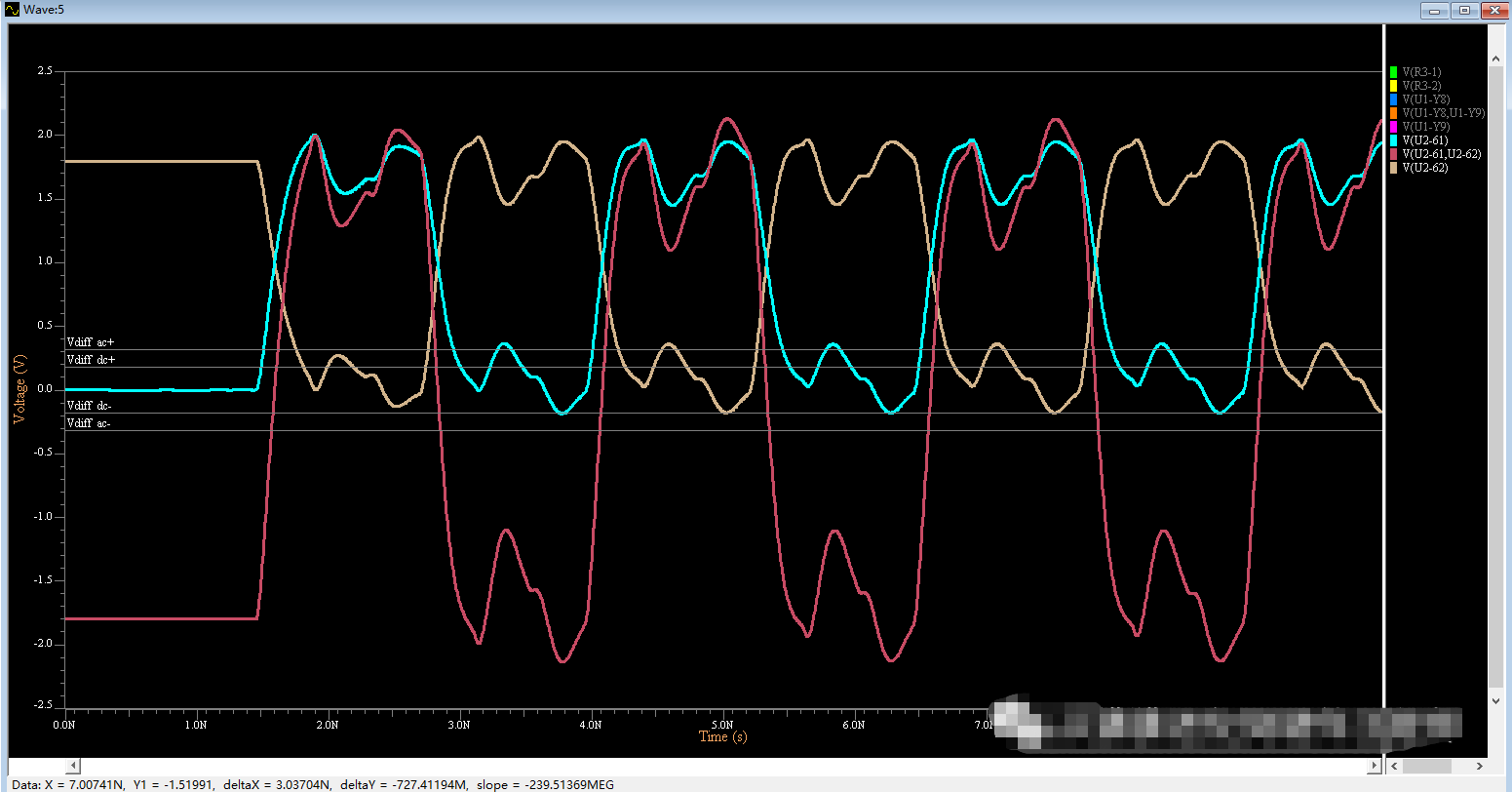

如下图是U2上的CLK+、CLK-、CLK+和CLK-的差分信号波形。

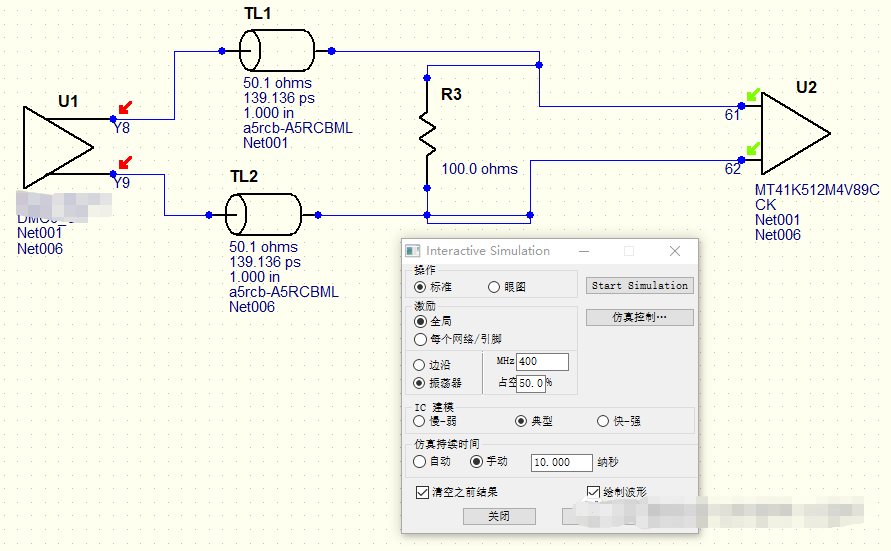

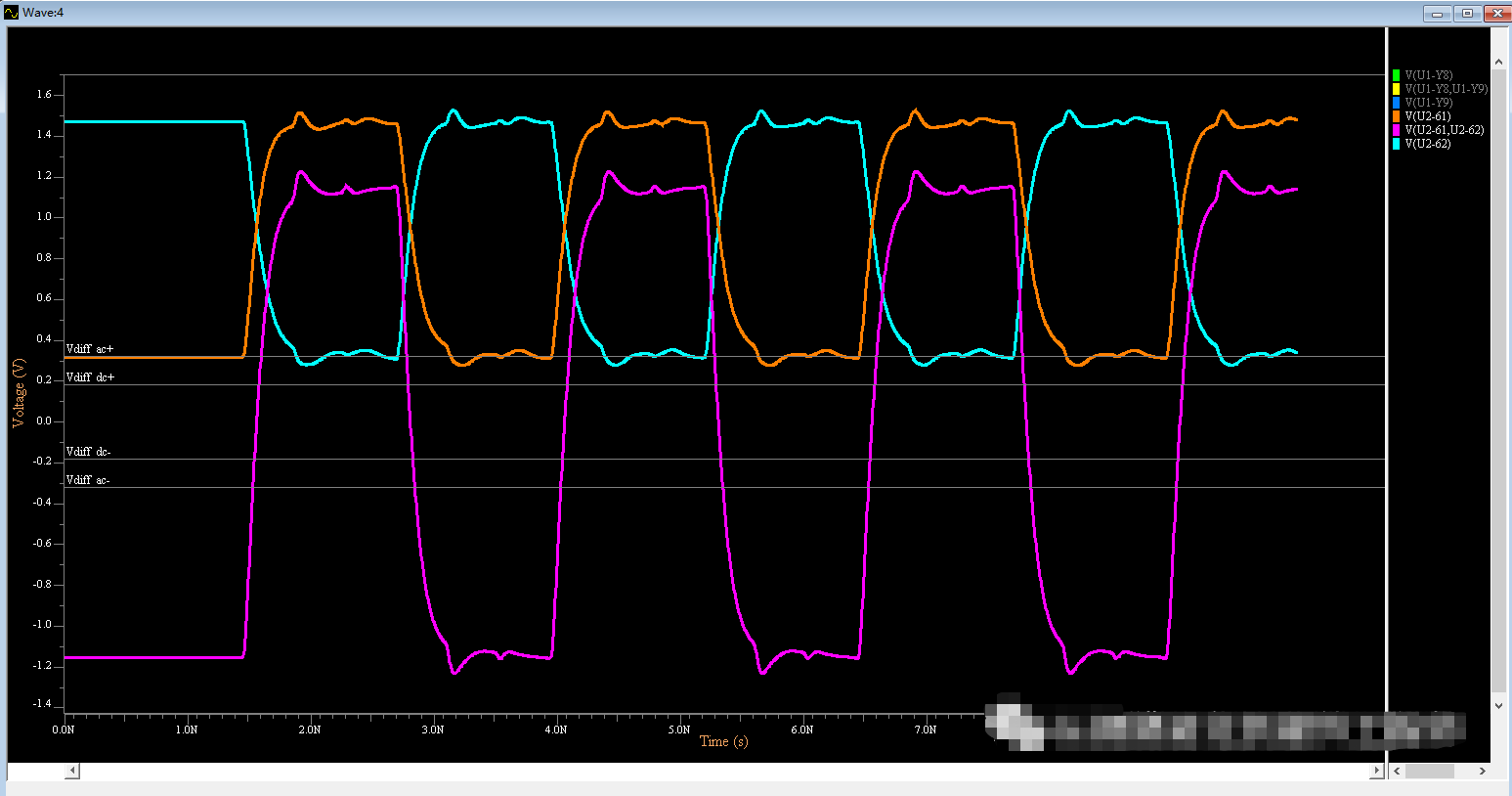

修改电路和PCB,使R3=Zdiff=100欧姆,并且让R3靠近DDR的时钟pin放置时(图中R3接入网络),信号质量明显变好。

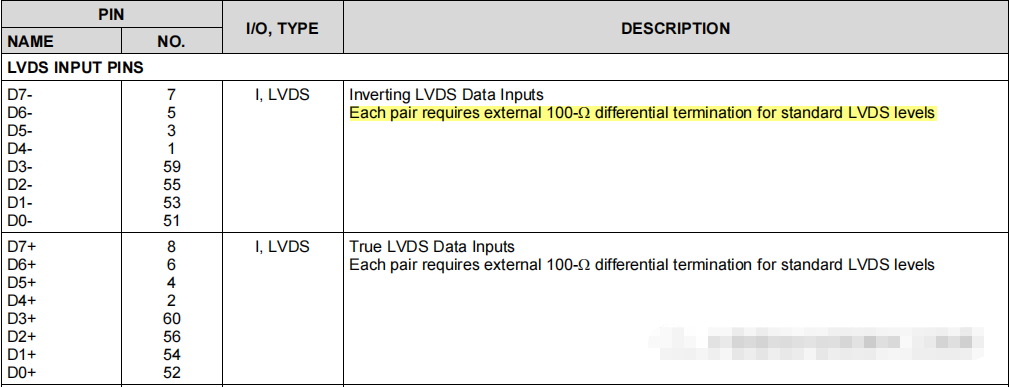

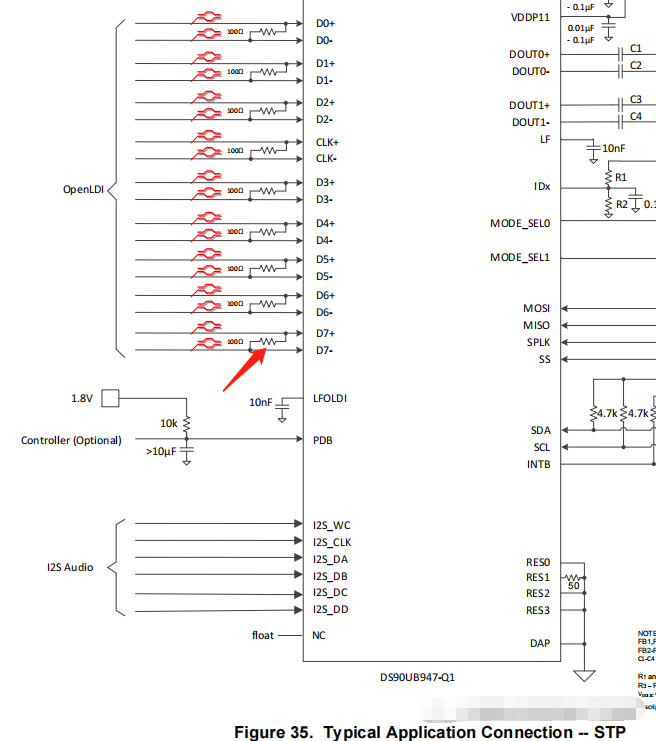

再例如TI的串行器DU90UB947。它是一颗接收来自SOC的LVDS信号,再将其转换成FPD-LINK信号,通过同轴电缆或者双绞线传输出的芯片。在汽车中控和仪表显示中,用来连接Head unit和中控屏幕或者仪表屏幕。在947的spec中就提到设计SOC和947之间的LVDS信号时,需要在靠近947那边布置100欧姆匹配电阻。

-

吴少奇

2024-08-12

0 回复 举报“修改电路和PCB,使R3=Zdiff=100欧姆,并且让R3靠近DDR的时钟pin放置时(图中R3接入网络),信号质量明显变好。”请问下这里并联R3的作用是使接收端阻抗近似为100欧姆,差分对走线与接收端达到阻抗匹配,所以信号质量变好吗? 收起回复

吴少奇

2024-08-12

0 回复 举报“修改电路和PCB,使R3=Zdiff=100欧姆,并且让R3靠近DDR的时钟pin放置时(图中R3接入网络),信号质量明显变好。”请问下这里并联R3的作用是使接收端阻抗近似为100欧姆,差分对走线与接收端达到阻抗匹配,所以信号质量变好吗? 收起回复

-

差分信号对信号完整性的影响2024-12-25 2022

-

听懂什么是信号完整性2024-12-15 1385

-

什么是传输线?什么是信号完整性分析?为什么传输线要测试差分信号?2023-10-23 1850

-

什么是信号完整性?2023-06-27 3603

-

信号完整性基础--差分信号(一)2023-06-09 7456

-

信号完整性之差分信号(四)2023-05-09 3253

-

信号完整性之反射(一)2023-04-15 3194

-

何为信号完整性?信号完整性包含哪些2021-12-30 2872

-

怎样学好“信号完整性”?2017-08-29 21540

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

信号完整性原理分析2009-11-04 1287

-

信号完整性分析与设计2009-09-12 58809

-

什么是信号完整性2009-06-30 5874

全部0条评论

快来发表一下你的评论吧 !