FPGA原型系统装配文件:Assign Traces介绍

可编程逻辑

描述

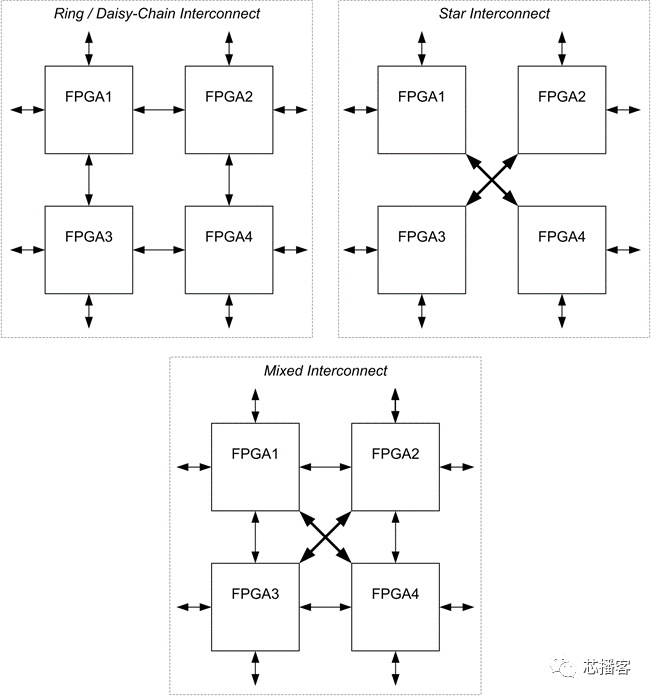

多片FPGA原型验证系统的拓扑连接方式各不相同,理想的多片FPGA原型验证系统应该可以灵活配置,可以使用其相应的EDA工具,根据SoC的特性,自动选择拓扑连接方式,比如以下几种连接方式,不同的FPGA之间连接的路径是在相应的FPGA上可以作为“分组”来使用的,这个连接的的路径我们称为trace,因此如何合理分配trace变得尤为重要,甚至颠覆我们通常认为的限制因素——FPGA上IO的数量。

一直以来,我们一直认为FPGA的IO引脚的数量是有限的。然而,实际上我们应该讨论不同FPGA上的引脚之间的连接。板上的迹线数量或能够连接这些FPGA的IO引脚的线缆和路由开关的宽度是真正的限制。

在一个设计良好的平台中,每个FPGA 的IO引脚都将连接到FPGA电路板描述的装配文件中,这是有用且准确的文件。然后,分区工具将准确无误地知道哪些trace准确且可用(因为有些IO确实是损坏的,就判定不可用),以及它们连接到哪些FPGA引脚。如果FPGA电路板装配文件描述准确,那么引脚分配将因此也准确。

所以这一部分被称为“分配跟踪(Assign traces)”,而不是“分配FPGA引脚”,不应该认为我们将每个FPGA顶部的信号分配给该FPGA上的引脚,而是应该将其视为将信号分配给traces,以便这些信号传播以固定trace运行的所有FPGA引脚。

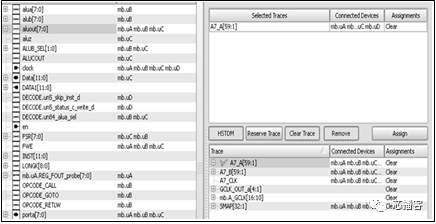

我们期望EDA工具自动化迹线分配过程,同时可以展示FPGA电路板上的可用traces和允许的电压区域,并允许自动信号分配。跟踪分配环境应帮助我们识别时钟、重置和其他关键信号。它还可以帮助我们按目的地对跟踪进行排序,并为特定跟踪的分配筛选合适的traces。

某原型验证EDA的跟踪分配窗口的一个视图如上图所示,其中我们可以看到左侧列出的需要分配的信号。这里我们可以看到,用户已经选择了一条由八个信号组成的总线,称为alout,如相邻列表所示,它需要连接到已划分为设备mb.uA、mb.uB和mb.uC的逻辑。

一旦选择了一个信号或一组信号,在右下角会出现一个经过过滤的板上候选trace列表,那些可用的并且至少连接到所需的FPGA。然后,我们选择我们的候选trace和相应的信号,并用相关按钮确认分配。

将信号分配给trace的建议顺序如下:

分配时钟、复位和其他全局输入。

分配test points或probe output以匹配FPGA电路板上的连接器。

分配连接到专用资源或连接器的顶端IO。

在了解电压电平要求的情况下,分配其余的设备间信号。

在每种情况下,对于任何选择的信号,都可能有不止一个候选轨迹。

我们按照以下优先顺序从候选轨迹中进行选择:

与信号具有相同端点的任何可用迹线。

如果没有traces符合1中的标准,则traces具有与信号相同的端点,加上最小数量的多余端点。多余的端点意味着FPGA引脚将被浪费。

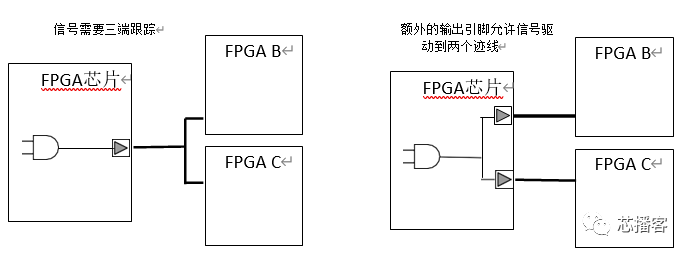

如果没有trace符合2中的标准,那么我们必须使用信号源FPGA的两个输出引脚将信号分割成两条trace,如下图所示。

当不存在至少包括信号所需的端点的迹线时,可以使用驱动FPGA和每个接收FPGA之间的多个trace。

我们的EDA工具应该能够自动将输出拆分到两个FPGA引脚上,而无需更改RTL。通过简单地将信号分配给多个traces来实现。然后,该工具增加驱动FPGA上的引脚数,并将信号复制到额外的trace上。

通常,在遵循上述推荐的偏好顺序的同时,可能会有多个等效的traces,信号可以应用于这些trace,在这些情况下,我们选择哪一个是无关紧要的。这强化了一个概念,即对于许多信号,我们使用哪一个FPGA引脚并不重要,只要它们都在同一trace上连接在一起。

鉴于上述过程相当有条理,EDA工具按照相同的规则进行自动分配相对简单。事实上,我们可以采取一种混合方法,通过手动进行最重要的连接,并允许工具自动完成对不太重要的信号的分配。

自动工具将遵循与我们自己类似的分配顺序。当自动工具从FPGA向其他资源分配跟踪时,我们可以通过向其提供指导来最小化手动分配步骤。通过使用相同的命名约定命名信号和资源管脚,工具可以识别,例如,信号addr1连接到ram_addr1及其关联的跟踪,而不是任何其他trace。通过这种方式,我们可以有条不紊地完成跟踪分配,并在工具的指导下,快速分配数千个FPGA引脚,而不会出错。

FPGA原型团队在许多项目中开发了自己的引脚分配脚本。这些脚本从虚拟FPGA综合运行的日志文件中提取顶层信号名称,并将其转换为简单的格式,可将其导入到常用的桌面电子表格应用程序中。然后,团队使用电子表格对信号名称进行文本搜索,并将其分配给正确的FPGA引脚。还将包含所有FPGA连接的定制板描述导入电子表格。然后,电子表格将生成端号列表,这些端号列表可以导出并再次编写为正确的UCF格式,用于布局布线。

这种方法很少见,因为它不仅需要开发和支持脚本、电子表格等,而且可能不是原型团队的核心能力和最佳时间利用。此外,我们还为项目中的错误引入了另一个机会。然而,这个例子确实强调了一点,即如果我们熟练且有决心,我们可以在没有专业EDA工具的情况下进行基于FPGA的原型设计。这可能是一个大多数人都会避免的“做还是买”的决定,而是默认使用目前市场上经过商业测试的分区工具。

审核编辑:刘清

-

验证中的FPGA原型验证 FPGA原型设计面临的挑战是什么?2022-07-19 2371

-

怎么采用FPGA原型系统加速物联网设计?2018-08-07 2527

-

如何通过LabVIEW FPGA加速嵌入式系统原型化?2021-05-06 1486

-

将 Virtualizer 虚拟原型和 HAPS 系列基于 FPGA 的原型无缝集成2017-02-08 560

-

FPGA 原型设计及发展趋势介绍2018-07-19 2771

-

一些常见的PCB原型设计和装配神话解析2019-08-06 2807

-

F4飞行控制器系统的焊接装配文件2020-07-06 721

-

关于FPGA开发板和原型验证系统对比介绍2022-04-28 3489

-

如何在N多选择中,为FPGA原型验证系统规划实用高效的接口?2022-09-19 1159

-

如何建立适合团队的FPGA原型验证系统平台与技术?2023-04-03 2011

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 2571

-

多台FPGA原型验证平台系统如何实现自由互连2023-04-11 909

-

多片FPGA原型验证系统互连拓扑分析2023-05-23 2154

-

什么是FPGA原型验证?FPGA原型设计的好处是什么?2024-01-12 2131

-

assign语句和always语句的用法2024-02-22 4557

全部0条评论

快来发表一下你的评论吧 !