三维封装工艺流程与技术

制造/封装

描述

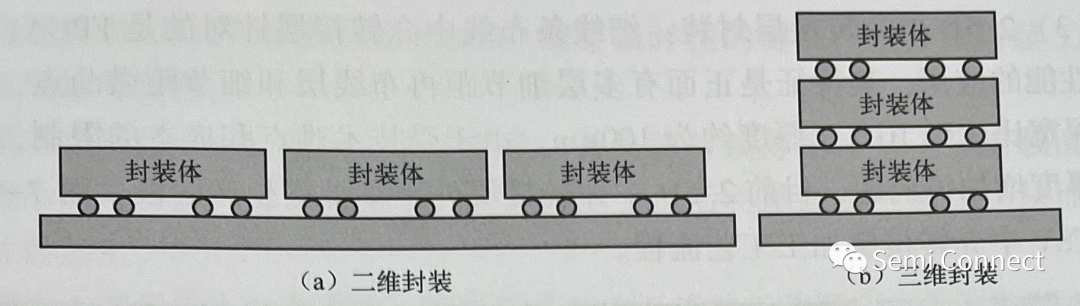

三维封装通过非 WB 互连技术实现芯片间的高密度封装,为微电子系统封装在三维空间开辟了一个新的发展方向,可以有效地满足高功能芯片超轻、超薄、高性能、低功耗及低成本的需求"。该技术主要应用在高速计算、网络和GPU 等系统芯片中。传统二维封装与三维封装对比示意图如图所示。

芯片级三维封装可以提高封装密度,减小封装尺寸,提高信号传输速度降低功耗和噪声,实现产品多功能化。由于封装密度增加,体积减小,三维封装产品的发热量大幅提升,如何解决其散热问题是该封装技术之关键、

三维封装主要分为芯片叠层三维封装和混合型三维封装两种结构类型。

1. 芯片叠层三维封装

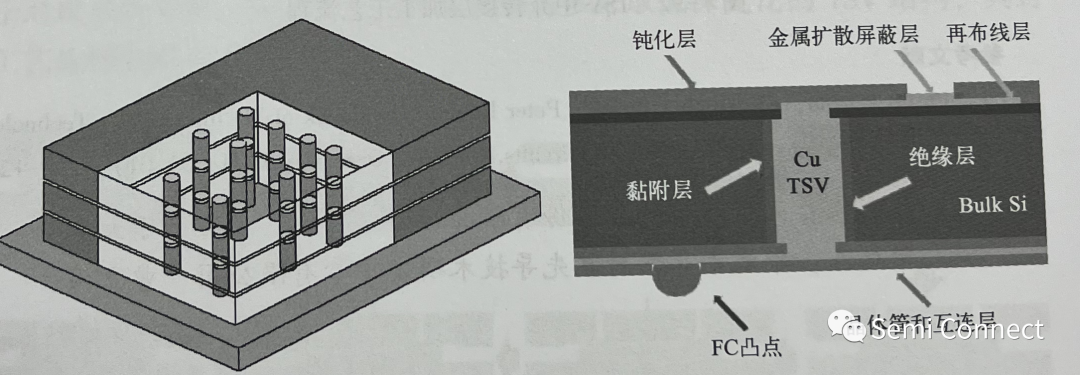

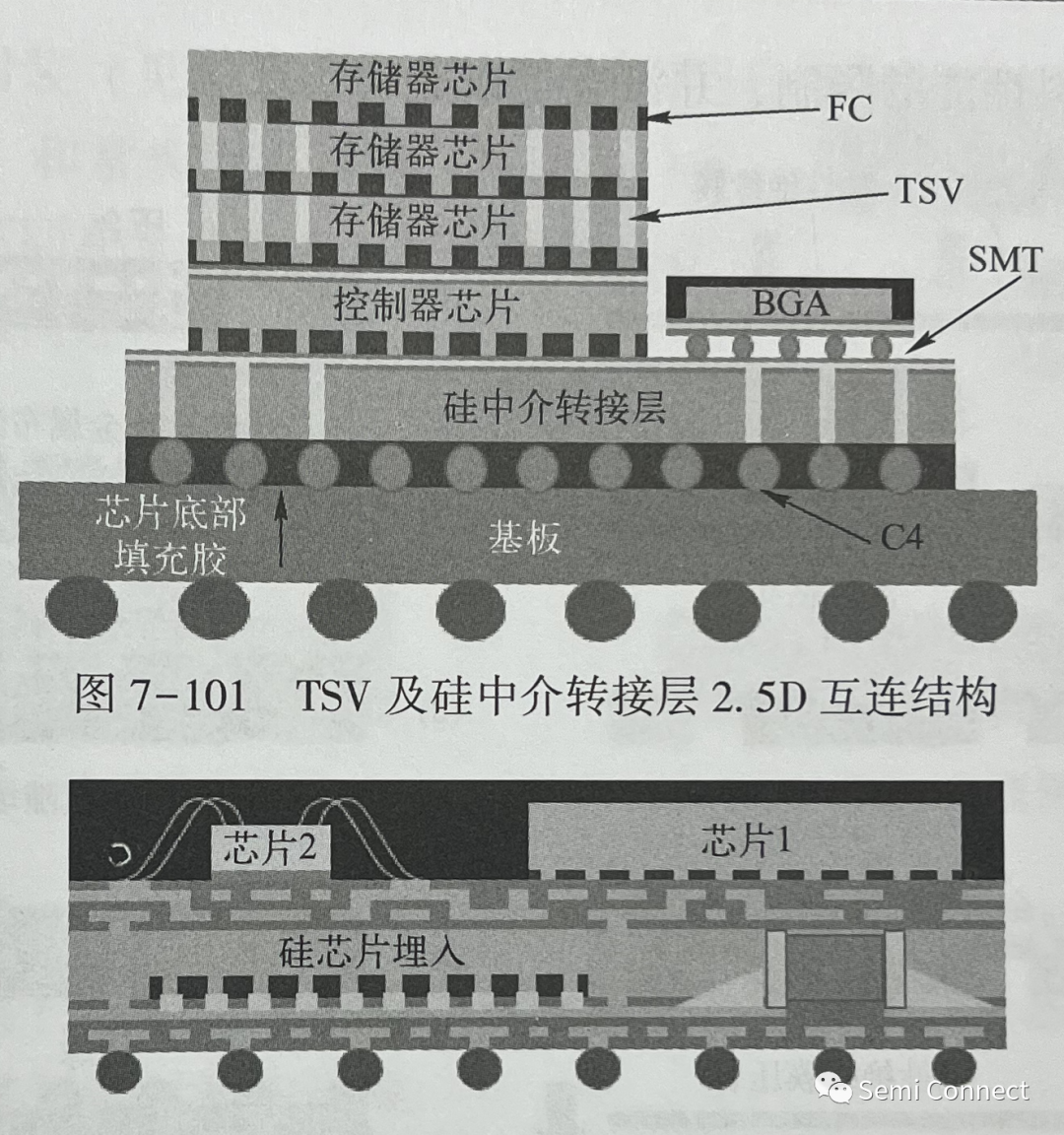

芯片叠层三维封装结构是将芯片在纵向上进行堆叠,采用TSV 互连技术HMC (Hybrid Memory Cube)技术进行芯片互连。如图1所示,存储芯片通过TSV 及微凸点与逻辑芯片互连,逻辑芯片通过 1SV 及微焊点与封装基板互连,封装基板通过倒装回流焊与 PCB 互连。TSV 中介转接层作为互连的关键部分,可以提高互连密度,增加带宽,其结构如图2所示。TSV 制作过程包括成孔、线性沉铜填孔、再布线及凸点制作等。

芯片叠层三维封装通常采用圆片到圆片 ( Wafer to Wafer,w2W)、芯片到圆片 (Die to Water, D2W)、芯片到芯片 (Die to Die, D2D)三种工艺流程,如图7-96 至图7-98 所示。

w2W 类型堆叠产品是先将两个圆片对齐,然后将两个圆片整体焊接,最后将堆叠芯片切割成单个芯片。根据焊接面对应关系,可分为背对面焊接及面对面焊按两种方式。该类型堆香产品共面性较好,但是要求第1个芯片与第2个芯上,之后将上层芯片煤按在底层芯片上。该炎型堆益产品可以解决 w2W &D2N 炎型推叠工艺对芯片尺寸的限制,上层芯片与下层芯片尺寸没有特别要水。

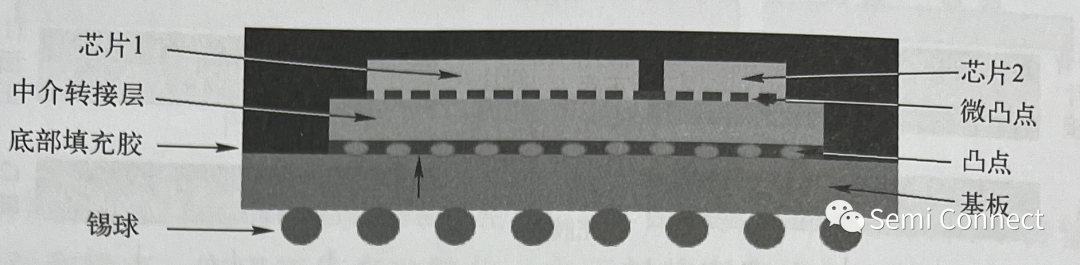

2.5D封装结构是指多个芯片并排放置在同一个封装体中,芯片之间通过高密度中介转接层形成高密度互连系统,如图所示。

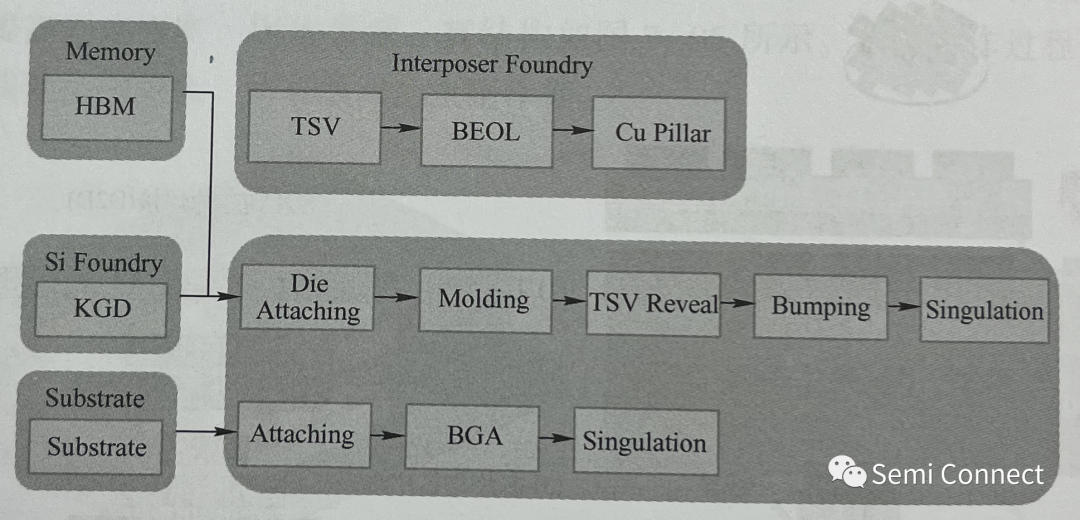

多芯片、微凸点及介质层是2.5D封装的主要组成部分。典型的硅介质层技术包括 TSI (Through Si Interposer)、ICLs (Low Cost Si Interposer)、POI (Photo- defined Organic Interposer)、ICCI ( Low Cost Class Interposer)和扇出型 WLP(Wafer Level Package)等。图7-100所示为 2.5D 封装工艺流程,图中 “HBM”表示高带宽内存 (High Bandwidth Memory ),“KCD”表示已知的合格芯片( Know Good Die) .“ BEOL”表示后工序作业线 (Back End of Line)。

2.混合型三维封装

混合型三维封装结构是指包含多种三维封装技术的组合封装结构。图7-101所示为 ISV 及硅中介转接层 2.5D 互连结构,图中存储器芯片与控制器芯片之间、CPU 与3D封装之间,通过硅介质中的硅通孔(TSV)中介转接层进行互连,形成混合型2.5D的三维封装结构;如图所示为 EMIB (Embedded MaltrDie Interconmect Bridge)互连结构,它是不同于 ISV 的另一种三维互连转接技术,它能进一步降低三维封装的成本。

审核编辑:汤梓红

-

半导体封装工艺流程的主要步骤2025-05-08 6035

-

传统封装工艺流程简介2024-01-05 3369

-

SMT组装工艺流程的应用场景2023-10-20 1253

-

SMT组装工艺流程的应用场景(多图)2023-10-17 3127

-

封装工艺流程--芯片互连技术2022-12-05 2488

-

芯片封装工艺流程讲解2022-10-31 13006

-

芯片封装工艺流程是什么2021-08-09 73422

-

集成电路芯片封装工艺流程2021-07-28 14242

-

贴片机生产工艺流程的影响2018-11-27 2266

-

倒装晶片的组装工艺流程2018-11-23 4930

-

ic封装工艺流程2010-07-18 3636

-

LAMP-LED封装工艺流程图2010-03-29 3843

-

BGA的封装工艺流程基本知识简介2010-03-04 7088

-

IC芯片的封装工艺流程2008-05-26 29483

全部0条评论

快来发表一下你的评论吧 !