IC设计流程相关名词梳理(含各流程EDA工具梳理)

EDA/IC设计

描述

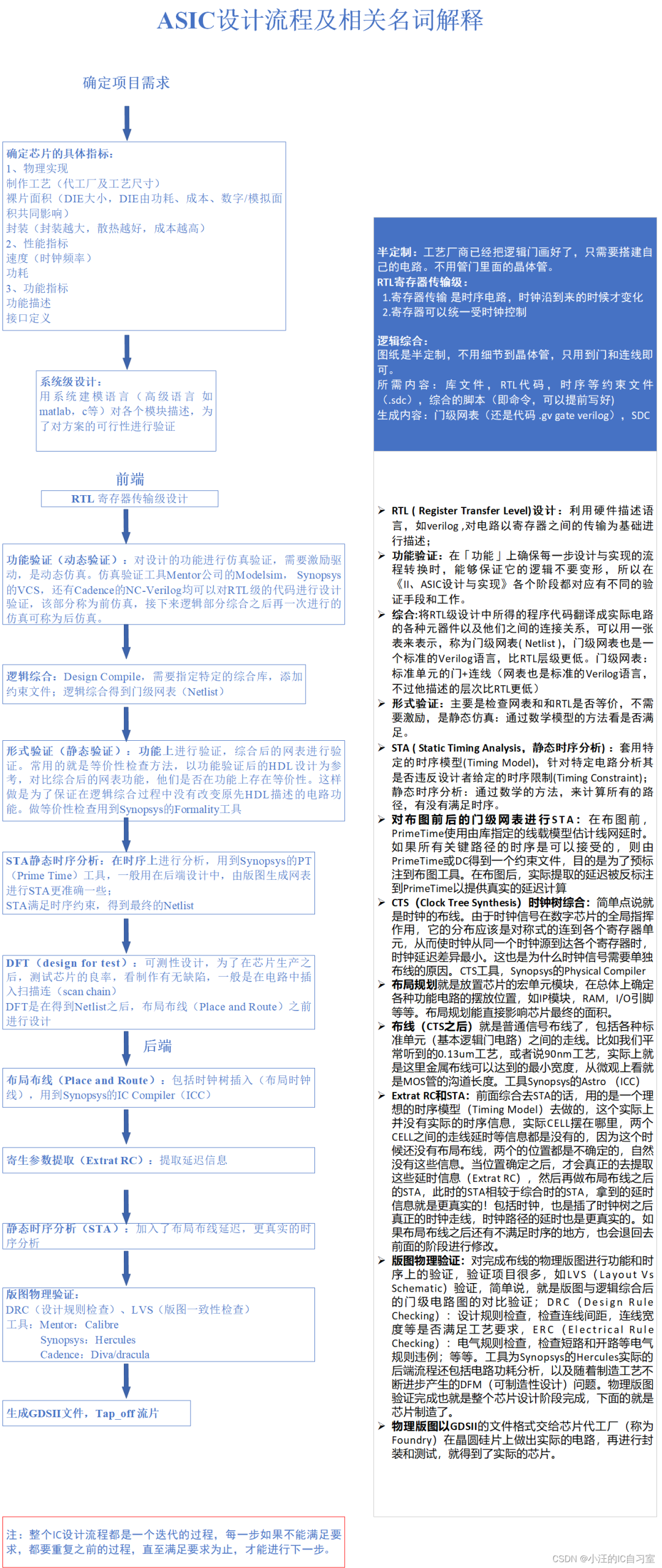

ASIC设计流程

一、确定项目需求

1. 确定芯片的具体指标:

物理实现

制作工艺(代工厂及工艺尺寸);

裸片面积(DIE大小,DIE由功耗、成本、数字/模拟面积共同影响);

封装(封装越大,散热越好,成本越高)。

性能指标:

速度(时钟频率);

功耗。

功能指标:

功能描述

接口定义

2. 系统级设计:

用系统建模语言(高级语言 如matlab,c等)对各个模块描述,为了对方案的可行性进行验证。

二、前端流程

1. RTL 寄存器传输级设计

利用硬件描述语言,如verilog对电路以寄存器之间的传输为基础进行描述。

2. 功能验证(动态验证):

对设计的功能进行仿真验证,需要激励驱动,是动态仿真。仿真验证工具Mentor公司的 Modelsim, Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证,该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

3. 逻辑综合(Design Compile):

需要指定特定的综合库,添加约束文件;逻辑综合得到门级网表(Netlist)。

4. 形式验证(静态验证):

功能上进行验证,综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。做等价性检查用到Synopsys的Formality工具。

5. STA静态时序分析:

在时序上进行分析,用到Synopsys的PT(Prime Time)工具,一般用在后端设计中,由版图生成网表进行STA更准确一些;

STA满足时序约束,得到最终的Netlist。

6. DFT(design for test)可测性设计:

为了在芯片生产之后,测试芯片的良率,看制作有无缺陷,一般是在电路中插入扫描连(scan chain);

DFT是在得到Netlist之后,布局布线(Place and Route)之前进行设计。

三、后端流程

1. 布局布线(Place and Route):

包括时钟树插入(布局时钟线),布局布线用到Synopsys的IC Compiler(ICC)工具。

在布线(普通信号线)之前先布局时钟线,即时钟树综合CTS(Clock Tree Synthesis),用到Synopsys的Physical Compiler工具。

2. 寄生参数提取(Extrat RC):

提取延迟信息

3. 静态时序分析(STA):

加入了布局布线延迟,更真实的时序分析

4. 版图物理验证:

DRC(设计规则检查)、LVS(版图一致性检查)

工具:

Mentor:Calibre

Synopsys:Hercules

Cadence:Diva/dracula

5. 生成GDSII文件,Tap_off 流片

(注:整个IC设计流程都是一个迭代的过程,每一步如果不能满足要求,都要重复之前的过程,直至满足要求为止,才能进行下一步。)

IC设计流程相关名词梳理(含各流程EDA工具梳理)

编辑:黄飞

-

EDA全流程的重要意义,以及国内EDA全流程进展2023-12-14 3772

-

梳理单片机学习方法、产品开发流程2023-09-21 1406

-

ARM代码编译与链接调试的工作流程梳理2022-02-09 642

-

嵌入式系统概述知识梳理2021-12-22 1256

-

你都知道变电的相关名词有哪些吗2021-09-22 1847

-

LWRP渲染流程梳理2021-02-03 850

-

LWRP的渲染流程2021-01-21 1791

-

数字IC设计流程2020-12-09 8292

-

利用tracepoint梳理调度器框架及主要流程2020-10-30 2941

-

IC设计前后端流程与EDA工具介绍2018-04-19 12693

-

ERP、CRM实施中流程的梳理?2017-08-17 4134

-

EDA设计流程及其工具2016-12-11 1163

-

IC设计流程2012-01-11 10728

-

电池相关名词解释(一目了然)2010-01-23 15492

全部0条评论

快来发表一下你的评论吧 !