FPGA系统中有源电容放电电路设计需注意哪些问题

描述

电信设备,服务器和数据中心的FPGA具有多个电源轨,需要正确排序才能安全地为这些系统上下供电。高可靠性DC-DC稳压器和FPGA电源管理的设计人员需要一种简单的方法来安全地放电大容量电容器,以避免损坏系统。

FPGA电源排序

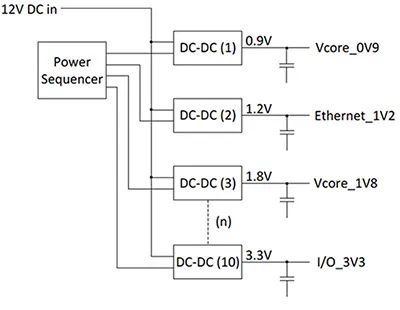

在生成片上系统FPGA的过程中,它们可以提供十个独立的电源轨,为Vcore,存储器总线电源,I/O控制器,以太网等提供电源。如图1所示,每个电源轨由DC供电。直流转换器可调节3.3 V,2.5 V,1.8 V,0.9 V等所需的电压。为了给系统加电,遵循特定的顺序以确保安全操作并避免损坏系统。同样在系统关闭期间,电源序列的顺序相反,确保在下一个电源轨关闭之前禁用每个电源轨。该指令通过电源序列发生器芯片控制,该芯片可启用每个DC-DC稳压器,如图1所示。

图1:典型FPGA系统电源轨每个服务的供电。

考虑存储在各种电源轨上的去耦电容中的电荷时会出现问题。例如,在0.9 V Vcore电源轨上,总去耦电容可以在10到20 mF的数量级,并且存储在电容器组中的剩余电荷需要在断电期间主动放电,在下电源关闭之前序列被禁用。这样可以避免违反掉电序列并保护FPGA系统。因此,建议在每个DC-DC稳压器输出端使用有源放电电路。

有源电容放电开关

通过了解电容器组的大小,可以采用开放式方法对RC时间常数进行放电。一旦电压小于充电状态的95%(在3×RC时间常数下发生),则假设电容器放电。

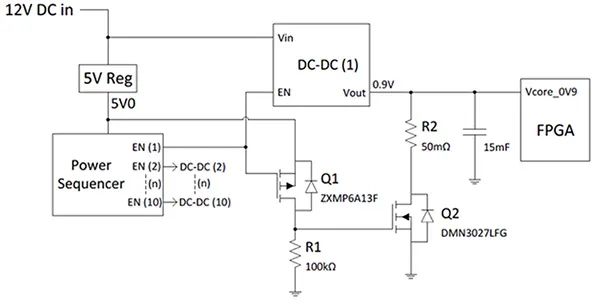

这样做的一个简单方法是通过一个具有已知接地电阻的开关,当需要放电时可以接通该开关。参考图1,电源序列发生器启用每个DC-DC稳压器的输出。然后可以使用该相同的使能(EN)信号来馈送并联连接到电容器组的开关。通过反转使能信号来驱动开关,当DC-DC稳压器的输出被禁止时,它将使电容器放电。对于开关,N沟道功率MOSFET,因为它很容易从以地为参考的逻辑信号驱动。所选电路如图2所示,Q2为N沟道功率MOSFET,Q1为P沟道MOSFET,反转电源序列发生器的EN逻辑信号。

图2:有源放电电路。

有源电容放电电路操作

参见图2 - 电源序列发生器的EN输出为DC-DC稳压器上的使能引脚供电以及电容器放电电路。当逻辑“0”发出关闭信号时,P沟道MOSFET(Q1)将信号反相,然后接通N沟道MOSFET(Q2)以对电容器组放电。

放电电路假设一旦关闭信号施加,DC-DC稳压器就无法继续产生输出。如果在关闭命令激活后,DC-DC稳压器的输出有电,则必须在放电电路激活之前引入延迟。这是为了确保放电MOSFET不会试图吸收DC-DC稳压器的全部输出电流能力。

为了从逻辑“0”信号增强N沟道功率MOSFET(Q2),P沟道MOSFET(Q1)将信号反相为5 V,以施加在Q2栅极源上。选择P沟道MOSFET(Q1)不具有低栅极阈值电压(VGS(th))。这是因为VGS(th)相对于温度下降并且Q1在逻辑“1”状态期间需要处于OFF状态以避免Q2的错误接通。需要选择适合5 V操作的值以及Power Sequencer。

当电源序列发生器输出逻辑“1”时,DC-DC稳压器在ON状态下使能,Q2必须处于OFF状态。采用逻辑“1”输出,高电平输出电压为4.19 V(电源序列发生器的EN引脚输出规格),则在环境工作温度为60°C时,Q1 VGS(th)需要大于0.9 V 。此外,Q2的栅极需要通过100kΩ的R1电阻下拉至源极电位,以避免误导通。

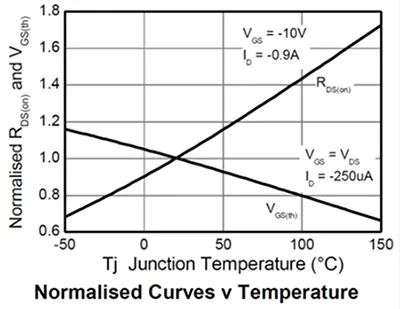

温度的VGS(th)变化在典型的电气曲线中找到。MOSFET数据表。例如,图3中给出了来自Diodes Incorporated的ZXMP6A13F的归一化VGS(th)与温度的关系.ZXMP6A13F是器件,因为保证VGS(th)在室温下为1 V,在60℃时降至约0.9 V °C。

图3:ZXMP6A13F的温度标准化RDS(on)和VGS(th)曲线。

当电源序列发生器使能输出变为逻辑'0'时,则存在0.270 V的低电平输出,Q1需要保证通过该5 V - 0.270 V信号增强通道,以确保Q2导通并放电电容器组。因此,Q1需要在VGS = -4.5 V时具有导通状态。

为了对电容器组放电,选择N沟道功率MOSFET(Q2)具有导通电阻(RDS(开) ))适合于在10 ms内对电容组放电,以确保在不到100 ms的时间内完成10个通道的完全关闭顺序。必须提供辅助电源,以在关闭电源后至少100 ms驱动关闭电路(电源序列发生器)。

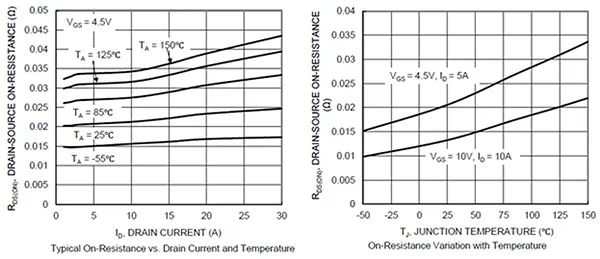

放电计算的时间

使用3 x RC时间常数,其中R是电容器组的ESR的组合电阻(假设<5mΩ),寄生走线电阻(假设为为<5mΩ),串联漏极电阻(R2)和功率MOSFET Q2 RDS(on)。还包括功率MOSFET导通电阻的温度依赖性,可以高达Tamb =25?C时RDS(on)的1.5倍,同时假设结已达到额定温度(典型TJ(值) )= 150°C) - 参见图5.

要在不到10 ms的时间内对15 mF电容器组放电,需要3 x RC = 8 ms:

电容器

因此,功率MOSFET Q2在VGS = 4.5 V,Tamb =25?C时需要RDS(on)<80mΩ。假设一个50mΩ的串联漏极电阻(在图2中称为R2)与MOSFET一起使用。

安全工作区和瞬态热应力

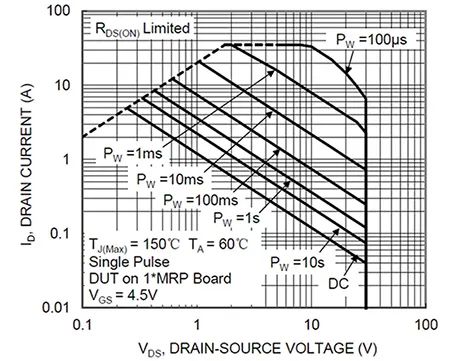

选择功率MOSFET Q2的额定功率能够处理放电电流的瞬态功耗。通过仿真计算峰值功率,并根据功率MOSFET数据表的瞬态功率容量图检查该值。由于功率MOSFET将随时间消耗电容器的能量作为电流和电压的函数,因此需要检查数据表中的安全工作区(SOA)曲线。这将提供功率MOSFET可以安全处理的单脉冲,同时确保结温不超过额定值,典型TJ(值)= 150°C。SOA应该基于应用的环境工作温度和所需的MOSFET栅极驱动,在这种情况下为4.5V。在放电0.9 V充电电容器组的情况下,然后检查SOA曲线,以获得1 V时的单脉冲峰值电流能力在1 ms和10 ms之间的脉冲宽度曲线。SOA应该针对典型的应用环境温度(假设为60°C),同时安装在PCB上,散热,也称为推荐焊盘(MRP)布局。在这些条件下,请参考图4了解DMN3027LFG的SOA。

图4:DMN3027LFG的安全工作区(SOA)

需要在实际电路中测量电容器组的峰值浪涌电流,以确保足够的电阻减慢响应速度,以避免可能导致EMI问题的急剧上升电流峰值以及N通道上的瞬态热应力功率MOSFET和电容器组。在图2中,将一个50mΩ串联电阻添加到Q2的漏极,以确保固定的已知值(与温度无关)在放电路径中的总电阻中占主导地位。

MOSFET导通电阻变化

请注意MOSFET的导通电阻随温度变化,如图5所示,在4.5 V栅极驱动的预期工作温度范围内变化高达15mΩ。除此之外,您还将在零件到零件和批次之间进行RDS(on)变化。典型的RDS(on)为22mΩ,在室温下DMN3027LFG上4.5 V栅极驱动的规格限制为26mΩ。

图5:DMN3027LFG的导通电阻温度响应。

因此,为确保已知电阻在放电路径中占主导地位,做法是使用R2系列电阻,该电阻约为RDS(on)的两倍在选定的门驱动器上。当R2为50mΩ且RDS(on)在15mΩ至40mΩ(典型值为22mΩ)之间变化时,95%的放电时间为3.9至5.4 ms(3 x RC)。这是差情况下电容器组大小为20 mF。

功耗

计算功率MOSFET Q2和串联电阻R2的功耗取决于占空比和Q2导通的时间。

如果在Q2导通时DC-DC稳压器上的0.9 V输出使能,那么Q2和R2之间可以达到11 W。假设结温达到150°C,典型的RDS(on)稳定在35mΩ,如图5所示。不应允许这种情况,因为它违反了DMN3027LFG的功耗并导致结点温度超过额定值。因此,必须禁用DC-DC稳压器输出,同时启用Q2。

这意味着坏的情况是由电容器短时间充电和放电引起的。假设电源序列发生器进入连续循环启用,然后每隔20 ms禁用DC-DC稳压器(10 ms启用+ 10 ms禁用),那么这将导致Q2和R2上的功率约为0.5 W.这是通过知道存储在电容器组中的总能量将每20 ms放电来计算的:

P = E/t =?CV2/20 ms = 500 mW,电容器组的C = 20 mF充电至1 V.

坏情况下,RDS(on)为40mΩ,26mΩx1.5,VGS = 4.5 V,TJ(值)= 150°C(图3)。因此,Q2和R2的功耗分别为222 mW和278 mW。15mΩ的RDS(on)会使R2的功耗增加到385 mW;意味着需要0.5 W额定值的表面贴装电阻。

在典型应用中,环境温度预计达到60°C,DMN3027LFG在推荐焊盘布局上的RθJA= 130°C/W,当耗散222 mW时,TJ达到90°C 。这为TJ()= 150°C提供了充足的空间。

电容器组放电测量

使用DMN3027LFG和ZXMP6A13F组装使用6 x 2,200 uF电解电容器(13.2 mF)的电容器组,如图2所示.ZXMP6A13F用5 V手动触发信号。

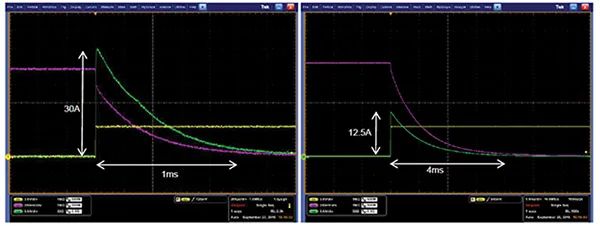

使用和不使用50mΩ串联电阻进行测量,然后在室温,零下和高温下进行测量,以观察峰值电流和放电时间的变化。仅通过DMN3027LFG通道RDS(on)电阻(不带50mΩ)放电会产生观察峰值电流的坏情况。请注意以下曲线中的时间尺度不同 - 200μs/div和1 ms/div通道1(C1)为黄色= DMN3027LFG栅极引脚上的电压通道3 (C3)为品红色=电容器组上的电压

通道4(C4)为绿色=来自DMN3027LFG源引脚的电流探头

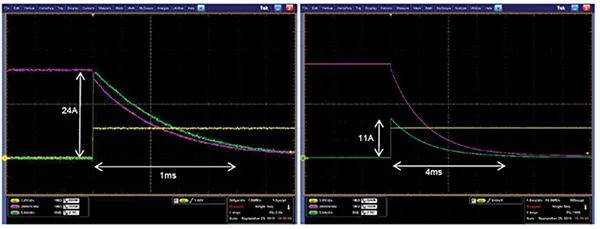

图6:室温测量(约Ta = 20°C)。左曲线= 30 A峰值电流仅通过DMN3027LFG通道电阻放电(200μs/div)右曲线= 12.5通过DMN3027LFG和50mΩ串联电阻放电的峰值电流(1 ms/div)参见图6,图7和图8 - 仅通过DMN3027LFG对13.2 mF电容器组放电,产生的峰值电流从24 A变化到35 A,具体取决于MOSFET RDS(on)的温度响应。通过添加50mΩ串联电阻,可将峰值电流限制在<15 A,温度变化仅限于11 A至14 A.请注意,随着温度升高,峰值电流会相对于RDS(on)增加而下降。

即使温度变化,放电时间至初始1 V充电状态的95%也会在约3至4 ms内发生。这与3 x RC时间常数的预期相同,SPICE建模此电路可以复制类似的结果。模拟一个13.2 mF电容器组在27°C(默认),加入50mΩ串联电阻,然后峰值电流约为13 A,并在3 ms内放电至95%。

图7:高温测量(大约Ta = 70°C)。左曲线= 24仅通过DMN3027LFG通道电阻的峰值电流放电(200μs/div)右曲线= 11通过DMN3027LFG和50mΩ串联电阻(1 ms/div)放电的峰值电流

图8:零下温度测量(约Ta = -20°C)。左曲线= 35仅通过DMN3027LFG通道电阻的峰值电流放电(200μs/div)右曲线= 14通过DMN3027LFG和50mΩ串联电阻(1 ms/div)放电的峰值电流结论

已经证明了一种基于已知RC时间常数对大电容器组放电的安全且简单的方法。这种开放式技术可以根据电容大小进行缩放。选择了以下器件:

Q1 = SOT23中的ZXMP6A13F P沟道MOSFET

Q2 = PowerDI3333-8中的DMN3027LFG N沟道MOSFETR2 = 50mΩ表面贴装电阻能够耗散500 mW。

通过在放电路径中添加50mΩ串联电阻,可以限制峰值放电电流并稳定温度变化。测量结果和模拟结果均吻合良好;让设计师有信心对不同的电容器组尺寸进行建模。

审核编辑:汤梓红

-

运放电路设计注意事项有哪些2024-10-18 2338

-

FPGA的有源电容器放电电路注意事项2023-07-25 681

-

有源放电电路的原理和注意事项2022-04-21 7566

-

技术人员在FPGA设计时需注意什么事项?2021-04-30 1223

-

如何结合晶振的负载电容计算外匹配电容容值以及在晶振振荡电路设计时需注意哪些事项?资料下载2021-04-17 1428

-

FPGA系统中有源电容放电电路设计需注意哪些问题资料下载2021-04-08 988

-

FPGA系统有源电容放电电路怎么避免损坏系统?2019-10-23 1757

-

关于设计FPGA系统中有源电容放电电路的方法和需要注意的问题2019-09-15 1356

-

掌握这些有源电容放电电路设计要领,和“损坏系统”说拜拜!2019-06-09 8007

-

FPGA系统中有源电容放电电路设计需注意哪些问题2019-03-29 3318

-

FPGA的有源电容放电电路考虑2017-05-16 715

-

RS485硬件电路设计中需注意的问题2015-12-21 1112

-

使用CMOS集成电路需注意的几个问题2010-06-05 544

-

集成运放电路中有源负载放大电路的分析与计算方法2010-04-13 12006

全部0条评论

快来发表一下你的评论吧 !