应用笔记——GaN偏置电路设计准则

描述

本文内容翻译自一篇Qorvo的应用笔记,虽然标题是针对GaN偏置电路设计的一些基本准则,但实际上对GaAs也是适用的。基于化合物半导体做射频功放的同学应该都是有概念的,正好这篇文章做了总结,就随手分享共同学习一下。

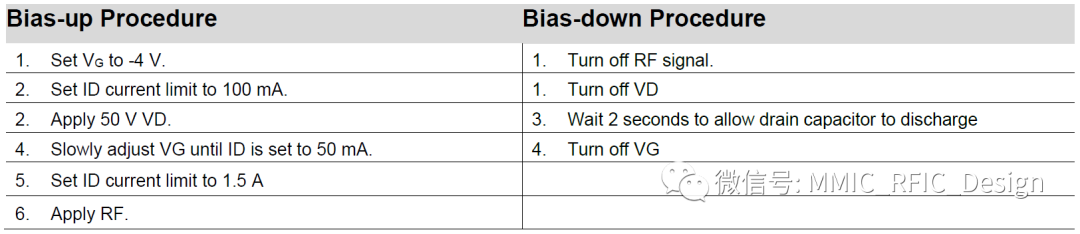

一、上电/下电顺序

基本上GaN大功率射频功放管都是耗尽型的,即零栅压时管子是完全导通状态,需要给栅极加负压才能工作在适当的偏置电流,否则大电流必然造成器件烧毁。因此必须通过硬件或者软件措施严格控制栅压和漏压的上电和下电顺序:

上电顺序:

1、设置栅压VG到-关断电压(具体值视晶体管要求而定);

2、将漏极电流ID限制为静态电流目标值IDQ的两倍左右;

3、漏极电压VD上电;

4、缓慢调整栅极电压VG使漏极电流ID达到静态电流目标值IDQ;

5、将漏极电流ID限制为比大信号工作电流稍大的值;

6、输入射频激励信号。

下电顺序:

1、关闭射频输入信号;

2、关闭漏极电源VD;

3、等两秒以确保漏极的储能电容已完全泄放;

4、关闭栅极电源VG。

二、设置偏置电流

用户都是通过调整栅源电压VGS来调节静态工作电流IDQ的,但由于GaN晶体管的栅压阈值波动较大,这就意味着每一只晶体管的栅压都需要调整才能达到相同的静态偏置电流;反之,如果施加固定栅压,将会导致不同晶体管的静态电流IDQ差异非常大,甚至可能完全没有电流或者很大的电流。过小或过大的电流都会影响放大器的性能,甚至损坏晶体管。

通常静态电流的选取都是参考器件手册,但用户可以以在参数允许的范围内进行微调,以获得期望的增益、效率、线性度、稳定性等。

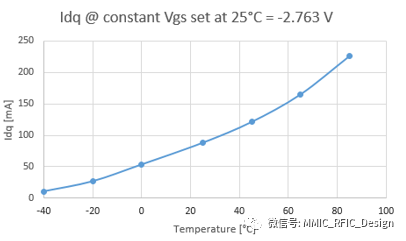

温度会影响晶体管的阈值电压,如果使用固定栅压偏置则会导致电流随温度波动,如下图所示:

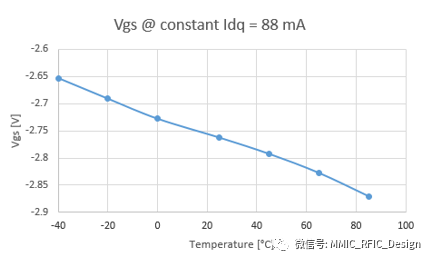

反之如果想偏置电流固定,不随温度变化,则应栅压应该随温度调节,如下图所示:

三、偏置旁路网络设计

为确保器件安全稳定工作,防止意外损坏,偏置网络的设计中有几个方面需要注意。给射频器件馈电的偏置网络必须可靠去耦,旁路电容不仅可以滤除电源的噪声和纹波,同时还充当器件的电荷源,它也降低了电源引线寄生电感的影响。偏置网络会与器件相互作用,从而影响器件的性能和稳定性,因此有时候设计人员还需要通过给旁路电容串联电阻来降低其Q值。

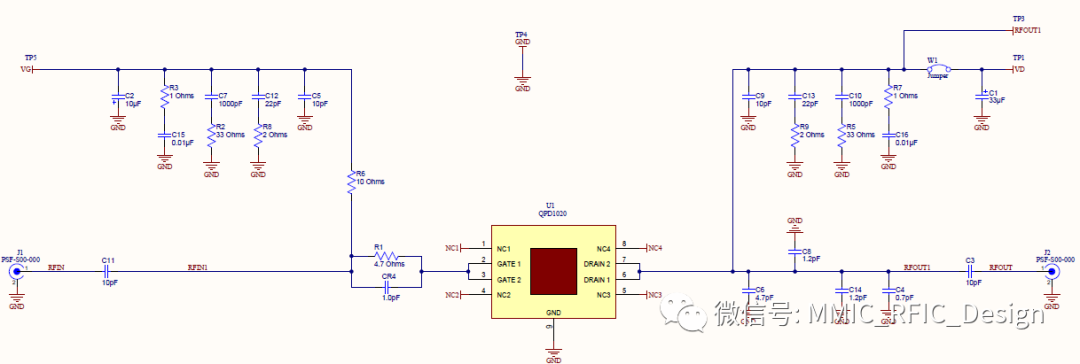

所有的GaN FET分立功放管的栅极都需要串联一个最小5~10Ω的电阻来确保电路的稳定性,但串联电阻一定会对射频性能有不良影响,因此在保证稳定性的前提下串联电阻要尽量小。一个典型的功放偏置电路(QPD1020 2.7-3.1GHz)如图所示,GaN MMIC通常都把栅极串联电阻集成在片内了,因此外部就不再需要串联电阻了。

四、栅极偏置电流设计

电源和偏置电路设计需要与器件的栅极电流兼容,需要既能给栅极提供也能从栅极吸入电流(即电流可正可负)。栅极漏电流的方向是从器件的栅极流出到偏置电路。在较高功率下,由于栅极寄生二极管对射频驱动信号的整流作用,电流会从偏置电路流进器件栅极。栅极漏电流的大小跟器件的尺寸正相关,大功率的管子漏电流比小功率管子更大。仅测试少量器件的漏电流来指导栅极偏置电路是不具有代表性的,应该参考器件手册或者咨询生产商的应用工程师。

如果偏置电路与GaN器件栅极之间有较大的等效电阻,栅极的漏电流就会在电阻上形成较大压降,从而影响栅极偏置电压。当电阻压降很大时,栅压上升导致漏极电流ID显著上升甚至烧毁器件。通常栅极电流在mA量级,假设一个管子的栅极电流是-1mA,串联1kΩ电阻就会产生1V的压降,即栅压比期望值偏高+1V。因此栅极的串联电阻既不能太大(压降)也不能太小(影响射频性能和稳定性)。对于有源偏置电路,还应该考察其自身的稳定性。

正向的栅极电流,通常在高驱动功率时出现,也许要在设计中加以考虑。有源偏置电路必须要提供足够的正向电流有效值,旁路电容可用于在脉冲或调制应用的峰值驱动条件下提供正向电流来源。输入功率越大栅极电流越大,正向偏置电流的最坏情况发生在低温下,因此最低工作温度下、最大输入功率下的最大栅极电流容量应该在有源偏置电路设计中进行考虑。

审核编辑:汤梓红

-

电机驱动电路中的瞬态电压应用笔记2023-11-29 499

-

求助,关于应用笔记CN0343超声波接收电路的计算问题2023-11-16 650

-

电路设计中偏置电流是如何引起误差的呢?2023-10-30 1692

-

DESAT外围电路设计的应用笔记2023-10-09 17816

-

MMIC放大器偏置程序应用笔记2021-06-03 798

-

HMC463LP5偏置序列应用笔记2021-04-30 769

-

SmartMesh IP应用笔记2021-04-21 1292

-

GaN偏置电路设计指南的详细资料说明2020-06-28 1613

-

放大器电路及方案应用笔记全集2018-10-09 4700

-

AD7192的AN1186运用笔记中的EMC电路设计,请问是否适用与AD7172-2的EMC设计,相关滤波元件参数是否需要调整?2018-08-13 2714

-

放大器电路设计2016-06-08 666

-

FIFO中文应用笔记2009-07-28 535

-

利用有源偏置提高立体声性能2009-06-19 832

全部0条评论

快来发表一下你的评论吧 !